Community Health Improvement Plan for Cambria and Somerset Counties, Pennsylvania (2022-2025)

This document outlines the Community Health Improvement Plan (CHIP) for Conemaugh Health System in Cambria and Somerset Counties, Pennsylvania. The plan focuses on addressing significant health needs identified through a Community Health Needs Assessment (CHNA), including mental/behavioral health, a

1 views • 9 slides

Medicaid and CHIP Coverage of New Treatments for Sickle Cell Disease

This communication highlights the Medicaid and Children's Health Insurance Program (CHIP) coverage of new treatments for Sickle Cell Disease (SCD), focusing on the approval of milestone gene therapies, Casgevy and Lyfgenia. It discusses the commitment of CMS to improving healthcare access, quality,

2 views • 13 slides

Building Linux Boot Files with Templates for Multiple SoC Projects

Explore the intricacies of building Linux boot files using templates for various System on Chip (SoC) projects. Learn about Petalinux, Yocto, and the composition of Yocto recipes. Discover the advantages of decoupled layers in a typical Petalinux project and set goals to create your own Yocto layer.

7 views • 28 slides

FELIX Phase II Run 4 and Versal Prime ACAP Device

Explore the advancements in FELIX Phase II Run 4, leveraging Xilinx Versal Prime ACAP Device, showcased at the 3rd CERN System-on-Chip Workshop. Witness massive improvements in trigger rates, data readout rates, and interactions per bunch crossing. Dive into the hardware details and Versal Prime's c

2 views • 36 slides

Automotive LiDAR System-on-Chip Market Stats from 2024-2033

The automotive LiDAR system-on-chip (SoC) market is expected to be valued at $29.3 million in 2024, which is anticipated to grow at a CAGR of 24.30% and reach $207.5 million by 2033.

5 views • 3 slides

Cutting-Edge Fiber to Chip Packaging for Quantum Applications

Cutting-edge research on fiber to chip packaging for quantum applications, showcasing low-loss techniques and advanced photonics devices. The study covers topics such as packaging multiple fibers, fabrication processes, fiber array fusion splicing, and transmission curves for multiple fibers. This w

0 views • 4 slides

Mastering Procedural Writing: Instructions for Chocolate Chip Cookies

This procedure writing guide outlines the essential elements for creating effective instructions, with a focus on how to make chocolate chip cookies. Learn about the importance of clear goals, safety procedures, step-by-step instructions, and key words to use. Follow the provided recipe for a delici

0 views • 7 slides

OACES Chip Seal Workshop Highlights and Insights

Delve into the world of chip seal production and oil rock operations with Billy Scott and Scott Ringham. Learn from their extensive experience at KRC, one of the top aggregate producers in the country. Discover the nuances of different candy bars and the reasons behind their production variations. U

0 views • 20 slides

System on Chip (SoC) Design and Components

Explore the world of System on Chip (SoC) design, components, and working flow. Learn about Intellectual Properties (IP), platform-based design, typical design flows, top-down design approach, and the emerging Electronic System Level (ESL) design flow. Discover the essential components of an SoC, su

0 views • 45 slides

Digital Light Processing (DLP) Projectors

Digital Light Processing (DLP) projectors are display devices based on optical micro-electro-mechanical technology that utilize digital micromirror devices. Developed in 1987 by Larry Hornbeck, these projectors are widely used in classrooms, businesses, digital signs, and even digital cinema project

0 views • 11 slides

Detection of Mutations in EGFR in Circulating Lung Cancer Cells: Study on SARMS Assay and CTC-Chip

This study by Shyamala Maherswaran, Ph.D., and team focuses on characterizing mutations in EGFR in circulating tumor cells using SARMS assay and CTC-chip. The research investigates the effectiveness of these non-invasive methods in analyzing tumors and explores the role of the T790M mutation in resp

0 views • 12 slides

Unified Approach for Performance Evaluation and Debug of System on Chip in Early Design Phase

This presentation discusses the challenges related to system-on-chip design, focusing on bandwidth issues, interconnect design, and DDR efficiency tuning. It explores the evolution of performance evaluation methods and the limitations of existing solutions. The need for a unified approach for early-

0 views • 28 slides

ChIP-seq Data Analysis in Primate iPSCs

Analysis of ChIP-seq data in primate iPSCs reveals insights into regulatory differences, experimental systems, read subsampling, QC analysis, peak classification, and cross-species comparisons for transcriptional regulation studies. Balanced designs and functional validation of iPSCs contribute to a

0 views • 33 slides

Enhancing NAND Flash Memory Chip-Off Forensic Analysis Reliability

This study focuses on improving the reliability of chip-off forensic analysis of NAND flash memory devices. By identifying error sources, quantifying errors, and proposing mitigation processes, the research emphasizes the impact of storage time and heat on errors introduced in chip-off analysis. The

0 views • 26 slides

Beam Test Results with BCM and TowerJazz CMOS F9 Weekly

Bojan Hiti from Jožef Stefan Institute in Ljubljana, Slovenia conducted a series of tests involving BCM prototype readout chip and TowerJazz CMOS at CERN SPS H6. The experiments included beam tracking, analog readout, and chip configurations for the ATLAS Beam Condition Monitor upgrade. Detailed re

0 views • 19 slides

Enhancing Off-chip Bandwidth Utilization for Improved System Performance

Efficiently coordinating off-chip read/write bandwidth through the Bandwidth-aware LLC proposal yields a 12% performance improvement in an 8-core system across multiple workloads. This approach optimizes DRAM read latency, surpassing existing policies and filling performance gaps while confirming lo

1 views • 36 slides

A Model for Application Slowdown Estimation in On-Chip Networks

Problem of inter-application interference in on-chip networks in multicore processors due to NoC contention causes unfair slowdowns. The goal is to estimate NoC-level slowdowns in runtime and improve system fairness and performance. The approach includes NoC Application Slowdown Model (NAS) and Fair

0 views • 25 slides

A Comprehensive Guide to Common Chip Seal Oils

Explore various types of chip seal oils used for road surfacing, including CRS-2P, CRS-3P, PMCRS-2H, HFE-100-S, HFRS-P2, AC-15P, HFE-150, RS-LTP, and more. Learn about their applications, compositions, and ideal usage conditions such as temperature requirements and traffic intensity. Discover hot ap

0 views • 4 slides

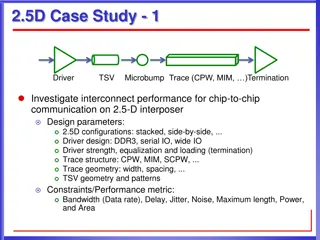

Investigating Chip-to-Chip Communication Performance on 2.5D Interposer

Investigate the performance of chip-to-chip communication on a 2.5D interposer by analyzing interconnect parameters such as configurations, driver design, trace structure, TSV geometry, and channel modeling. Explore methods like SPICE simulation and MATLAB GUI for performance estimation and optimiza

0 views • 18 slides

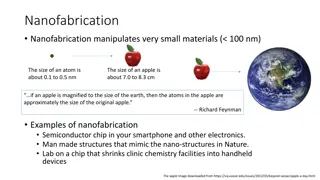

Nanofabrication: Revolutionizing Technology at the Nano Scale

Nanofabrication is a cutting-edge technology that manipulates materials on a minuscule scale, smaller than 100 nm. This process enables the creation of intricate structures like semiconductor chips, lab-on-a-chip devices, and mimicking natural nanostructures. With examples like the Apple A7 chip con

0 views • 11 slides

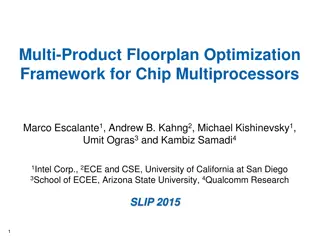

Multi-Product Chip Multiprocessor Floorplan Optimization Framework

This research discusses a framework for optimizing floorplans of chip multiprocessors, considering multiple products with varying requirements. The study emphasizes the interdependency between interconnection networks and floorplans, impacting power, performance, and area. By making floorplans chopp

0 views • 31 slides

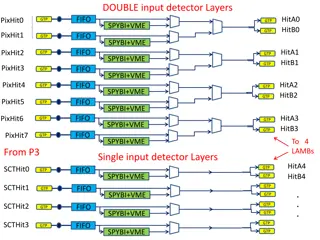

Control Chip Functionality Overview in Particle Detection Systems

This detailed content discusses the functionality of the control chip in particle detection systems. It covers topics such as error monitoring, logic generation, input/output communication, and more. The control chip plays a crucial role in handling errors, generating actions based on severity, and

0 views • 6 slides

Standard G6PD Test Quality Assurance Guide

This comprehensive guide covers the quality assurance features of the SD Biosensor STANDARD G6PD Test, including instructions on checking the strip, code chip, and control reagents. Learn how to use the check strip, change the code chip, and utilize quality control reagents for accurate testing resu

0 views • 14 slides

Memory Benchmarking of ARM-Based Systems-on-Chip

This study evaluates memory performance in ARM-based Systems-on-Chip (SoCs) for Data Stream Computing (DSC). It discusses key challenges such as energy efficiency, storage capacity, costs, and memory latencies. The relevance of memory performance in military-led research is highlighted, along with t

0 views • 40 slides

High-Speed Hit Decoder Development for RD53B Chip

Development of a high-speed hit decoder for the RD53B chip by Donavan Erickson from MSEE ACME Lab, focusing on data streams, hitmap encoding, ROM splitting, decode engine building, and more. The process involves encoding methods, ROM setup with borrowed software look-up tables, and buffer systems fo

0 views • 33 slides

Medicaid and CHIP Payment Error Rate Measurement (PERM) Program Overview

The Payment Error Rate Measurement (PERM) program is an initiative by CMS to estimate improper payments in Medicaid and CHIP annually. Sampling is used to measure the true improper payment rate. The program operates under final regulations, reviewing payments made in Reporting Year 2021. The goal is

0 views • 56 slides

Networks-on-Chip (NoC) in Computer Engineering

Networks-on-Chip (NoC) represent a packet-switched communication network designed for on-chip systems, allowing efficient data routing via switches and interconnection links. NoCs aim to apply large-scale network concepts in embedded systems, offering scalability, flexible QoS guarantees, higher ban

0 views • 29 slides

SLAC CRYO: Waveform Digitizer/Serializer for Cryogenic TPC Experiments

SLAC is developing the CRYO ASIC, a high-performance waveform digitizer and serializer optimized for cryogenic operation in experiments like DUNE. The CRYO ASIC offers advanced features such as single-chip integration, programmability, on-chip regulation, and design for reliability. Operating in a 1

0 views • 23 slides

Network-on-Chip Communication and Optimization

Network-on-Chip (NoC) is essential for communication among system elements in large systems. It involves topology, flow control, congestion handling, and routing optimization techniques like virtual channels. Learn about the key aspects and challenges in designing efficient NoCs.

0 views • 26 slides

Plant Bioinformatics Studies on ChIP-Seq Data Analysis

Plant bioinformatics researchers conducted experimental analyses and mapped gene regulatory networks using ChIP-Seq data. The studies involved exploring gene expression, regulatory interactions, and transcription factor binding sites. Techniques such as peak calling, motif finding, and peak annotati

0 views • 19 slides

Public Benefits Updates in Texas Amid COVID-19

During the COVID-19 pandemic, Texas has implemented various measures to support residents. These include coverage for COVID-19 testing under Medicaid and CHIP, waived co-payments for CHIP services, extensions for SNAP/TANF/Medicaid recertifications, waiver of work requirements, and online purchasing

0 views • 15 slides

Challenges and Progress in Children's Health Coverage

The data presented highlights the evolution of children's health coverage in the United States, focusing on uninsured children and enrollment trends in programs like Medicaid and CHIP. Despite significant gains since the enactment of CHIP in 1997, many children remain uninsured due to various factor

0 views • 9 slides

Best Chip Repair Services in Burnaby

If you want the Best Chip Repair Services in Burnaby, visit Apac Auto Glass. They specialize in Windshield Replacement, Chip Repair, ICBC Glass Repair, Door glass repair, and more. Their business is not just about excellence; it's a reflection of the

1 views • 6 slides

Cutting-Edge Chip Development in 65nm

Delve into the world of advanced chip development with a focus on layout experience in 65nm technology. Explore different solutions, testing scenarios, and the integration of analogue buffers to enhance the understanding of analogue front-end technologies. Get insights into upcoming projects, strate

0 views • 10 slides

Performance Evaluation of On-Chip Sensor Network in MPSoC

In this study, the performance evaluation of on-chip sensor networks in Multi-Processor System-on-Chip (MPSoC) architectures is explored. Limitations of bus interconnects are discussed, and the concept of Network-on-Chip (NoC) as a solution is introduced. The integration of sensors in MPSoC design i

0 views • 25 slides

CMOS Chip Testing: Need, Principles, Strategies

This content delves into the critical aspects of CMOS chip testing, highlighting the necessity, testing principles, design strategies, and techniques at the chip and system levels. It also explores layout design for enhanced testability, logic verification, silicon debugging, manufacturing testing,

0 views • 22 slides

Hit rate distribution

The purpose of this project is to optimize the hit rate distribution for Au+Au 200GeV run by analyzing chip-by-chip and half ladder-by-half ladder hit rates. Issues such as hot channels and low efficiency due to dead pixel areas are addressed, ensuring stable hit rates for VTXP. Images provide insig

0 views • 11 slides

Efficient Timing Channel Protection for On-Chip Networks

On-Chip Networks (OCNs) are shared resources in future large-scale multi-cores, leading to multiple applications/virtual machines coexisting. This study delves into the issue of timing channels causing interference due to shared NoCs, with a focus on security assurance systems. The research highligh

0 views • 25 slides

Belle II SVD Silicon Sensors & Front-End Readout

This content discusses the components, requirements, and technology used in the Belle II Silicon Vertex Detector (SVD), including details about the silicon sensors, front-end readout ASIC (such as the APV25 chip), and the chip-on-sensor concept.

0 views • 17 slides

and the Role of Medicaid and CHIP

Role of Medicaid and CHIP in providing health coverage for Texas women, including coverage trends, Medicaid recipients, eligibility criteria, and populations not covered. Understand the impact on maternal health and access to care.

0 views • 21 slides