Enhancing NAND Flash Memory Chip-Off Forensic Analysis Reliability

This study focuses on improving the reliability of chip-off forensic analysis of NAND flash memory devices. By identifying error sources, quantifying errors, and proposing mitigation processes, the research emphasizes the impact of storage time and heat on errors introduced in chip-off analysis. The study also introduces the effectiveness of a read-retry mechanism in reducing errors. The paper delves into the operation of MLC NAND flash memory cells, error distributions, and retention errors, providing insights to enhance the reliability of chip-off analysis.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Improving the Reliability of Chip-Off Forensic Analysis of NAND Flash Memory Devices Aya Fukami, Saugata Ghose, Yixin Luo, Yu Cai, Onur Mutlu 1

Brief Summary of the Paper Brief Summary of the Paper Our Goal: Identify error sources in NAND flash memory during chip-off Quantify errors in NAND flash memory introduced in chip-off Identify a mitigation process to reduce errors introduced during chip-off analysis Our findings: Long storage time of devices increases errors in NAND flash memory Heat in chip-off increases uncorrectable errors Read-retry mechanism can reduce errors introduced during chip-off 2

Talk Outline Talk Outline Background Basic operation of NAND flash memory Testing Methodology and Experimental Results Retention error Errors introduced by heat How to Improve Reliability of Chip-off Analysis Read-retry operation 3

Talk Outline Talk Outline Background Basic operation of NAND flash memory Testing Methodology and Experimental Results Retention error Errors introduced by heat How to Improve Reliability of Chip-off Analysis Read-retry operation 4

MLC NAND Flash Memory Cell Operation Control Gate Floating Gate Oxide Source Drain Substrate 00 01 10 Stored data: 11 Threshold voltage Current[A] Voltage[V] Amount of charge = Threshold voltage of the cell = Stored data value 5

MLC NAND Cell Vth Distribution Read voltage Number of cells 10 10 11 11 01 01 00 00 Threshold Voltage Threshold voltages need to be between each read voltage 6

Retention Error on MLC NAND Flash Cell Control Gate Floating Gate Oxide Source Drain Substrate Read voltage Number of cells 10 10 11 11 01 01 00 00 Threshold Voltage Error! Error! Error! Charge leakage over time causes threshold voltage shifts Data error in result is called retention error 7

NAND Flash Cell Degradation Oxide Erasing Programming Degraded Cell Number of cells 10 10 00 00 Threshold Voltage Error! Repeated programming and erasing (P/E cycle) accelerates charge leakage 8

NAND Flash Error Sources During Chip-off Heat guns or electrical rework machines De-solder NAND flash memory chips with heat Required temperature and duration: 250 C (482 F), ~2 minutes High temperature accelerates charge leakage 9

Error Correction Codes (ECC) Flash memory controllers store ECC codewords to correct errors in data Typical correction capability for recent chip: 40 bits correction capability per 1KB Errors exceeding ECC correction capability: uncorrectable errors 10

Talk Outline Background Basic operation of NAND flash memory Testing Methodology and Experimental Results Retention error Errors introduced by heat How to Improve Reliability of Chip-off Analysis Read-retry operation 11

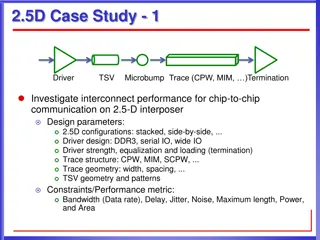

Testing Environment Test chips: New 2y-nm NAND flash memory chips from two different vendors (hereafter called Chip A and Chip B) Controller: Altera DE0 FPGA 12

Testing Methodology: Retention Error Evaluation Repeated programming/erasing cycles (P/E cycles) 10, 300, 1000, 2500, and 4000 cycles Raw bit error rate (RBER) measurement at multiple retention age (=wait time after programming) Day 0 and 1, Week 1, 2, 3 and 4 13

Experimental Result: Experimental Result: Retention Error: Chip A Retention Error: Chip A 10-2 ECC Error Correction Capability Raw Bit Error Rate Day 0 Day 1 Week 1 Week 4 10-3 18 12 10-4 10-5 10 100 1K P/E Cycle Count RBER grows as P/E cycle count and retention age increase 14

Experimental Result: Experimental Result: Retention Error: Chip B Retention Error: Chip B 10-2 ECC Error Correction Capability Raw Bit Error Rate Day 0 Day 1 Week 1 Week 4 10-3 4 10-4 3 10-5 10 100 P/E Cycle Count 1K RBER grows as P/E cycle count and retention age increase 15

Testing Methodology: Testing Methodology: Thermal Effect Evaluation Thermal Effect Evaluation Baking target chips at 250 C for 2 mins at different retention age (simulating chip-off procedures) 1 Week 4 Weeks Raw bit error rate (RBER) measurement after baking 16

Experimental Result: Experimental Result: Errors Errors Introduced by Introduced by Heat 100 Heat (Chip A) (Chip A) Week 1, Before Baking Week 4, Before Baking Week 1, After Baking Week 4, After Baking Raw Bit Error Rate 10-1 10-2 ECC Error Correction Capability 51 10-3 33 10-4 10-5 10 100 P/E Cycle Count 1K Heat introduces errors more than ECC can correct 17

Experimental Result: Experimental Result: Errors Errors Introduced by Introduced by Heat 100 Heat (Chip (Chip B) B) Week 1, Before Baking Week 4, Before Baking 10-1 Week 1, After Baking Raw Bit Error Rate Week 4, After Baking 10-2 ECC Error Correction Capability 37 10-3 51x 10-4 10-5 10 100 1K P/E Cycle Count Heat introduces errors more than ECC can correct 18

Experimental Result: Experimental Result: Uncorrectable Errors after Baking Uncorrectable Errors after Baking Fraction of pages that contains uncorrectable errors (P/E cycle=300) Retention Period before Baking 1 Week 4 Weeks Chip A Chip B 29.1% 84.2% 78.1% 83.6% Heat introduces uncorrectable errors even when the chip has been only lightly used 19

Talk Outline Talk Outline Background Basic operation of NAND flash memory Testing Methodology and Experimental Results Retention error Errors introduced by heat How to Improve Reliability of Chip-off Analysis Read-retry operation 20

Read Read- -Retry Retry Mechanism Mechanism Default read voltage Shifted read voltage Shifted read voltage Number of cells 11 11 01 01 Threshold Voltage 01 11 01 11 Read-retry mechanism shifts the read voltage to reduce errors caused by threshold voltage shifts 21

Testing Methodology: Testing Methodology: Read Read- -Retry Evaluation Retry Evaluation Read-Retry command found on chip B Implemented as a vendor specific command Read operation with read-retry Evaluation of 2 modes (mode A and B) 22

Experimental Result: Error Reduction with Read-Retry 10-1 Default Read Read-Retry Mode A Read-Retry Mode B (4 weeks after programming) Raw Bit Error Rate -94.6% 10-2 ECC Error Correction Capability -88.6% 10-3 10-4 10 100 P/E Cycle Count 1K Read-retry can reduce errors introduced by thermal-based chip-off procedure 23

Uncorrectable Uncorrectable Error Reduction Error Reduction by Read by Read- -Retry Retry Fraction of pages that contains uncorrectable errors (Chip B, after baking) P/E Cycle Count 300 83.6% 0% 0% Read Mode 1000 99.7% 12.1% 0% Default Read-Retry A Read-Retry B Read-retry can reduce errors introduced by thermal-based chip-off procedure 24

Conclusions and Recommendations Conclusions and Recommendations Wait time increases errors Conduct data extraction at the earliest possible time after receiving a device Heat introduces uncorrectable errors Keep the temperature as low as possible Read-retry can reduce errors Use read-retry after chip-off when available 25

Improving the Reliability of Chip-Off Forensic Analysis of NAND Flash Memory Devices Aya Fukami, Saugata Ghose, Yixin Luo, Yu Cai, Onur Mutlu 26