Understanding the Fetch-Decode-Execute Cycle in Computer Processing

Exploring the fundamental process of executing a program in a computer through the fetch-decode-execute cycle. This cycle involves loading programs and data into the computer's memory, fetching and executing instructions sequentially, and managing memory operations effectively. The interaction between the processor, memory, and control unit is crucial for program execution.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

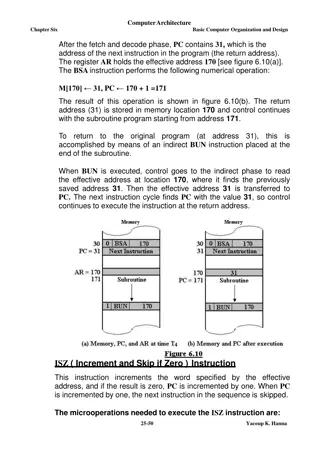

The Fetch-Execute Cycle To execute a program you must first load the program and any relevant data in to the computer s memory (RAM) from disk. The program and data is stored in memory until needed by the processor (the stored program concept). MainMemory 10101010 11101000 00110001 10100010 11100000 00001000 10100010 11110011 11111000 00110000 Address 11000000 00001001 11000000 00001001 11000000 00000111 11000000 00000110 11000000 00000101 11000000 00000100 11000000 00000011 11000000 00000010 11000000 00000001 11000000 00000000 Processor

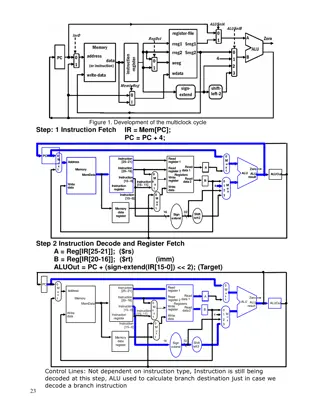

The Fetch-ExecuteCycle A program may contain thousands of instructions but the processor can only execute one instruction at a time. The first instruction is fetched from memory in to the processor where it is decoded and executed. Then the second instruction is fetched and then executed and so on until the program ends. This is known as the FETCH EXECUTE CYCLE . Processor LDA #B5

Memory ReadOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 1. The processor sets up the address bus with the required memory address by placing it in the MAR

Memory ReadOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 2. The control unit activates the read line on the control bus

Memory ReadOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers 11110011 DataBus Memory Data Register Control Unit ALU ControlBus 3. The address bus opens the relevant memory location at that address

Memory ReadOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers 11110011 DataBus Memory Data Register Control Unit ALU ControlBus 4. The contents of the memory location are released, sent along the data bus and into the MDR

Memory ReadOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 5. The data is then decoded and executed

Memory WriteOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 1. The processor sets up the address bus with the required memory address by placing it in the MAR

Memory WriteOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 2. The processor sets up the data bus with the value to be stored in memory by placing it in the MDR

Memory WriteOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 3. The control unit activates the write line on the control bus

Memory WriteOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers DataBus Memory Data Register Control Unit ALU ControlBus 4. The address bus opens the relevant memory location at that address

Memory WriteOperation Processor MainMemory Address 00001001 00001000 00000111 00000110 00000101 00000100 00000011 00000010 00000001 00000000 Memory Address Register AddressBus Other Registers 11000111 DataBus Memory Data Register Control Unit ALU ControlBus 5. The contents of the memory data register are released, sent along the data bus and into the memory location