Advanced Operation of TPS548D22 with OVP Functionality

This detailed content presents the operational intricacies of TPS548D22 with OVP function, including setup specifications, fault-triggered actions, shutdown mechanisms, threshold behaviors, and minimum on-time considerations. The process involves orchestrated switching between FETs to regulate VOUT levels, respond to faults like overvoltage and undervoltage, and manage inductor current during various conditions. Additionally, it covers forced overvoltage scenarios, resonant LC network dissipation, and control of off-time durations based on specific thresholds. The comprehensive explanation offers valuable insights into the device's advanced functionality.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

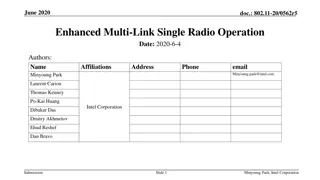

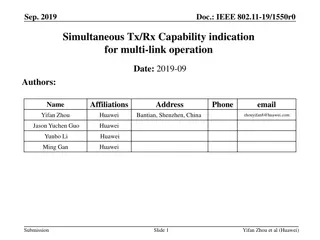

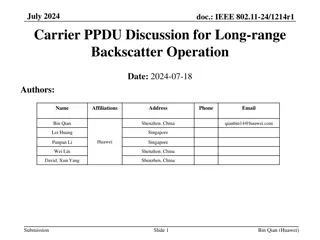

TPS548D22 OVP Operation Amnat Yakamna September 12, 2018 TI Information Selective Disclosure

1.0VOUT Setup VIN=VDD=12V VOUT=1.0V FREQUENCY=650Khz Inductor=0.33 H Iccmax=25A OCL=32A MODE=D-CAP3_DCM Ramp Generator s Resistor= (FSW=650Khz=Rx1)

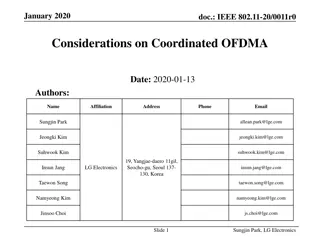

OVP Operation After OV fault triggers, LS FET turns on to pull down VOUT until negative OC is triggered. Then LS FET turns off and HS FET turns on for a Ton period. Afterwards, HS FET turns off and LS FET turns on again until negative OC is triggered again. The negative OC induced switching process repeats again and again in order to regulate the VOUT pull down current. After VOUT is close to being completely discharged, negative OC won t get triggered anymore and so LS FET stays turned on. To trigger UV fault after OV fault induced VOUT discharge, FB voltage must drop below UV threshold (68% of the target reference voltage). The UVP comparator output goes high and an internal UVP delay counter begins counting. After 1ms, the device latches OFF both high-side and low-side MOSFETs drivers. 3

OVP Operation Shutdown, IOUT=40A ~1ms UVP delay, LS FET=ON and HS FET=OFF Device latches off the LS and HS FET.

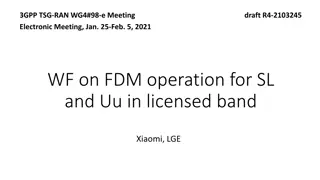

OVP Operation OV Threshold. Shutdown, IOUT=40A UVP Threshold. LS FET turns on to pull down VOUT until negative OC is triggered. Inductor current became less negative and more positive. The energy stored in the inductor has to be dissipated through the LC network. The LC network is highly resonant and underdamped so resulting current looks quite oscillatory.

OVP Operation OV Threshold. Forced OV condition by the function generator pulsed through a diode for ~5us. The set voltage is at 20% above the reference voltage.

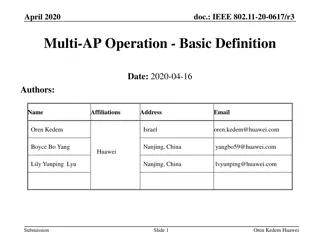

OVP Operation Switch node Minimum on-time Negative OC threshold The different off-time durations controlled by the negative OC threshold and the VOUT decreasing (V=L*di/dt).