Universal Two-Qubit Computational Register for Trapped Ion Quantum Processors

Universal two-qubit computational register for trapped ion quantum processors, including state preparation, gates, and benchmarking. The experimental setup and results are discussed.

0 views • 14 slides

Towards Single-Event Upset Detection in Hardware Secure RISC-V Processors

This research focuses on detecting single-event upsets (SEUs) in hardware-secure RISC-V processors in radiation environments, such as high-energy physics and space applications. Motivated by the potential data errors, unpredictable behavior, or crashes caused by SEUs, the study explores fault inject

5 views • 17 slides

Superscalar Processors in Processor Design

Explore the concept of superscalar processors in processor design, including the ability to execute instructions independently and concurrently. Learn about the difference between superscalar and superpipelined approaches, instruction-level parallelism, and the limitations and design issues involved

1 views • 55 slides

Computer Architecture: A Comprehensive Overview by Prof. Dr. Nizamettin AYDIN

Explore the realm of computer architecture through the expertise of Prof. Dr. Nizamettin AYDIN, covering topics like RISC characteristics, major advances in computers, comparison of processors, and the driving force for CISC. Delve into the evolution of processors, register optimization, and the tra

0 views • 42 slides

Introduction to Intel Assembly Language for x86 Processors

Intel Assembly Language is a low-level programming language designed for Intel 8086 processors and their successors. It features a CISC instruction set, special purpose registers, memory-register operations, and various addressing modes. The language employs mnemonics to represent instructions, with

3 views • 12 slides

Shared Memory Systems in Computer Architecture

Shared memory systems in computer architecture allow all processors to have direct access to common physical memory, enabling efficient data sharing and communication among processors. These systems consist of a global address space accessible by all processors, facilitating parallel processing but

2 views • 19 slides

Computer System Architectures

Computer systems can be categorized into single-processor and multiprocessor systems. Single-processor systems have one main CPU but may also contain special-purpose processors. Multiprocessor systems have multiple processors that share resources, offering advantages like increased throughput, econo

2 views • 25 slides

PowerPC Architecture Overview and Evolution

PowerPC is a RISC instruction set architecture developed by IBM in collaboration with Apple and Motorola in the early 1990s. It is based on IBM's POWER architecture, offering both 32-bit and 64-bit processors popular in embedded systems. The architecture emphasizes a reduced set of pipelined instruc

3 views • 13 slides

Contrasting RISC and CISC Architectures

Contrasting RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing) architectures, the images and descriptions elaborate on their advantages and disadvantages, with a focus on multiplying two numbers in memory using a CISC approach. CISC processors aim to complete tasks

1 views • 35 slides

ARM RISC Design Philosophy and Its Impact

Delve into the world of ARM processors, exploring the RISC design philosophy that underpins their efficiency and widespread application. Learn about key principles, compare RISC with CISC, and discover how ARM's simplicity, orthogonality, and efficient architecture contribute to its dominance in mob

0 views • 12 slides

Design and Implementation of Shifters in ALU for Single-Cycle Processors

The detailed discussion covers the construction of a multifunction Arithmetic Logic Unit (ALU) for computer processors, specifically focusing on the design and implementation of shifters. Shift operations such as SLL, SRL, SRA, and ROR are explained, with insights into shifting processes and data ex

1 views • 5 slides

k-Ary Search on Modern Processors

The presentation discusses the importance of searching operations in computer science, focusing on different types of searches such as point queries, nearest-neighbor key queries, and range queries. It explores search algorithms including linear search, hash-based search, tree-based search, and sort

1 views • 18 slides

Enhancing I/O Performance on SMT Processors in Cloud Environments

Improving I/O performance and efficiency on Simultaneous Multi-Threading (SMT) processors in virtualized clouds is crucial for maximizing system throughput and resource utilization. The vSMT-IO approach focuses on efficiently scheduling I/O workloads on SMT CPUs by making them "dormant" on hardware

0 views • 31 slides

Accelerating Lemma Learning Using Joins in Satisfiability Modulo Theories

Explore the use of joins in accelerating lemma learning within the context of Satisfiability Modulo Theories (SMT). The study covers various SMT applications at Microsoft and delves into the development of the Z3 solver. Key topics include theories, arithmetic operations, array theory, uninterpreted

0 views • 25 slides

Dynamic Load Balancing on Graphics Processors: A Detailed Study

In this comprehensive study by Daniel Cederman and Philippas Tsigas from Chalmers University of Technology, the focus is on dynamic load balancing on graphics processors. The research delves into the motivation, methods, experimental evaluations, and conclusions related to this critical area. It cov

0 views • 57 slides

Scaling Multi-Core Network Processors Without the Reordering Bottleneck

This study discusses the challenges in packet ordering within parallel network processors and proposes solutions to reduce reordering delay. Various approaches such as static mapping, single SN approach, and per-flow sequencing are explored to optimize processing efficiency in multi-core NP architec

0 views • 22 slides

- Exceptions in Modern High-Performance Processors

- Overview of exceptions in pipeline processors, including conditions halting normal operation, handling techniques, and example scenarios triggering exception detection during fetch and memory stages. Emphasis on maintaining exception ordering and performance analysis in out-of-order execution proc

3 views • 28 slides

Interrupt Processing Sequence in X86 Processors

X86 processors have 256 software interrupts, functioning similarly to a CALL instruction. When an INT n instruction is executed, the processor follows a sequence involving pushing the flag register, clearing flags, finding the correct ISR address, and transferring CPU control. Special interrupts lik

1 views • 10 slides

Should Ghana Provide Discounts on Cocoa Beans for Local Processors? A Case Study

Ghana's cocoa sector plays a significant role in the country's economy, yet less than 25% of cocoa beans are processed locally, limiting its market share. This case study explores the impact of local processing on Ghana's cocoa industry and discusses the dilemma of value addition. The question of wh

0 views • 14 slides

Constructive Computer Architecture: Multistage Pipelined Processors

Explore the concepts of multistage pipelined processors and modular refinement in computer architecture as discussed by Arvind and his team at the Computer Science & Artificial Intelligence Lab, Massachusetts Institute of Technology. The content delves into the design and implementation of a 3-stage

0 views • 28 slides

Data Hazards in Pipelined Processors: Understanding and Mitigation

Explore the concept of data hazards in pipelined processors, focusing on read-after-write (RAW) hazards and their impact on pipeline performance. Learn strategies to mitigate data hazards, such as using a scoreboard to track instructions and stall the Fetch stage when necessary. Discover how adjusti

0 views • 23 slides

Instruction Flow Techniques in High-IPC Processors

Explore the intricate processes involved in optimizing instruction flow within high-IPC processors, tackling challenges such as control dependences, branch speculation, and branch direction prediction. Learn about the goals, impediments, branch types, and implementations that shape the efficient exe

0 views • 80 slides

Leveraging Graphics Processors for Accelerating Sonar Imaging via Backpropagation

Utilizing graphics processors to enhance synthetic aperture sonar imaging through backpropagation is a key focus in high-performance embedded computing workshops. The backpropagation process involves transmitting sonar pulses, capturing returns, and reconstructing images based on recorded samples. T

0 views • 18 slides

Z3: An Efficient SMT Solver

Z3 is an efficient Satisfiability Modulo Theories (SMT) solver that integrates various decision procedures for program analysis, verification, and test case generation. It supports linear arithmetic, bit-vectors, uninterpreted functions, quantifiers, and offers an extensive API for different program

0 views • 16 slides

SMT-LIB: The Satisfiability Modulo Theories Library Overview

The Satisfiability Modulo Theories Library (SMT-LIB) is a comprehensive tool for formal reasoning in various supported theories such as arrays, bit vectors, and integer and real arithmetic. It provides a wide range of supported sublogics for precise specifications and verifications. Moonzoo Kim, fro

0 views • 14 slides

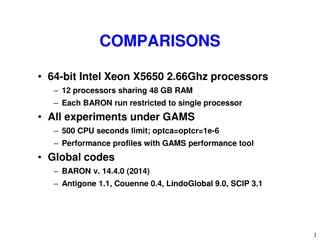

Performance Comparison of Optimization Solvers on Intel Xeon X5650 Processors

Experiment results comparing the performance of optimization solvers (BARON, Antigone, LindoGlobal, SCIP, Couenne) on Intel Xeon X5650 2.66Ghz processors with 48GB RAM. The study includes 369 NLPs from various libraries and an aggregate analysis of 1740 NLPs and MINLPs. Performance profiles generate

1 views • 6 slides

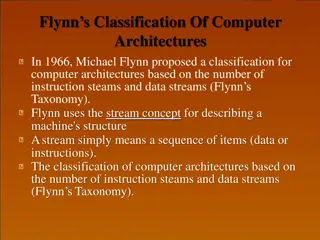

Flynn's Taxonomy: Classification of Computer Architectures

Michael Flynn's 1966 classification divides computer architectures into SISD, SIMD, MISD, and MIMD based on the number of instruction streams and data streams. SISD corresponds to traditional single-processor systems, SIMD involves multiple processors handling different data streams, MISD has multip

0 views • 10 slides

Introduction to DSP Processors and Applications

DSP processors play a crucial role in various applications such as communications, audio and video processing, graphics, navigation, radar, and more. These processors are designed to efficiently handle repetitive numerical calculations, maintain numeric fidelity, and provide real-time processing cap

0 views • 43 slides

Verification and Synthesis using SMT Solvers

This paper explores the use of SMT solvers for program verification and synthesis, focusing on discovering invariants with arbitrary quantification and boolean structure. It delves into proving programs correct by inferring program states and discusses tasks like sortedness and permutation. The auth

0 views • 18 slides

Scheme Monitoring Tool for Pipe Water Supply Schemes in Assam

Providing safe drinking water to rural households is a key goal of the Jal Jeevan Mission in Assam. The Scheme Monitoring Tool (SMT) simplifies the tracking and monitoring of Pipe Water Supply Schemes, ensuring effective project implementation and timely completion. Developed to streamline the daily

0 views • 9 slides

Advanced Processors

Delve into the world of DSP processors and hardware architectures for signal processing, exploring topics such as Harvard Architecture, pipelining, and specialized instructions like MAC. Discover the simplified architecture of standard microprocessors and the need for DSP architecture with elements

0 views • 59 slides

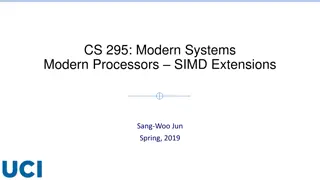

CS 295: Modern Systems Modern Processors - SIMD Extensions

This content covers topics on modern processors, including SIMD extensions, performance improvements, Flynn Taxonomy Recap, Intel SIMD extensions, registers, SSE/AVX data types, and Sandy Bridge Microarchitecture. It provides insights into transparent performance improvements, explicit performance e

0 views • 34 slides

Reviewed Updates and System Upgrades in RMS and SMT

This update covers reviewed revisions to AMWG procedures and TDSP AMS data practices matrix, system upgrades, hardware failures analyzed for root cause, planned release for SMT, Help Desk calls and tickets status, active AEPN, CNP, Oncor data agreements, and upcoming meetings via WebEx. Find out mor

0 views • 7 slides

Understanding Superscalar vs. VLIW Processors: Architecture and Differences

Explore the world of Superscalar and VLIW processors, two advanced technologies designed to enhance performance by executing multiple instructions in parallel. Delve into the architectures, differences, and operational principles of these processors to gain insights into their unique capabilities an

0 views • 22 slides

Understanding Processor Technology and Memory Hierarchy Advancements

Explore advanced processor technologies including superscalar and vector processors, memory hierarchy concepts, virtual memory implementation, shared memory organizations, bus systems, and pipeline design. Delve into the design space of processors, comparing CISC and RISC architectures, and discover

1 views • 30 slides

Advanced Program Synthesis Techniques Using SAT/SMT Solvers

Explore advanced topics in program synthesis through SAT/SMT solvers, including sketching examples, swapping techniques, and SyGus with Syntax Guided Synthesis. Understand constraint systems, computational problems, and theory fixes for function synthesis. Dive into SyGus examples for theory QF-LIA

1 views • 18 slides

Evolution of Intel x86 Processors at Carnegie Mellon

Explore the evolution of Intel x86 processors at Carnegie Mellon, from the introduction of the 8086 in 1978 to the latest Core i7 Broadwell models in 2015. Learn about the milestones, features, and advancements in machine-level programming, assembly basics, and the dominance of Intel processors in t

0 views • 44 slides

Account Management and SMT Services Overview

Explore key aspects of 3rd party registration, account management, and SMT services including data timelines, service availability, anomalies, account statistics, and ODR details. Gain insights into service performance and trends in relation to account management processes.

0 views • 5 slides

Soft Vector Processors and Streaming Pipelines in Action

Explore the implementation of soft vector processors with streaming pipelines, addressing data parallel problems on FPGAs, overlays, processors, and examples like the N-Body Problem. Dive into custom vector instructions, VectorBlox MXP, CVI complications, and heterogeneous lanes for efficient proces

0 views • 21 slides

Godson Processors: Evolution and Features

Discover the evolution of Godson processors, from the inception of BLX IC Design Corporation to the latest Godson-3B1500 model. Explore the key features, architectures, and advancements in this comprehensive overview of Godson processors.

0 views • 17 slides