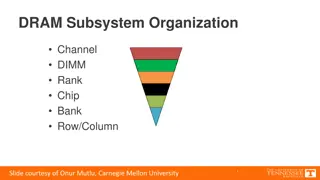

The Organization of DRAM Subsystem Components

Explore the intricate structure of the DRAM subsystem, including memory channels, DIMMs, ranks, chips, banks, and rows/columns. Delve into the breakdown of DIMMs, ranks, chips, and banks to comprehend the design and functioning of DRAM memory systems. Gain insights into address decoding, row/column

0 views • 16 slides

Computer Architecture: Understanding SRAM and DRAM Memory Technologies

In the field of computer architecture, SRAM and DRAM are two prevalent memory technologies with distinct characteristics. SRAM retains data as long as power is present, while DRAM is dynamic and requires data refreshing. SRAM is built with high-speed CMOS technology, whereas DRAM is more dense and b

4 views • 38 slides

High-Throughput True Random Number Generation Using QUAC-TRNG

DRAM-based QUAC-TRNG provides high-throughput and low-latency true random number generation by utilizing commodity DRAM devices. By employing Quadruple Row Activation (QUAC), this method outperforms existing TRNGs, achieving a 15.08x improvement in throughput and passing all 15 NIST randomness tests

1 views • 10 slides

SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Processing Using DRAM

SIMDRAM introduces a novel framework for efficient computation in DRAM, aiming to overcome data movement bottlenecks. It emphasizes Processing-in-Memory (PIM) and Processing-using-Memory (PuM) paradigms to enhance processing capabilities within DRAM while minimizing architectural changes. The motiva

4 views • 14 slides

Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the n

0 views • 43 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

1 views • 48 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

RowPress: A New Read Disturbance Phenomenon in Modern DRAM Chips

Demonstrating and analyzing RowPress, a novel read disturbance phenomenon causing bitflips in DRAM chips. Different from RowHammer vulnerability, RowPress showcases effective solutions on real Intel systems with DRAM chips.

0 views • 46 slides

Panopticon: Complete In-DRAM Rowhammer Mitigation

Despite extensive research, DRAM remains vulnerable to Rowhammer attacks. The Panopticon project proposes a novel in-DRAM mitigation technique using counter mats within DRAM devices. This approach does not require costly changes at multiple layers and leverages existing DRAM logic for efficient miti

1 views • 17 slides

Understanding DRAM Errors: Implications for System Design

Exploring the nature of DRAM errors, this study delves into the causes, types, and implications for system design. From soft errors caused by cosmic rays to hard errors due to permanent hardware issues, the research examines error protection mechanisms and open questions surrounding DRAM errors. Pre

1 views • 31 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

1 views • 37 slides

Power Consumption in Memory-Intensive Databases

This collection of research delves into the power challenges faced by memory-intensive databases (MMDBs) and explores strategies for reducing DRAM power draw. Topics covered include the impact of hardware features on power consumption, experimental setups for analyzing power breakdown, and the effec

1 views • 13 slides

Enhancing DRAM Performance with ChargeCache: A Novel Approach

Reduce average DRAM access latency by leveraging row access locality with ChargeCache, a cost-effective solution requiring no modifications to existing DRAM chips. By tracking recently accessed rows and adjusting timing parameters, ChargeCache achieves higher performance and lower DRAM energy consum

0 views • 33 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

CLR-DRAM: Dynamic Capacity-Latency Trade-off Architecture

CLR-DRAM introduces a low-cost DRAM architecture that enables dynamic configuration for high capacity or low latency at the granularity of a row. By allowing a single DRAM row to switch between max-capacity and high-performance modes, it reduces key timing parameters, improves system performance, an

0 views • 42 slides

Locality-Aware Caching Policies for Hybrid Memories

Different memory technologies present unique strengths, and a hybrid memory system combining DRAM and PCM aims to leverage the best of both worlds. This research explores the challenge of data placement between these diverse memory devices, highlighting the use of row buffer locality as a key criter

1 views • 34 slides

The Impact of On-Die ECC on DRAM Error Characteristics

The BEER project explores how on-die ECC complicates DRAM reliability studies by concealing error characteristics. It aims to uncover the unique ECC function of DRAM chips and infer error locations in error-prone cells. The study highlights the challenges in identifying and correcting bit flips obfu

1 views • 17 slides

Flipping Bits in Memory: DRAM Disturbance Errors

This study explores the potential errors induced in DRAM chips by flipping bits without accessing them directly, leading to disturbance errors in adjacent rows. The impact of repeatedly opening and closing rows is also investigated, highlighting potential risks associated with such actions. Addition

0 views • 15 slides

DRAMs: Lightweight Memory Technology Overview

Dynamic Random-Access Memories (DRAMs) are explored in depth, covering topics such as DRAM bit cells, operational characteristics, and logical diagrams. Learn about the destructive read nature, need for periodic refresh, and efficient hydraulic analogies for better understanding. Discover how DRAM r

2 views • 24 slides

Quick Evaluation of Physical Unclonable Functions in DRAM Devices

Leveraging the latency-reliability tradeoff in commodity DRAM devices, this study presents a novel approach to quickly evaluate Physical Unclonable Functions (PUFs) in modern DRAM technology. The research explores the unique characteristics of DRAM latency failures and proposes a method to generate

0 views • 9 slides

Enhancing System Performance with Fine-Grained In-DRAM Data Relocation

This study focuses on improving system performance by reducing DRAM latency through fine-grained data relocation and caching mechanisms. The FIGARO substrate leverages existing structures within a modern DRAM device to enhance data relocation efficiency and cache performance, resulting in notable im

1 views • 5 slides

Improving System Performance with Fine-Grained In-DRAM Data Relocation and Caching

This study presents FIGARO, a novel approach to reducing DRAM latency through in-DRAM caching. By utilizing fine-grained data relocation and caching, FIGARO optimizes system performance and energy efficiency. The implementation involves leveraging the shared global row buffer in DRAM banks for effic

0 views • 34 slides

A Case for Refresh Pausing in DRAM Memory Systems

Dynamic Random Access Memory (DRAM) faces challenges with data loss due to leakage, leading to the need for frequent refresh operations, impacting system performance. This paper delves into the growing problem of refresh overhead in DRAM systems, proposing the concept of refresh pausing to mitigate

1 views • 39 slides

Exploiting DRAM Data Retention Characteristics

DRAM research focuses on Bit-Exact ECC Recovery (BEER) to determine on-die ECC functions, operating timings, temperature dependence, aggregate failure rates, chip reliability, error distributions, inter-chip variation, and ECC obfuscation. BEER methodology induces errors to solve parity-check matric

0 views • 15 slides

Bit-Exact ECC Recovery: Determining DRAM On-Die ECC Functions

DRAM on-die ECC complicates third-party reliability studies by obfuscating raw bit errors. BEER introduces a new testing methodology to determine a DRAM chip's unique on-die ECC function, enabling valuable studies in the future.

0 views • 30 slides

Reduced Voltage Operation in Modern DRAM Devices Experimental Characterization

DRAM power is crucial in modern systems, and reducing voltage can enhance efficiency. Explore the impact on reliability, latency, and energy with new mechanisms like Voltron. Address high power consumption, low-voltage memory designs, and goals like understanding DRAM characteristics and developing

0 views • 51 slides

Enhancing DRAM Performance with CROW Substrate

Learn about CROW, a low-cost substrate that boosts DRAM performance, energy efficiency, and reliability through its innovative design. Explore the challenges of DRAM scaling and how CROW addresses them effectively, leading to significant speedups and energy savings. Discover key results showcasing t

0 views • 7 slides

SALP in DRAM: A Case for Subarray-Level Parallelism

This study advocates for Subarray-Level Parallelism (SALP) in DRAM to address the serialization of requests to the same DRAM bank. By increasing the independence of subarrays and enabling parallel operation, significant performance and energy efficiency improvements are achieved at a low cost. The s

0 views • 44 slides

Enabling Dynamic Capacity-Latency Trade-off in Low-Cost DRAM Architecture

The CLR-DRAM architecture presents a low-cost solution that allows for dynamic configuration of DRAM rows to switch between max-capacity and high-performance modes. By reconfiguring connections between DRAM cells and sense amplifiers, the system achieves reduced latency and refresh overhead. Key res

0 views • 6 slides

Project Evaluation Workshop for DRAM Pilot Programs

The workshop organized by the California Public Utilities Commission aims to assess the success of the DRAM I, DRAM II pilots, and DRAM III solicitation phase. Recommendations based on research and analysis will guide the Commission in determining the success of the auction mechanism pilots. The pro

0 views • 23 slides

Modern DRAM Simulator Ramulator 2.0 Overview

Ramulator 2.0 is a modern, modular, and extensible DRAM and memory system simulator designed to address robustness and performance issues in DRAM technology. The simulator offers fine-grained modeling of DRAM operation at the cycle level, utilizing hierarchical state-machine-based modeling for unifi

1 views • 25 slides

Efficient DRAM Caching for Hybrid Memory Systems

Discover how TicToc enables bandwidth-efficient DRAM caching in hybrid memory systems to address the challenges posed by increasing memory bandwidth and capacity demands. Explore the use of emerging memory technologies, such as 3D-DRAM and 3D-XPoint, as well as the benefits of utilizing DRAM as a ca

0 views • 25 slides

Efficient Data Movement in DRAM using LISA Subarrays

Learn about Low-Cost Inter-Linked Subarrays (LISA) enabling fast inter-subarray data movement in DRAM, addressing the bottleneck of bulk data movement, wide connectivity between subarrays, key ideas, applications, and DRAM internals. Explore the innovative solutions for improving data transfer effic

0 views • 49 slides

Effective DRAM Cache Optimization Strategies Explained

Discover innovative techniques for optimizing DRAM cache efficiency with a focus on Hit Speculation, Self-Balancing Dispatch, and Overhead Reduction. Explore the challenges of Dirty Data, the benefits of Die-Stacked DRAM technology, and the latest advancements in DRAM Cache state-of-the-art solution

0 views • 23 slides

Mitigating Data-Dependent DRAM Failures for Reliable System Operation

Explore cutting-edge methods for detecting and mitigating data-dependent DRAM failures to ensure reliable system performance. Learn about leveraging memory content, online profiling, technology scaling, and efficient detection techniques. Discover how to tackle intermittent failures and detect data

0 views • 11 slides

Improving DRAM Latency with Charge-Level-Aware Techniques

Learn about a novel approach to reducing DRAM latency using charge-level-aware look-ahead partial restoration. This method addresses the significant portion of DRAM access latency caused by cell restoration processes, leading to notable performance gains and energy savings.

0 views • 6 slides

Innovative DRAM Simulation with Ramulator 2.0

Explore Ramulator 2.0, a cutting-edge DRAM and memory system simulator designed to address robustness and performance issues in DRAM. Featuring fine-grained modeling and extensible architecture, it offers insights into memory technologies and DRAM standards.

0 views • 25 slides

Enhancing System Performance with Fine-Grained In-DRAM Data Management

Learn about FIGARO, a system designed to reduce DRAM latency through in-DRAM caching and data relocation. FIGCache optimizes memory access by caching specific row segments, resulting in a 16.3% improvement in system performance and 7.8% reduction in energy consumption on average. Explore the details

0 views • 18 slides

Addressing Prolonged Restore Challenges in DRAM Scaling

Explore the challenges of scaling DRAM in the face of technology advancements, with a focus on prolonged restore issues. Learn about the complexities of DRAM operations, scaling trends, and the demands for continued scaling to meet evolving computational needs.

0 views • 53 slides