Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the need for a variation-aware DRAM power model for more precise calculations.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study

DRAM Power Is Becoming a Major Design Concern 0.5 Total System Energy 0.4 0.3 Fraction of 0.2 0.1 0.0 Malladi+ ISCA '12 ISCA '15 Report '16 HPCA '10 ICAC '11 ISCA '12 David+ Elmore+ Ware+ Paul+ Yoon Page 2 of 20

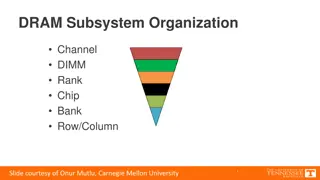

Outline Background: DRAM Organization & Operation Characterization Methodology New Findings on DRAM Power Consumption VAMPIRE: A Variation-Aware DRAM Power Model Conclusion Page 3 of 20

Simplified DRAM Organization and Operation DRAM Chip . . . Bank 0 Bank 7 Processor Chip DRAM Cell Array . . . activation Core Core Row Buffer Column Select Shared Last-Level Cache . . . Memory Controller Bank Select I/O Drivers I/O Drivers memory channel Page 4 of 20

Outline Background: DRAM Organization & Operation Characterization Methodology New Findings on DRAM Power Consumption VAMPIRE: A Variation-Aware DRAM Power Model Conclusion Page 5 of 20

Power Measurement Platform Keysight 34134A DC Current Probe DDR3L SO-DIMM Virtex 6 FPGA JET-5467A Riser Board Page 6 of 20

Methodology Details Page 7 of 20

Outline Background: DRAM Organization & Operation Characterization Methodology New Findings on DRAM Power Consumption VAMPIRE: A Variation-Aware DRAM Power Model Conclusion Page 8 of 20

1. Real DRAM Power Varies Widely from IDD Values 100 200 800 Datasheet Corrected Datasheet Measured 80 Current (mA) Current (mA) 150 600 Current (mA) 60 100 400 40 50 200 20 0 0 0 A B C A B C A B C Page 9 of 20

2. DRAM Power is Dependent on Data Values 800 800 Write Current (mA) Read Current (mA) Vendor A Vendor B Vendor C 600 600 400 400 Vendor A Vendor B Vendor C 200 200 0 0 0 Number of Ones in a Cache Line 128 256 384 512 0 Number of Ones in a Cache Line 128 256 384 512 Page 10 of 20

3. Structural Variation Affects DRAM Power Usage 1.4 Idle Current Normalized 1.2 1.0 0.8 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 Vendor A Vendor B Vendor C 1.1 Read Current Normalized 1.0 0.9 0.8 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 Vendor A Vendor B Vendor C 1.20 1.15 1.10 1.05 1.00 0.95 Normalized Measured Vendor A Vendor B Vendor C Current 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Number of Ones in Row Address Page 11 of 20

4. Generational Savings Are Smaller Than Expected Page 12 of 20

Summary of New Observations on DRAM Power Page 13 of 20

Outline Background: DRAM Organization & Operation Characterization Methodology New Findings on DRAM Power Consumption VAMPIRE: A Variation-Aware DRAM Power Model Conclusion Page 14 of 20

A New Variation-Aware DRAM Power Model Inputs VAMPIRE Outputs (from memory system simulator) Read/Write and Data-Dependent Power Modeling Per-vendor power consumption Trace of DRAM commands, timing Idle/Activate/Precharge Power Modeling Range for each vendor (optional) Data that is being written Structural Variation Aware Power Modeling Page 15 of 20

VAMPIRE Has Lower Error Than Existing Models 250% Micron Model DRAMPower VAMPIRE Percentage Error Mean Absolute 200% 160.6% 150% 100% 50% 32.4% 6.8% 0% Vendor A (8 modules) Vendor B (7 modules) Vendor C (7 modules) GMean Page 16 of 20

VAMPIRE Enables Several New Studies 1.2 Baseline BDI Optimized OWI DRAM Energy Normalized 1.1 -12.2% 1.0 0.9 0.8 0.7 Vendor A Vendor B Vendor C GMean Page 17 of 20

Outline Background: DRAM Organization & Operation Characterization Methodology New Findings on DRAM Power Consumption VAMPIRE: A Variation-Aware DRAM Power Model Conclusion Page 18 of 20

Conclusion Page 19 of 20

What Your DRAM Power Models Are Not Telling You: Lessons from a Detailed Experimental Study

Backup Slides Page 21 of 20

More Information in the Paper 1.1 Normalized Baseline BDI Optimized OWI Energy 1.0 0.9 0.8 Vendor A Vendor B Vendor C Page 22 of 20

Todays Models Leave a Lot to Be Desired Page 23 of 20

How Do We Measure Current? VDD USB Host PC Probe PCI-e FPGA DRAM Module PCI-e IF Cmd Buffer Rank . . . Chip Chip memory channel SoftMC [1] [1] Hassan et al. SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies, HPCA, 2017. Page 24 of 20

Foundation of Current Power Models IDD0 Activation and Precharge IDD1 Activation 1 Column Read Precharge IDD2N Precharge Standby (all banks are precharged/closed) clk enabled IDD3N Active Standby (all banks are active/opened) clk enabled IDD2P Precharge Power-Down (all banks are precharged/closed) clk disabled IDD3P Active Power-Down (all banks are active/opened) clk disabled IDD4R/W Burst mode Read/Write IDD5B Burst mode Refresh IDD7 Activate Column Read w/ Auto Precharge Page 25 of 20

Whats So Bad About That? Page 26 of 20

IDD0: Activation and Precharge Energy DRAM Array tRAS tRP tRAS 0xF0 ACT PRE ACT PRE time 0x00 Row Buffer Measured Current0.50 0.30 200 Datasheet Measured 0.45 150 Normalized Current (mA) 0.40 100 0.35 50 0 A B C Vendor A Vendor B Vendor C Page 27 of 20

IDD1: Activation, Read, and Precharge Energy DRAM Array 0xF0 tRCD tRP PRE RD ACT ACT tRAS 0x00 time Row Buffer Measured Current0.70 0.20 350 Datasheet Measured 300 0.60 Current (mA) Normalized 250 0.50 200 150 0.40 100 0.30 50 0 Vendor A Vendor B Vendor C A B C Page 28 of 20

IDD2N: Precharged Standby Bank 0 Bank 1 DRAM Array Bank 7 DRAM Array DRAM Array (1) Precharge All Banks (Close Row Buffers) (2) Wait Row Buffer Row Buffer Row Buffer Measured Current1.00 0.20 0.80 Normalized 0.60 0.40 A B C Page 29 of 20

IDD3N: Active Standby Bank 0 Bank 1 Bank 7 DRAM Array DRAM Array DRAM Array (1) Activate All Banks (Open Row Buffers) (2) Wait Row Buffer Row Buffer Row Buffer Measured Current0.70 0.20 0.10 200 Datasheet Measured 0.60 150 Current (mA) Normalized 0.50 100 0.40 0.30 50 0 Vendor A Vendor B Vendor C A B Page 30 of 20 C

IDD2P: Precharged Power Down Bank 0 Bank 1 DRAM Array Bank 7 DRAM Array DRAM Array (1) Precharge All Banks (Close Row Buffers) (2) Wait Row Buffer Row Buffer Row Buffer Measured Current1.20 0.20 0.00 80 Datasheet Measured 1.00 60 Current (mA) Normalized 0.80 40 0.60 0.40 20 0 Vendor A Vendor B Vendor C A B C Page 31 of 20

IDD4R: Burst Read Current Bank 0 Bank 1 Bank 7 (1) Activate All Banks (Open Row Buffers) DRAM Array DRAM Array DRAM Array (2) Read one column at a time Row Buffer Row Buffer 15 0x00 0x33 Row Buffer 9 0x00 0x33 (3) Interleave across banks after each read 7 0 1 8 0x00 0x33 800 Datasheet Measured Corrected 600 Current (mA) 400 200 0 Vendor A Vendor B Vendor C Page 32 of 20

IDD4W: Burst Write Current Bank 0 Bank 1 Bank 7 (1) Activate All Banks (Open Row Buffers) DRAM Array DRAM Array DRAM Array (2) Write one column at a time Row Buffer Row Buffer 15 0x00 0x33 Row Buffer 9 0x00 0x33 (3) Interleave across banks after each read 7 0 1 8 0x00 0x33 600 Datasheet Measured Current (mA) 400 200 0 Vendor A Vendor B Vendor C Page 33 of 20

IDD5B: Refresh in Burst Mode Burst Mode: tRFC tRFC tREFI (64ms) REF REF REF time tRFC Measured Current1.00 0.50 0.90 Normalized 0.80 0.70 0.60 A B C Page 34 of 20

IDD7: Read, Auto-Precharge ACT-RDA tRRD ACT-RDA tRRD ACT-RDA tRRD time 800 Measured Current0.65 0.35 Datasheet Measured 0.60 600 Current (mA) Normalized 0.55 400 0.50 0.45 200 0.40 0 A B C Vendor A Vendor B Vendor C Page 35 of 20

Impact of Bit Toggling on DRAM Power . . . Bank 0 Row Buffer 1 Bank 1 Row Buffer 1 Bank 7 Row Buffer 1 column number 0 2 c 1 0 2 c 1 0 2 c 1 . . . 0000 1010 1111 0011 1011 0010 1011 0110 1011 0010 1011 0110 . . . . . . . . . . . . Column Select Column Select Column Select 1 . . . global bitlines global bitlines Bank Select 2 peripheral bus to I/O drivers Page 36 of 20

Data Dependency Model Read Write F (mA) G (mA) H (mA) F (mA) G (mA) H (mA) Vendor A 246.44 0.433 0.0515 531.18 -0.246 0.0461 Vendor B 217.42 0.157 0.0947 466.84 -0.215 0.0166 Vendor C 234.42 0.154 0.0856 368.29 -0.116 0.0229 y = F + y = F + Gn Gn + + Ht Ht Additional current per logic-1 Additional current per bit toggle 800 800 Read Current (mA) Write Current (mA) 600 600 400 400 Vendor A Vendor B Vendor C 200 200 0 0 0 Number of Ones in a Cache Line 128 256 384 512 0 128 256 384 512 Number of Ones in a Cache Line Page 37 of 20

Models https://github.com/CMU-SAFARI/VAMPIRE Page 38 of 20

Structural Variation 1.4 Normalized Normalized Active Standby Active Standby Energy across Banks Current 1.2 1.0 0.8 0 12 3 4 5 6 7 0 12 3 4 5 6 7 0 12 3 4 5 6 7 Vendor A Vendor B Vendor C 1.1 Normalized Normalized Read Read Burst Energy across Banks Current 1.0 0.9 0.8 0 12 3 4 5 6 7 0 12 3 4 5 6 7 0 12 3 4 5 6 7 Vendor A Vendor B Vendor C 1.1 Write Current Normalized 1.0 0.9 Normalized Write Burst Write Burst Energy across Banks 0.8 0 12 3 4 5 6 7 0 12 3 4 5 6 7 0 12 3 4 5 6 7 Vendor A Vendor B Vendor C Page 39 of 20

Evaluated System Configuration Processor x86-64 ISA, one core 3.2 GHz, 128-entry instruction window Cache L1: 64 kB, 4-way associative; L2: 2 MB, 16-way associative Memory Controller 64/64-entry read/write request queues, FR-FCFS [119, 149] DRAM DDR3L-800 [57], 1 channel, 1 rank/8 banks per channel Page 40 of 20

Trends Across Generations 400 200 Datasheet Measured Datasheet Measured Current (mA) Current (mA) 300 150 -112.1mA -192.1mA 200 100 100 50 -53.7mA -64.0mA 0 0 2010 2011 2012 2013 2014 2015 Year Manufactured Activation Energy 2010 2011 2012 2013 2014 2015 Year Manufactured Precharge Standby Energy 700 700 Datasheet Measured Datasheet Measured 600 600 Current (mA) Current (mA) 500 500 -200.2mA -212.2mA -140.6mA 400 400 300 300 -147.4mA 200 200 100 100 0 0 2010 2011 2012 2013 2014 2015 Year Manufactured Read Energy 2010 2011 2012 2013 2014 2015 Year Manufactured Write Energy Page 41 of 20

Data Encoding 1.2 Baseline BDI Optimized OWI Normalized Energy 12.5% Energy Reduction 1.0 0.8 0.6 Vendor A Vendor B Vendor C Page 42 of 20

Validating Our DRAM Power Models Page 43 of 20