Flipping Bits in Memory: DRAM Disturbance Errors

This study explores the potential errors induced in DRAM chips by flipping bits without accessing them directly, leading to disturbance errors in adjacent rows. The impact of repeatedly opening and closing rows is also investigated, highlighting potential risks associated with such actions. Additionally, the study delves into the effects on x86 CPUs and DRAM modules through a series of loops and operations.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Flipping Bits in Memory Flipping Bits in Memory Without Accessing Them: Without Accessing Them: DRAM Disturbance Errors DRAM Disturbance Errors Yoongu Kim Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, Onur Mutlu

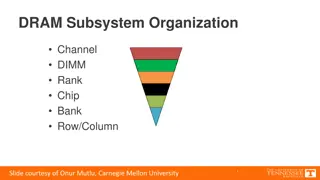

DRAM Chip DRAM Chip Wordline Row Row Row Row Row

DRAM Chip DRAM Chip Wordline Row Row Opened Row Opened Row Row Row V VHIGH HIGH

DRAM Chip DRAM Chip Wordline Row Row Closed Row Closed Row Row Row V VLOW LOW

DRAM Chip DRAM Chip Wordline Row Row Opened Row Opened Row Row Row V VHIGH HIGH

DRAM Chip DRAM Chip Wordline Row Row Opened Row Opened Row Row Row V VHIGH HIGH

DRAM Chip DRAM Chip Wordline Row Row Opened Row Opened Row Row Row V VHIGH HIGH Repeatedly opening and closing a row induces disturbance errors disturbance errors in adjacent rows

x86 CPU x86 CPU DRAM Module DRAM Module loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop X Y

x86 CPU x86 CPU DRAM Module DRAM Module loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop X Y

x86 CPU x86 CPU DRAM Module DRAM Module loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop X Y

x86 CPU x86 CPU DRAM Module DRAM Module loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop X Y

Most Modules At Risk Most Modules At Risk 83% 83% 88% 88% 86% 86%

Most Modules At Risk Most Modules At Risk 83% 83% 88% 88% 86% 86% After ???? After ???? After ????

Most Modules At Risk Most Modules At Risk 83% 83% 88% 88% 86% 86% After ???? After ???? After ???? ??? Errors ??? Errors ??? Errors

Flipping Bits in Memory Flipping Bits in Memory Without Accessing Them: Without Accessing Them: DRAM Disturbance Errors DRAM Disturbance Errors 4:30 4:30 PM PM