Cutting-Edge Analog IPs for High-Density SRAM and GPIO

Explore the latest advancements in analog IPs showcased at AMICSA 2018, including high-density Dual Port SRAM, General Purpose IO with local POC, Voltage Monitor, and more. Dive into the details of technology, features, and specifications for these cutting-edge designs. Discover how these innovations enhance performance and reliability in semiconductor applications.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

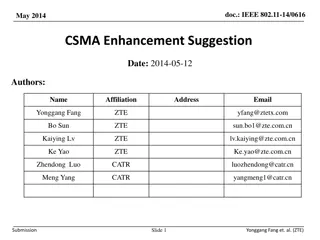

DARE180U NEW ANALOG IPS LAURENT BERTI AMICSA 2018, LEUVEN PUBLIC

INTRODUCTION Technology and context High Density Dual Port SRAM General Purpose IO (GPIO) with local POC Voltage Monitor Power-On Reset Cristal Oscillator Extended Frequency Range PLL 11-BIT SAR ADC AMICSA 2018 2

TECHNOLOGY/CONTEXT UMC L180 MM/RF 1.8V/3.3V, Single Poly 6 Metal (1P6M), P-Sub/Twin-Well DARE180U platform/ecosystem Single Event model ELT transistor PCELL Enhanced Model (including asymmetry...). ELT aging model RAD layout rule check AMICSA 2018 3

HIGH DENSITY DUAL PORT SRAM (DARE180U_HDRAM) High Density Dual port SRAM 4096x13 bits. Clock to output available write: max. 3.8ns Clock to output available read: max. 5.3ns Use of straight transistors only. Other RAD rules (N area isolation...) enforced. Clock tree and address decoder hardened against SET. Word bit s separation of 57 m (hardening versus MBU) Designed SEL free till 80 MeV*cm2/mg Area reduction: 50% AMICSA 2018 4

GENERAL PURPOSE IO (GPIO) WITH LOCAL POC (DARE180U_GPIO) Digital input (Schmitt trigger) with programmable pull-up/pull-down Digital output (4mA drive) Analog input (serial impedance of 50 Ohms with secondary ESD protection) Analog output Designed SEL and SET free till respectively 80 and 60 MeV*cm2/mg A EN_DO_int ANA_0 Prim. Clamp Sec. Clamp ANA_50 Core 50 Ohm PAD PU PD Z PU_int PD_int EN_DI_int EN_DO EN_DI EN_DO_int EN_DI_int PU_int PD_int CTRL PU PD AMICSA 2018 5

GENERAL PURPOSE IO (GPIO) WITH LOCAL POC (DARE180U_GPIO) TR33 Local Power On Control (POC) to prevent glitches during the power ramp-up and the power ramp-down TR33 TF33 100ms VDD3V3 3.3V 2.2V VDD1V8 1.8V 1.5V 0.6V Vres33 Vres18 min 200us ~20ms ~20ms POR_RN Active POC Pull-Up 1MOhms Pull-Down 1MOhms AMICSA 2018 6

VOLTAGE MONITOR (DARE180U_VMON) 3.3V voltage monitor 3 bits to setup the detection level from 2.9V till 3.25V (step of 50mV) Glitches filtering (20 s) Designed SEL and SET free till respectively 80 and 60 MeV*cm2/mg Hysteresis Combined with BG_OK 2.9 to 3.25V by 50mV step 0 to 550 s AMICSA 2018 7

VOLTAGE MONITOR (DARE180U_VMON) 1.8V voltage monitor 3 bits to setup the detection level from 1.6V till 1.75V (step of 25mV) Glitches filtering (20 s) Designed SEL and SET free till respectively 80 and 60 MeV*cm2/mg Hysteresis Combined with BG_OK 1.6 to 1.75V by 25mV step AMICSA 2018 8

POWER-ON RESET (DARE180U_POR) 1.8V detection Programable reset pulse with external capacitor Designed SEL and SET free till respectively 80 and 60 MeV*cm2/mg Programable pulse width: - Cext = 0nF => 235 s typ - Cext = 220nF => 150ms typ AMICSA 2018 9

CRISTAL OSCILLATOR (DARE180U_XO) Frequency range: 5MHz (Rakon crystal ESCC 3501/019), 100 A typ., 18 ppm, startup time 1.4ms typ. 25MHz (Rakon crystal ESCC 3501/01/8), 450 A typ., 11 ppm, startup time 1.8ms typ. Designed SEL free till 80 MeV*cm2/mg Designed SET free till 60 MeV*cm2/mg: No double edge Max. 1.1ns phase error at 25 MHz (~2% phase error) Max. 3.8ns phase error at 5MHz (~2% phase error) AMICSA 2018 10

EXTENDED FREQUENCY RANGE PLL (DARE180U_PLL_EXT) VCO frequency range 280MHz till 400MHz Designed SEL free till 80 MeV*cm2/mg Designed SET free till 60 MeV*cm2/mg: No double edge Max. 160ps phase error @FVCO = 400 MHz Max. 600ps phase error @FVCO = 280 MHz Programmable frequency division: 8, 16, 20, 32, 40 and 80. Thermal jitter: 1ps typ up Lock Detector PLL_LOCK down PLL_PD up PLL_IN PFD CP LP VCO PLL_OUT down PLL_FB_IN Synchronous divider by N PLL_FB_OUT PLL_DIV<2:0> AMICSA 2018 11

EXTENDED FREQUENCY RANGE PLL (DARE180U_PLL_EXT) HARDENING PFD: by drive strength Synchronous divider: triplication with reset after each cycle (state-machine) Charge Pump: current limitation combined with clamp *10 *10 1 A 100ps => F = 15MHz => Vont of 15mV *10 *10 Charge 1 10 40k Vcont *10 *10 630pF Discharge 8pF *10 13k *10 1 A *10 AMICSA 2018 12

EXTENDED FREQUENCY RANGE PLL (DARE180U_PLL_EXT) HARDENING VCO: analog averaging *20 *20 *20 *20 *20 40k AMICSA 2018 13

11-BIT SAR ADC (DARE180U_ADC) 8:2 analog mux Bypass Auto zeroed differential amplifier (0dB, 6dB and 12dB). Wide input common mode Hardening: SET simulation result? 6R 4R 5R 15R INN<3> PAD Resd Sec. clamp 6R 4R 5R 15R INN<2> PAD Resd Sec. clamp 7 6R 4R 5R 15R INN<1> PAD Resd Sec. clamp 6R 4R 5R 15R INN<0> PAD Resd Sec. clamp OUTP 3 2 1 5 6 INP<0> PAD 4 OUTN Min input CM [V] Max input CM [V] | INP<i> - INN<i> | [V] Resd Sec. clamp Gain [dB] 0 6R 4R 5R 15R 0 VDDA 2 INP<0> PAD Resd Sec. clamp 6R 4R 5R 15R 6 VDDA/8 7/8*VDDA 1 8 12 3/16*VDDA 13/16*VDDA 0.5 INP<0> PAD Resd Sec. clamp 6R 4R 5R 15R INP<0> PAD Resd Sec. clamp 6R 4R 5R 15R AMICSA 2018 14

11-BIT SAR ADC (DARE180U_ADC) SAR ADC configurable in differential or single-ended mode (11-bit interface, ENOB WC of 10 bits at 300kS/s) Internal voltage reference (external capacitor free) Auto zeroed comparator Total current consumption 5mA (including analog-mux amplifier) AMICSA 2018 15

11-BIT SAR ADC (DARE180U_ADC) HARDENING Designed SEL free till 80 MeV*cm2/mg Digital hardening by: drive strength for the critical combinatorial gates Use of Hit FF Signal driving switches of the capa-bank are not hardened: the SET is filtered by the limited bandwidth Muller-C filter for the non critical signal (DataOut...) Weak Latch AMICSA 2018 16

11-BIT SAR ADC (DARE180U_ADC) HARDENING Comparator hardening: Use an auto-zeroed architecture => don t need big input transistor Comparator cross section of 80 m2 @0.1 MeV*cm2/mg for an error of 1 LSB3 3200 events (1LSB) per year on Geo worst week without shielding. Capa-bank hardening Total capa-bank switches area: 240 m2 Cunit = 12.5 fF SEU of 1 LSB correspond to 0.6 MeV*cm2/mg 10 events (1LSB) per year on Geo worst week without shielding. AMICSA 2018 17