GRIT Meeting 2019 Faster Status Overview

This document provides an overview of the GRIT Meeting 2019 focusing on the status update of the FASTER project. It covers various topics including real-time algorithms, clock synchronization, data and diagnostic trees, and proposed future developments. The images included showcase details on the agenda, system specifications, real-time algorithms, and device configurations discussed during the meeting.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

GRIT meeting 2019 FASTER STATUS 10 October2019 Carniol Benjamin, Chaventr Thi rry, Cussol Daniel, Etasse David, Fontbonne Cathy, Fontbonne Jean-Marc, Harang Julien, Hommet Jean, Langlois J rome, Poincheval J rome 1

AGENDA FASTER-V2 1. FASTER OVERVIEW 2. FASTER REAL TIME ALGORITHMS 3. FASTER CLOCK AND T0 TREE 4. FASTER DATA AND DIAGNOSTIC TREE FASTER AND GRIT DETECTOR 1. FASTER AND AGATA PROPOSAL 1. GRIT DAUGTHER BOARD 2. GRIT MOTHER BOARD 3. FMC DAUGHTER BOARD WITH 5 PLAS 4. PLANNING 2 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 OVERVIEW Offline Analysis RHB Real Time Algorithms Modular Electronic Ubuntu repository Based on Root 3 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 OVERVIEW STANDALONE SYSTEM MULTI-CHANNEL SYSTEM 1 VITA 57 slot, 1 FPGA (C5 140 LE) 1 Gb/s Ethernet 2 VITA 57 slots, AMC.2 full size module, 3 FPGA(s) (C5 140 LE) 1 and 10 Gb/s Ethernet 10 MHz Clock synchronization FPGA firmware loading by Ethernet 4 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 OVERVIEW STANDALONE SYSTEM MULTI-CHANNEL SYSTEM 4 FADC (125MHz@14bits) 1V, 2V, 5V, 10V input range 25 MHz Bandwidth 2 FADC (500MHz@12bits) 1V input range 1V input adjustable Offset 100 MHz Bandwidth DDC316 from TI 32 channels I-TO-V conversion front end 3pC to 12 pC (full scale) Integration time range from 10us to 10 ms ISEG BPS-Serie - 4W 500 V to 6 KV FMC project (CERN) 5 I/O ports 200 MHz Bandwidth LVTTL 5 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 REAL TIME ALGORITHMS Time resolution VS signal amplitude FASTER-CRRC4 FASTER-TRAPEZ-TDC FASTER-QDC-TDCHR FASTER-RF FASTER-SCALER FASTER-SAMPLER FASTER-ELECTROMETER Demon detector, CARAS board, FASTER-QDC-TDCHR FASTER_HV 60Co HPGe detector, MOSAHR board, FASTER_ADC 6 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

AGENDA FASTER-V2 1. FASTER OVERVIEW 2. FASTER REAL TIME ALGORITHMS 3. FASTER CLOCK AND T0 TREE 4. FASTER DATA AND DIAGNOSTIC TREE FASTER AND GRIT DETECTOR 1. FASTER AND AGATA PROPOSAL 1. GRIT DAUGTHER BOARD 2. GRIT MOTHER BOARD 3. FMC DAUGHTER BOARD WITH 5 PLAS 4. PLANNING 7 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 CLOCK AND T0 TREE T0 Common signal INHIBIT T0 20 MHz START Register 20 MHz 10 MHz Clock T0 Common signal 10 MHz Clock Common signal 8 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 DATA AND DIAGNOSTIC TREE FPGA1 FPGA2 5Gb/s Time sort function 1 and 10 Gb/s Trigger Merger Function 5Gb/s INHIBIT SIGNAL Lock function UDP/IP Protocol 9 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 DATA AND DIAGNOSTIC TREE FPGA1 FPGA2 FPGA1 FPGA2 FPGA1 FPGA2 Time sort function Time sort function Time sort function Trigger Merger Function Trigger Merger Function Trigger Merger Function INHIBIT SIGNAL INHIBIT SIGNAL INHIBIT SIGNAL Lock function Lock function Lock function UDP/IP Protocol UDP/IP Protocol UDP/IP Protocol Time sort function Introspection data 10 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 DATA AND DIAGNOSTIC TREE Time sort function Introspection data 11 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER-V2 DATA AND DIAGNOSTIC TREE Introspection data 12 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

AGENDA FASTER-V2 1. FASTER OVERVIEW 2. FASTER REAL TIME ALGORITHMS 3. FASTER CLOCK AND T0 TREE 4. FASTER DATA AND DIAGNOSTIC TREE FASTER AND GRIT DETECTOR 1. FASTER AND AGATA PROPOSAL 1. GRIT DAUGTHER BOARD 2. GRIT MOTHER BOARD 3. FMC DAUGHTER BOARD WITH 5 PLAS 4. PLANNING 13 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

FASTER AND AGATA GRIT AGATA DETECTOR PAC DETECTOR PAC 1 Pulse/s Trigger Request GTS PLAS FASTER TO AGATA INTERFACE MODULE AGATA DAQ Or T0 100 MHz 10 MHz 100 Mhz SMART DAQ T0 T0 Global MERGER using The timestamp information 14 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

AGENDA FASTER-V2 1. FASTER OVERVIEW 2. FASTER REAL TIME ALGORITHMS 3. FASTER CLOCK AND T0 TREE 4. FASTER DATA AND DIAGNOSTIC TREE FASTER AND GRIT DETECTOR 1. FASTER AND AGATA PROPOSAL 1. GRIT DAUGTHER BOARD 2. GRIT MOTHER BOARD 3. FMC DAUGHTER BOARD WITH 5 PLAS 4. PLANNING 15 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

GRIT DAUGHTER-BOARD (2 Telescopes) 12 V (120W) DAUGHTER- BOARD 12 V (60W) 1 Gb/s (Data and Slow control bus) 12 V (120W) 28 Telescopes could be managed by a small UTCA crate TRIG RQ BUFFERS TRIG RQ DAUGHTER- BOARD T0 T0 20 MHz 20 MHz 12 V (60W) 12 V (60W) 1 Gb/s (Data and Slow control bus) 1 Gb/s (Data and Slow control bus) TRIG RQ BUFFERS T0 TRIG RQ TRIG RQ BUFFERS TRIG RQ T0 T0 T0 20 MHz 20 MHz 20 MHz 20 MHz 12 V (60W) 1 Gb/s (Data and Slow control bus) 48 Telescopes could be managed by the largest crate TRIG RQ BUFFERS TRIG RQ T0 T0 20 MHz 20 MHz 16 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

GRIT MOTHER-BOARD (1 Telescope) VACCUM POWER 12 V (60W) 1 Gb/s (Data and Slow control bus) FPGA TRIG RQ TRIG RQ TRIG RQ T0 T0 T0 20 MHz 20 MHz 20 MHz SPI bus 17 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

PLAS DAUGHTER-BOARD GRIT Telescope POWER I2C bus SPI to i2c bridge 32 Ch SPI bus PLAS config F AAF 32 Ch PLAS (160 channels) AAF telescope out + multiplexer 32 Ch Analog ADC PLAS out - AAF n*50 Mhz 32 Ch 20 Mhz PLL PLAS 100 Mhz AAF 32 Ch Power PLAS trigRQ AAF Readout Crtl (30W ) TS RST 18 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

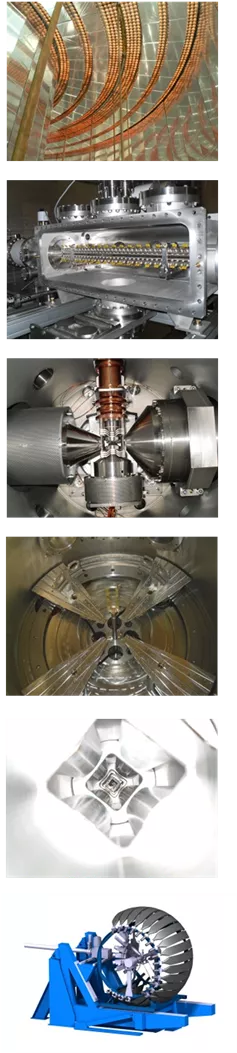

CHAMBER DETECTOR 19 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

AGENDA FASTER-V2 1. FASTER OVERVIEW 2. FASTER REAL TIME ALGORITHMS 3. FASTER CLOCK AND T0 TREE 4. FASTER DATA AND DIAGNOSTIC TREE FASTER AND GRIT DETECTOR 1. FASTER AND AGATA PROPOSAL 1. GRIT DAUGTHER BOARD 2. GRIT MOTHER BOARD 3. FMC DAUGHTER BOARD WITH 5 PLAS 4. PLANNING 20 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

Possible Planning November-December 2019 : PLAS to the foundry 11 weeks December 2019 May 2020: design and manufacture the PLAS test board HMI 21 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

PHASE1 FMC DAUGHTER-BOARD WITH 1 PLAS trigRQ POWER config I2C bus SPI to i2c bridge SPI bus trigRQ TS RST Preamp Board 32 Ch Readout Crtl out + ADC PLAS out - AAF n*50 Mhz pulses 100 Mhz 20 Mhz PLL 22 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

Possible Planning November-December 2019 : PLAS to the foundry 11 weeks December 2019 May 2020: design and manufacture the PLAS test board HMI May 2020- November 2020: test of PLAS V2 ok -> board with several PLAS V2 Discussion V2 Nok-> Modify V2 or V3? THANK YOU 23 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

CONCLUSION FASTER is a digital modular acquisition system from the electronic front end to the histogram builder software developped at LPC. FASTER is very easy to install, to use with great performances. FASTER is able to perform the main nuclear functions with a set of hardware very reduced. FASTER is wireless . FASTER is designed to handle medium size experiment (from one to few hundred channels). FASTER could be designed to handle large size experiment (from one to few thousand channels). FASTER could be used with AGATA. Budget for PHASE1 -> FASTER Budget 1 FTE/years from 2018 (middle) -> 2019 (end) 24 GRIT Meeting 2019, FASTER STATUS , Benjamin Carniol & David Etasse

DIGITAL DATA ACQUISITION WITH ANALOG MEMORY ASIC Digital Signal Processing : - BLR - SHAPER -> NRJ - CFD -> TDC - TimeStamp Fs ADC FPGA PAC AAF BW -> Fmax Fc < ~Fmax Fe > 2 * Fmax N bits Fs Analog Memory ADC FPGA PAC AAF Freadout Fc < ~ 100 Mhz Fe = 200 MHz ENOB = 12 bits TimeStamp Trigger position BW ~ 100 MHz Digital Signal Processing : - BLR - SHAPER -> NRJ - CFD -> TDC 25 GRIT Meeting 2019, STATUS of FASTER, Benjamin Carniol & David Etasse