Development of Silicon Tracker and Sensor Technology for sPHENIX Detector

Research and development efforts are underway for silicon tracker and sensor technology to enhance the functionality of the sPHENIX detector. The project aims to improve mass resolution, cover specific areas effectively, and optimize sensor configurations. Various sensor concepts are being explored to meet the performance requirements and ensure efficient data collection and analysis for the sPHENIX detector.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

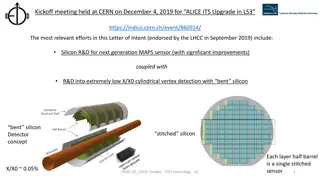

Silicon tracker and sensor R&D for sPHENIX Japan Korea PHENIX meeting November 28 Y. Akiba

sPHENIX detector EMCal + Hcal covering 2pi x |eta|<1 Babar Solenoid (1.5 T) Silicon tracker inside Babar solenoid

Measurement of Upsilion Driver of the tracker performance requirement is to measure three upsilon states. mass resolution better than 100MeV for Upsilon A large radius (60cm to 80cm outer-most) is needed

Tracker concept EMCAL To cover | |<1.1 R=60 cm zmax = 80cm Area = 6.0m2 R=35 cm zmax = 45cm Area = 2.0m2 R=10 cm zmax = 14cm Area = 0.2m2 Total Area: 8.2 m2 of silicon (single layer) S2(R=60cm) S1ab (R=35cm) S0ab (R=10cm) About 1000 10x10cm sensors needed Reconfigured VTX

Sensor concept (1) HPK has double metal technology, which can bring the read-out of the strip to the side of the sensor Read-out line direction Strip direction We used this technique in stripixel sensor of VTX. Note that the strip runs in the horizontal direction The merit of this design is that we can run the cooling of the chips along the ladder

Sensor concept (2) We can also make one section like this. Here one vertical read-out line is connected to two strips. Such a design is useful for sensor at large R, where occupancy is low. This will same the number of SVX4 chips needed, and also reduces the data size. There is ambiguity which strip (8mm long) is hit. But this should not be a problem at a large R. The occupancy is so low that the tracking software should be able to figure out which strip is the real hit. For the outer most layer, I think we can connect , for example, 6 short (8mm) strips to one vertical read-out line.

Sensor concept for S2 (lagest) 96mmx92.16mm active area Divided into 12x12 blocks Each block is 8mm x 7.68mm and made of 128 strips of 8mm x 60 micron Upper 6 bocks are connected upwards. Lower 6 blocks are connected by downwards 24 SVX4 chips to read- out the entire sensor

Sensor concept (3) For three additional strip layers (S0, S1, S2), one can make one type of sensor for each layer. For all of the three types of sensors, one strip is (60micron)x8mm, and one read-out section is (60x128 micron)x8mm = 7.68mm x 8.00 mm. All of the three types of sensor are read-out by 24 SVX4 chips. 12 chips in the upper size, 12 chips in the lower side. S0: R=10cm. One SVX4 read-outs 1 section. 1channel 1strip. Sensor size: 16mm x 96mm. 6 sensors per wafer S1: R=35cm. One SVX4 read-outs 3 sections. 1 channel 3 strips. Sensor size: 48mm x 96 mm. 2 sensors per wafer S2: R=60cm. One SVX4 read-outs 6 sections. 1channel 6 strips. Sensor size: 96mm x 96mm. 1 sensor per wafer

Stereo angles (for S1 and S0) Small stereo angle can be implemented for S1 and S0 This will improve the Z position resolution Stereo angle +/-1/64 We use the similar design for Stripixel of VTX

HPK design for the S2 sensor 98mm x 98mm is the largest sensor that HPK can make We will make a protype of this sensor soon

3 sensors S2 sensor S1 sensor S0 sensor Bonding pads for 12 SVX4s Bonding pads for 12 SVX4s Bonding pads for 12 SVX4s Bonding pads for 12 SVX4s OR Bonding pads for 12 SVX4s Bonding pads for 12 SVX4s

ROC and sensor modules ROC FPGA SVX4 Use common ROC for all three types of sensor modules

Read-out scheme (Final) Bus to fiber converter Read-out bus (point to point) Data fiber bundle to Counting House C N T L Data fibers F E M F E M F E M F E M F E M To DCM-2

Stave prototype Rectangular channel for cooling and support Make a few to cool ROC and to operate it.

Prototype ladder ROC or Hybrid Support/cooling SVX4 Silicon Sensor S1a/b ladder (double layer) S2 ladder (single layer) A full size ladder requires many SMs. Perhaps ~half ladder for S1 and S2 is a realistic goal?

SVX4 Silicon Sensor S0b S0a Placement of S0 ladder into a barrel is more challenging In this case, I think one-sided structure like above is needed. (or is there any good idea?)

S0a/b 20mm FPGA SVX4 15mm ROC 12mm 15.36mm 96mm Sensor active area: 15.36 mm x 96mm (15.36mm = 60 micron x 128 x 2) Read-out by one side. Otherwise, it is difficult to form a barrel mechanically. A possible solution is sensor/ROC configuration shown above. One strip ix 16mm long, read-out by a SVX4 chip. In the cartoon above, a blue chip reads a blue areas, and a green chip reads a blue area. If we have one cooling/support per such SM Sensor: 0.68% Cooling/support: 1.54% x (7mm/15.36mm)=0.7% ROC: 0.8% (the area of the ROC is very close to that of the sensor active area) Bus and additional support: 0.1% Overlap: 15% Total: (0.68+0.7+0.8+0.1)*1.15=2.6%

Tracker configuration The minimum L to achieve 1.4% resolution is 44cm for 1.5% rad. Length S1a/b. So I think the following configuration is reasonable and quite feasible to make. Layer Radius (cm) X0 type W(phi) (micron) L(z) (mm) Stereo # of strip/ch B0 2.5 1.3% pixel 50 0.425 NA NA B1 5.0 1.3% pixel 50 0.425 NA NA S0a 9.8 2.6% strip 60 16.0 +1/32 1 S0b 10.2 strip 60 16.0 -1/32 1 S1a 34.8 1.5% strip 60 8.0 +1/64 3 S1b 35.2 strip 60 8.0 -1/64 3 S2 60.0 1% strip 60 8.0 0 6

Sensor R&D status Working with Hamamatsu on the first prototype of S2 sensor (the outer-most layer) Paper work to place the order is in progress. JAEA also contribute to the project. RIKEN: the fixed cost + 3 sensors. JAEA: 2 sensors Prototype sensors will be available by the end of JFY We need to start R&D for ROC soon PHENIX group made request for silicon tracker electronics to BNL-internal R&D fund

Time line of R&D 2014 2015 2016 year month Sensor (S2) prototype Sensor (S2) prototype 9 10 11 12 1 2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 5 6 7 8 design order/fabrication test S2 sensor preproduction S2 sensor preproduction design(if needed) order/fabrication test ROC/hybrid ROC/hybrid conceptual design layout of ROC fabrication FPGA programming layout of version 2 ROC fabricaiton of ver2 ROC test FEM test FEM design/layout fabrication FPGA programming ROC(w/o sensor) test S2 Silicon module S2 Silicon module assembly bench test assembly (2nd) test (2nd) S2 Ladder and stave S2 Ladder and stave design stave fabrication ladder assembly fixture assembly (half ladder) assembly (full ladder) test bus test bus design fabrication S1ladder chain test S1ladder chain test half ladder chain test full ladder chain test Sensor (S1) prototype Sensor (S1) prototype design order fabrication delivery test S1 Silicon module S1 Silicon module assembly bench test S1 ladder S1 ladder ladder assembly fixture ladder assembly S1 ladder chain test S1 ladder chain test chain test

Summary sPHENIX needs a large silicon trakcer We propose to add three layers of strip layers outside of re-configured VTX for sPHENIX The detector requires large amount of silicon sensor (~10m**2) R&D of the silicon sensor has started