Next Version Development for AlphaRad4 Sensor Front-End

In this project, the goal is to create the next version of the AlphaRad4 sensor front-end system by modifying the AlphaRad3 front-end to work with the sensors from AlphaRad4. The project involves various functional and electrical specifications, including gain ranges, comparators, counters, and different sensor versions with specific input characteristics. The design involves changes in the analog and digital parts, bias block, front-end DAC monitor, preamplifier, shaper, comparator, and more, aiming to enhance sensor performance.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

AlphaBeast Rachid & Maciek 02-03.2022 1

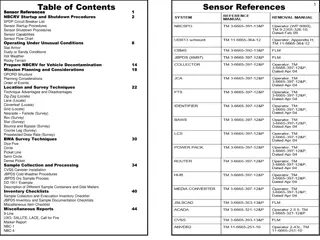

Requirements Goal: Make next version of the AlphaRad4 sensors Problem: No access to the design (schematic) Solution: Modify the front-end of AlphaRad3 to work with sensor from AlphaRad4 (layout available) Front-end specifications : Functional: 2 gain ranges (low, high) 3 comparators + counters 6 versions of the sensor with different input diodes (sensor part done by A.Dorokhov) Electrical: Input capacitance ~50 pF Hit rate 20 s => 50kHz Input charge: I range = 400k e-; II range = 1600k e- 2

TOP Sensor Between the 6 versions only the Sensor part changes Analog part Digital part Pads 3

Analog part Bias Block Front-End DAC Monitor 4

Front End Cdet a chang e M me topologie qu avant mais avec des designs de blocs diff rents Sorties : pour le r glage et le debugging 5

Pramplificateur 2 gains : G0 et 4 G0 2 sorties ind pendantes: 1 vers le shaper et l autre pour le test Adaptation de la 2i me sortie pour utiliser le m me suiveur que le shaper 6

Shaper Filtre passe bande Gain fixe tension mode commun r glable 7

Comparateur Structure avec contre- r action positive Plus sensible moins d offset (voir simulation MC) 8

Linarit intgrale du Pramplificateur faible gain Jusqu 1,6Me Grand gain Jusqu 400Ke 9

Linarit intgrale du shaper Grand gain Jusqu 400Ke faible gain Jusqu 1,6Me 10

Comparateur PFB (Positif Feed Back):Notre proposition OL (Open loop): Ancien comparateur 11

Bias block Bandgap Current DAC 1x Voltage DAC 3 x Voltage threshold DAC (smaller range) 3x IREF_external in case bandgap not working All the control signals come from the Digital Part Bandgap corners Current DAC Voltage DAC Vthreshold_scan Vthreshold_baseline Vbase=127 Vbase=0 12

DAC Monitor 7 inputs and 1 buffered output DAC selection with the Digital Part 13

Padring Digital Power Analog 6 inputs 2 outputs 1 in-out (I2C SDA) Analog VDDA (2.5V) Digital VDD (3.0V) Input IREF_ext Outputs Detector, Preamp, Shaper, DAC_Monitor Clamp pad ESD protection 14

Digital Part Block provides the Command Decoder functionality SPI and I2C protocols Code provided by S.Higueret Debugged and corrected by M.Kachel Technology does not provide files for QRC => SPEF file created in Calibre and used for the SignOff analysis (SpefIn command) 15

Validation Methods Analog Design - Parametric Simulations for linearity - Monte Carlo simulations - for dispersion Digital Design - Simulation of VHDL code - Simulation of generated schematic -> After Synthesis + P&R Mixed simulations - Digital Part (schematic) + Analog part with PADS (extracted) 16

Final Mixed Simulation SPI commands Set all the DACs SPI commands Read back Counter values Injection of the charge to the detector (500k, 1M, 1.5M e-) Comparators responding 17

Summary Adaptation of AlphaRad3 for sensing part of AlphaRad4 Design of the bandgap + DACs Synthesis and P&R of the Digital Part Layout and verification of the TOP (DRC+LVS) Mixed mode simulations after extraction 18