Title of Presentation

Explore essential guidelines for creating impactful presentations in the field of VLSI Technology, covering slide format requirements, font size rules, and presentation flow tips. Ensure your presentation stands out at the 2023 Symposium on VLSI Technology and Circuits.

11 views • 23 slides

Open-Source General Partitioning Multi-Tool for VLSI Physical Design

An open-source tool called TritonPart offers a constraints-driven approach for general partitioning in VLSI physical design. It replaces hMETIS and is integrated with OpenROAD, providing features like multi-way partitioning and embedding-aware techniques. TritonPart shows significant improvements ov

4 views • 20 slides

Effective Presentation Guidelines for IEEE VLSI Symposium 2024

Create a successful presentation for the 2024 IEEE VLSI Symposium by following these guidelines: Format your slides to a widescreen layout with landscape orientation. Avoid corporate logos and use white backgrounds with dark text. Include presenter and coauthors' names, titles, and affiliations on t

2 views • 25 slides

Guidelines for Effective Presentations at 2020 VLSI Technology Symposium

Create impactful presentations for the 2020 VLSI Technology Symposium by following guidelines on slide format, font sizes, and content layout. Ensure your slides are concise, visually appealing, and focused on key concepts. Embrace simplicity, use simple diagrams, avoid complex equations, and rehear

2 views • 17 slides

VLSI Technology and Its Advantages

Very Large Scale Integration (VLSI) is the process of integrating hundreds of thousands of transistors onto a single microchip, revolutionizing the design and performance of electronic circuits. VLSI offers numerous advantages such as reduced circuit size, cost-effectiveness, increased operating spe

0 views • 15 slides

Online Vlsi Training Institutes In Hyderabad

Transform your career with the most exceptional online VLSI training from Takshila-vlsi.com, the premier institute in Hyderabad. Enrol now to unleash your full potential!

6 views • 1 slides

Dynamic Voltage and Frequency Scaling in Advanced VLSI

Explore the concepts of Dynamic Voltage and Frequency Scaling (DVFS) in Advanced VLSI design. Learn about the impact on clocking, STA, and testing, as well as considerations for selecting the right voltage and frequency settings. Discover how controlling voltage affects power consumption and computa

0 views • 51 slides

Introduction to VLSI CAD and Discrete-Event Simulation at Tufts University

This course introduces students to event-oriented simulation, building virtual models, and validating designs through simulation. It covers the importance of simulation in testing and refining designs before implementation. Examples include simulating VLSI networks and exploring the use of discrete-

0 views • 32 slides

Centre of Excellence in Signal Processing Activities and Progress Report

Broad areas of signal processing activities at the Centre of Excellence in Signal Processing include audio, speech, language, medical image processing, computer vision, wireless communications, and machine learning. The center focuses on addressing various challenges in audio/speech recognition, emo

0 views • 17 slides

Machine Learning of Interconnect Coupling Delay and Transition Effects

This research paper explores the use of machine learning to study interconnect coupling delay and transition effects in VLSI design. It discusses the challenges of calibrating non-SI to SI timing reports, the impact of clock period adjustments on path slack, and the complexities involved in the cali

0 views • 32 slides

Integrated Circuits: Fabrication and Packaging Technology

Integrated circuits are fabricated on silicon wafers using a photographic process. The resolution of this process determines the number of devices that can be integrated onto a single chip. After fabrication, the wafer is tested, diced, and functional die are packaged using aluminum or gold wires. T

1 views • 11 slides

High-Performance Gate Sizing with Signoff Timer: VLSI Design Challenges

This study delves into the intricate realm of gate sizing in VLSI design, focusing on optimizing power and delay through effective approaches and addressing challenges such as interconnect delay, inaccurate internal timers, and critical paths. Previous gate sizing techniques are evaluated, and a met

1 views • 34 slides

Static Timing Analysis in Advanced VLSI Design

Static timing analysis is a crucial aspect of VLSI design, helping predict chip performance before fabrication. This article explores the importance of static timing analysis, its effectiveness, and the limitations of dynamic simulation tools like SPICE. Learn about the challenges in testing critica

0 views • 76 slides

Rectangular Dissections and Edge-Flip Chains in Lattice Triangulations

Explore equitable rectangular dissections and their applications in VLSI layout, graph mapping, and combinatorial problems in this scholarly work by Dana Randall from Georgia Institute of Technology. Discover the concept of partitioning an n x n lattice region into n2/a rectangles or areas where cor

0 views • 32 slides

Comprehensive Overview of Fault Modeling and Fault Simulation in VLSI

Explore the intricacies of fault modeling and fault simulation in VLSI design, covering topics such as testing philosophy, role of testing in VLSI, technology trends affecting testing, fault types, fault equivalence, dominance, collapsing, and simulation methods. Understand the importance of testing

0 views • 59 slides

Advanced VLSI - Dark Silicon and Power Management Challenges

Explore the complexities of VLSI design including the concept of dark silicon and the challenges of power management in modern microprocessors. Delve into strategies such as conditional clocking and DVFS to address these issues in the ever-evolving field of semiconductor technology.

0 views • 17 slides

Effective Electronic Presentation Guidelines for VLSI Test Symposium

Comprehensive guide for creating impactful electronic presentations at the 2019 VLSI Test Symposium. Covers presentation specifications, best practices, and tips to engage a technical expert audience effectively. Emphasizes concise content, visual clarity, high contrast, limited text, and smooth tra

0 views • 17 slides

vlsi physical design

Unleash the potential of VLSI physical design with Takshila-vlsi.com. Elevate your career and skills with our comprehensive courses and expert guidance.\n\n\/\/ \/product\/physical-design\/

2 views • 1 slides

asic design course online

Learn how to unlock your full potential in ASIC design with the online course offered by Takshila-vlsi.com. Take your career to new heights by learning from industry experts.\n\n\/\/ \/product\/asic-verification\/

3 views • 1 slides

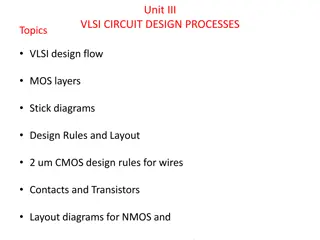

Stick Diagrams in VLSI Circuit Design

Stick diagrams in VLSI design help visualize the layout of components on silicon by capturing topography and layer information through color codes or monochrome encoding. They serve as an interface between symbolic circuits and actual layouts, facilitating the planning of layout and routing while de

0 views • 27 slides

VLSI Design Methodologies and Layout Rules: A Comprehensive Overview

This detailed content provides an in-depth exploration of VLSI design methodologies and layout rules, focusing on topics such as standard cell layout methodology, transistor dimensions, design rules for n-well process, and more. The information covers important aspects like minimum widths, spacings,

0 views • 35 slides

Defect Characterization and Testing of Skyrmion-Based Logic Circuits at IEEE VLSI Test Symposium 2021

With CMOS devices nearing quantum-mechanical limits, magnetic skyrmions offer a promising solution for next-generation spintronic logic devices and memories. This presentation at the IEEE VLSI Test Symposium 2021 delves into defect characterization and testing of skyrmion-based logic circuits. It co

0 views • 19 slides

Basic Hardware Verification Flow

This content delves into the significance of verification in hardware design, emphasizing the need for meticulous code review, skilled engineers, and comprehensive testing practices. It explores the Universal Verification Methodology (UVM) and various effective protocols for ensuring robust verifica

0 views • 54 slides

VLSI Channel Routing

Explore VLSI channel routing challenges, types of VLSI channels, and constraints involved. Learn about graph problems like Minimum Clique Cover and their application in VLSI channel routing.

0 views • 22 slides

Introduction to VLSI Design and Sequential Circuits

This content introduces the basics of VLSI design and sequential circuits, covering topics such as memory elements, latches vs. registers, timing definitions, and standard memory elements. It elaborates on the functionality of sequential circuits and explains concepts like bistable logic devices, mu

0 views • 32 slides