Universal Two-Qubit Computational Register for Trapped Ion Quantum Processors

Universal two-qubit computational register for trapped ion quantum processors, including state preparation, gates, and benchmarking. The experimental setup and results are discussed.

0 views • 14 slides

Apache MINA: High-performance Network Applications Framework

Apache MINA is a robust framework for building high-performance network applications. With features like non-blocking I/O, event-driven architecture, and enhanced scalability, MINA provides a reliable platform for developing multipurpose infrastructure and networked applications. Its strengths lie i

3 views • 13 slides

Towards Single-Event Upset Detection in Hardware Secure RISC-V Processors

This research focuses on detecting single-event upsets (SEUs) in hardware-secure RISC-V processors in radiation environments, such as high-energy physics and space applications. Motivated by the potential data errors, unpredictable behavior, or crashes caused by SEUs, the study explores fault inject

3 views • 17 slides

Modeling and Generation of Realistic Network Activity Using Non-Negative Matrix Factorization

The GHOST project focuses on the challenges of modeling, analyzing, and generating patterns of network activity. By utilizing Non-Negative Matrix Factorization (NMF), realistic network activity patterns can be created and injected into live wireless networks. Understanding and predicting user behavi

4 views • 28 slides

Understanding Superscalar Processors in Processor Design

Explore the concept of superscalar processors in processor design, including the ability to execute instructions independently and concurrently. Learn about the difference between superscalar and superpipelined approaches, instruction-level parallelism, and the limitations and design issues involved

0 views • 55 slides

Understanding Computer Architecture: A Comprehensive Overview by Prof. Dr. Nizamettin AYDIN

Explore the realm of computer architecture through the expertise of Prof. Dr. Nizamettin AYDIN, covering topics like RISC characteristics, major advances in computers, comparison of processors, and the driving force for CISC. Delve into the evolution of processors, register optimization, and the tra

0 views • 42 slides

Understanding Multicore Processors: Hardware and Software Perspectives

This chapter delves into the realm of multicore processors, shedding light on both hardware and software performance issues associated with these advanced computing systems. Readers will gain insights into the evolving landscape of multicore organization, spanning embedded systems to mainframes. The

0 views • 36 slides

Introduction to Intel Assembly Language for x86 Processors

Intel Assembly Language is a low-level programming language designed for Intel 8086 processors and their successors. It features a CISC instruction set, special purpose registers, memory-register operations, and various addressing modes. The language employs mnemonics to represent instructions, with

2 views • 12 slides

Understanding Traffic Engineering Analysis in Telecommunication Networks

Traffic engineering analysis in telecommunication networks involves determining the network's capacity to carry traffic with a loss probability. Blocking probability, which is a key design concern, is influenced by various elements such as switching devices, digit receivers, call processors, and tru

1 views • 50 slides

Network Compression Techniques: Overview and Practical Issues

Various network compression techniques such as network pruning, knowledge distillation, and parameter quantization are discussed in this content. The importance of pruning redundant weights and neurons in over-parameterized networks is highlighted. Practical issues like weight pruning and neuron pru

0 views • 37 slides

Understanding Shared Memory Systems in Computer Architecture

Shared memory systems in computer architecture allow all processors to have direct access to common physical memory, enabling efficient data sharing and communication among processors. These systems consist of a global address space accessible by all processors, facilitating parallel processing but

0 views • 19 slides

Understanding Computer System Architectures

Computer systems can be categorized into single-processor and multiprocessor systems. Single-processor systems have one main CPU but may also contain special-purpose processors. Multiprocessor systems have multiple processors that share resources, offering advantages like increased throughput, econo

2 views • 25 slides

Understanding System Management Mode (SMM) in x86 Processors

System Management Mode (SMM) is a highly privileged mode in x86 processors that provides an isolated environment for critical system operations like power management and hardware control. When the processor enters SMM, it suspends all other tasks and runs proprietary OEM code. Protecting SMM is cruc

1 views • 26 slides

Network Slicing with OAI 5G CN Workshop Overview

Overview of Network Slicing with OAI 5G CN workshop focusing on the crucial role of network slicing in realizing the service-oriented 5G vision. This workshop covers topics like multiple logical networks creation on shared infrastructure, different types of network slices, preparation and instantiat

1 views • 6 slides

PowerPC Architecture Overview and Evolution

PowerPC is a RISC instruction set architecture developed by IBM in collaboration with Apple and Motorola in the early 1990s. It is based on IBM's POWER architecture, offering both 32-bit and 64-bit processors popular in embedded systems. The architecture emphasizes a reduced set of pipelined instruc

2 views • 13 slides

Contrasting RISC and CISC Architectures

Contrasting RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing) architectures, the images and descriptions elaborate on their advantages and disadvantages, with a focus on multiplying two numbers in memory using a CISC approach. CISC processors aim to complete tasks

0 views • 35 slides

Understanding Snort: An Open-Source Network Intrusion Detection System

Snort is an open-source Network Intrusion Detection System (NIDS) developed by Cisco, capable of analyzing network packets to identify suspicious activities. It can function as a packet sniffer, packet logger, or a full-fledged intrusion prevention system. By monitoring and matching network activity

0 views • 23 slides

Understanding ARM RISC Design Philosophy and Its Impact

Delve into the world of ARM processors, exploring the RISC design philosophy that underpins their efficiency and widespread application. Learn about key principles, compare RISC with CISC, and discover how ARM's simplicity, orthogonality, and efficient architecture contribute to its dominance in mob

0 views • 12 slides

Design and Implementation of Shifters in ALU for Single-Cycle Processors

The detailed discussion covers the construction of a multifunction Arithmetic Logic Unit (ALU) for computer processors, specifically focusing on the design and implementation of shifters. Shift operations such as SLL, SRL, SRA, and ROR are explained, with insights into shifting processes and data ex

0 views • 5 slides

Transportation Network Modeling and Analysis with C.Coupled SE Platform

This content outlines the features and functionalities of the C.Coupled SE Platform (CSET Platform) developed by the Connetics Transportation Group. It covers aspects such as interface design, inputs merging, purposes, platform development using Cube, TAZs merging, and network attributes. The platfo

0 views • 11 slides

k-Ary Search on Modern Processors

The presentation discusses the importance of searching operations in computer science, focusing on different types of searches such as point queries, nearest-neighbor key queries, and range queries. It explores search algorithms including linear search, hash-based search, tree-based search, and sort

0 views • 18 slides

Enhancing I/O Performance on SMT Processors in Cloud Environments

Improving I/O performance and efficiency on Simultaneous Multi-Threading (SMT) processors in virtualized clouds is crucial for maximizing system throughput and resource utilization. The vSMT-IO approach focuses on efficiently scheduling I/O workloads on SMT CPUs by making them "dormant" on hardware

0 views • 31 slides

Dynamic Load Balancing on Graphics Processors: A Detailed Study

In this comprehensive study by Daniel Cederman and Philippas Tsigas from Chalmers University of Technology, the focus is on dynamic load balancing on graphics processors. The research delves into the motivation, methods, experimental evaluations, and conclusions related to this critical area. It cov

0 views • 57 slides

Scaling Multi-Core Network Processors Without the Reordering Bottleneck

This study discusses the challenges in packet ordering within parallel network processors and proposes solutions to reduce reordering delay. Various approaches such as static mapping, single SN approach, and per-flow sequencing are explored to optimize processing efficiency in multi-core NP architec

0 views • 22 slides

Hardware Configurations for Project Cysera by Zoebir Bong

This document outlines proposed hardware configurations for Project Cysera drafted by Zoebir Bong. It includes options from Dell and Lenovo servers with both remote and local data storage solutions. Each configuration specifies server models, network switches, processors, memory, storage drives, net

0 views • 8 slides

Meridian: An SDN Platform for Cloud Network Services

Meridian is an SDN platform developed by Mohammad Banikazemi, David Olshefski, Anees Shaikh, John Tracey, and GuohuiWang at IBM T. J. Watson Research Center. The platform focuses on providing cloud network services efficiently. It encompasses an architecture that enables faster and more convenient n

0 views • 21 slides

- Understanding Exceptions in Modern High-Performance Processors

- Overview of exceptions in pipeline processors, including conditions halting normal operation, handling techniques, and example scenarios triggering exception detection during fetch and memory stages. Emphasis on maintaining exception ordering and performance analysis in out-of-order execution proc

0 views • 28 slides

Understanding Interrupt Processing Sequence in X86 Processors

X86 processors have 256 software interrupts, functioning similarly to a CALL instruction. When an INT n instruction is executed, the processor follows a sequence involving pushing the flag register, clearing flags, finding the correct ISR address, and transferring CPU control. Special interrupts lik

0 views • 10 slides

Understanding Shared Memory, Distributed Memory, and Hybrid Distributed-Shared Memory

Shared memory systems allow multiple processors to access the same memory resources, with changes made by one processor visible to all others. This concept is categorized into Uniform Memory Access (UMA) and Non-Uniform Memory Access (NUMA) architectures. UMA provides equal access times to memory, w

0 views • 22 slides

Understanding Network Analysis: Whole Networks vs. Ego Networks

Explore the differences between Whole Networks and Ego Networks in social network analysis. Whole Networks provide comprehensive information about all nodes and links, enabling the computation of network-level statistics. On the other hand, Ego Networks focus on a sample of nodes, limiting the abili

0 views • 31 slides

Should Ghana Provide Discounts on Cocoa Beans for Local Processors? A Case Study

Ghana's cocoa sector plays a significant role in the country's economy, yet less than 25% of cocoa beans are processed locally, limiting its market share. This case study explores the impact of local processing on Ghana's cocoa industry and discusses the dilemma of value addition. The question of wh

0 views • 14 slides

Understanding Shared Memory Coherence, Synchronization, and Consistency in Embedded Computer Architecture

This content delves into the complexities of shared memory architecture in embedded computer systems, addressing key issues such as coherence, synchronization, and memory consistency. It explains how cache coherence ensures the most recent data is accessed by all processors, and discusses methods li

0 views • 47 slides

Constructive Computer Architecture: Multistage Pipelined Processors

Explore the concepts of multistage pipelined processors and modular refinement in computer architecture as discussed by Arvind and his team at the Computer Science & Artificial Intelligence Lab, Massachusetts Institute of Technology. The content delves into the design and implementation of a 3-stage

0 views • 28 slides

Data Hazards in Pipelined Processors: Understanding and Mitigation

Explore the concept of data hazards in pipelined processors, focusing on read-after-write (RAW) hazards and their impact on pipeline performance. Learn strategies to mitigate data hazards, such as using a scoreboard to track instructions and stall the Fetch stage when necessary. Discover how adjusti

0 views • 23 slides

Understanding Instruction Flow Techniques in High-IPC Processors

Explore the intricate processes involved in optimizing instruction flow within high-IPC processors, tackling challenges such as control dependences, branch speculation, and branch direction prediction. Learn about the goals, impediments, branch types, and implementations that shape the efficient exe

0 views • 80 slides

Leveraging Graphics Processors for Accelerating Sonar Imaging via Backpropagation

Utilizing graphics processors to enhance synthetic aperture sonar imaging through backpropagation is a key focus in high-performance embedded computing workshops. The backpropagation process involves transmitting sonar pulses, capturing returns, and reconstructing images based on recorded samples. T

0 views • 18 slides

Network Function Virtualization (NFV) Overview

Network Function Virtualization (NFV) focuses on virtualizing network functions to improve efficiency and reduce costs in network infrastructure. The lecture discusses key readings, devices that compose a network, specialization of devices, benefits of one-device-does-anything approach, and the goal

0 views • 21 slides

Enhancing Network Stability with Network Monitoring Systems

Network monitoring is crucial for efficient management and proactive issue detection in a network environment. Factors influencing an effective network system include choosing the best OEM, SLA agreements, and selecting a reliable System Integrator. Reactive monitoring can lead to financial losses a

0 views • 12 slides

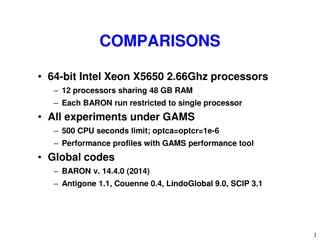

Performance Comparison of Optimization Solvers on Intel Xeon X5650 Processors

Experiment results comparing the performance of optimization solvers (BARON, Antigone, LindoGlobal, SCIP, Couenne) on Intel Xeon X5650 2.66Ghz processors with 48GB RAM. The study includes 369 NLPs from various libraries and an aggregate analysis of 1740 NLPs and MINLPs. Performance profiles generate

0 views • 6 slides

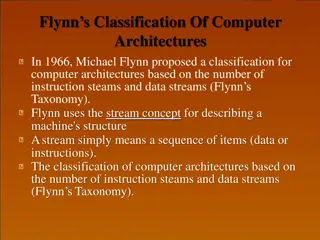

Flynn's Taxonomy: Classification of Computer Architectures

Michael Flynn's 1966 classification divides computer architectures into SISD, SIMD, MISD, and MIMD based on the number of instruction streams and data streams. SISD corresponds to traditional single-processor systems, SIMD involves multiple processors handling different data streams, MISD has multip

0 views • 10 slides