Understanding Computer Organization and Architecture

A computer system is a programmable digital electronics device that processes data as per program instructions to provide meaningful output. It comprises hardware and software components, with hardware being the physical parts and software essential for driving the hardware. Computer organization fo

14 views • 71 slides

Decoupled SMO Architecture Overview

Develop flows showing interaction between SMO modules in the context of open-source architecture using OSC, ONAP, and other code. The objective is to align open-source work with O-RAN trends, improve synergy, reduce duplication, and provide feedback to O-RAN discussions. Related work includes Decoup

4 views • 27 slides

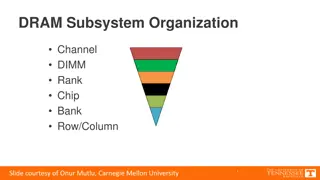

Understanding the Organization of DRAM Subsystem Components

Explore the intricate structure of the DRAM subsystem, including memory channels, DIMMs, ranks, chips, banks, and rows/columns. Delve into the breakdown of DIMMs, ranks, chips, and banks to comprehend the design and functioning of DRAM memory systems. Gain insights into address decoding, row/column

0 views • 16 slides

Overview of RF Architecture and Waveform Assumptions for NR V2X Intra-Band Operation

In the electronic meeting of 3GPP TSG-RAN-WG4, discussions were held on the RF architecture and waveform assumptions for NR V2X intra-band operation in band n79. Various options and recommendations were presented regarding RF architecture, antenna architecture, and waveform definitions for efficient

1 views • 7 slides

Computer Architecture: Understanding SRAM and DRAM Memory Technologies

In the field of computer architecture, SRAM and DRAM are two prevalent memory technologies with distinct characteristics. SRAM retains data as long as power is present, while DRAM is dynamic and requires data refreshing. SRAM is built with high-speed CMOS technology, whereas DRAM is more dense and b

3 views • 38 slides

Understanding Computer Architecture and Organization

Computer architecture and organization are fundamental aspects of computing systems. Computer architecture focuses on the functional design and implementation of various computer parts, while computer organization deals with how operational attributes come together to realize the architectural speci

3 views • 40 slides

Common Software Architecture Anti-Patterns

Anti-patterns in software architecture are commonly occurring solutions to problems that lead to negative consequences. These arise due to insufficient knowledge or experience, misuse of design patterns, and lack of attention to evolving project architecture. Examples include Jumble, Stovepipe, Spag

1 views • 7 slides

Understanding Cache Memory in Computer Architecture

Cache memory is a crucial component in computer architecture that aims to accelerate memory accesses by storing frequently used data closer to the CPU. This faster access is achieved through SRAM-based cache, which offers much shorter cycle times compared to DRAM. Various cache mapping schemes are e

2 views • 20 slides

PowerPC Architecture Overview and Evolution

PowerPC is a RISC instruction set architecture developed by IBM in collaboration with Apple and Motorola in the early 1990s. It is based on IBM's POWER architecture, offering both 32-bit and 64-bit processors popular in embedded systems. The architecture emphasizes a reduced set of pipelined instruc

2 views • 13 slides

Understanding Client-Server Architecture

Client-server architecture is a computing model where a central server hosts and manages resources and services for client computers over a network. There are different types of clients and servers, each with unique characteristics and roles. This architecture offers various advantages and disadvant

3 views • 15 slides

High-Throughput True Random Number Generation Using QUAC-TRNG

DRAM-based QUAC-TRNG provides high-throughput and low-latency true random number generation by utilizing commodity DRAM devices. By employing Quadruple Row Activation (QUAC), this method outperforms existing TRNGs, achieving a 15.08x improvement in throughput and passing all 15 NIST randomness tests

0 views • 10 slides

SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Processing Using DRAM

SIMDRAM introduces a novel framework for efficient computation in DRAM, aiming to overcome data movement bottlenecks. It emphasizes Processing-in-Memory (PIM) and Processing-using-Memory (PuM) paradigms to enhance processing capabilities within DRAM while minimizing architectural changes. The motiva

2 views • 14 slides

Digital Architecture for Supporting UNICEF's High-Impact Interventions

In an ideal scenario, the digital architecture for children would encompass systems such as Enterprise Architecture, Functional Architecture, and Solution Architecture to support UNICEF's high-impact interventions. It would involve integrated platforms for Health Information Exchange, Supply Chain M

1 views • 19 slides

Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the n

0 views • 43 slides

Dram Shop Act and Premises Liability for Bar and Tavern Owners

Understanding the liabilities and responsibilities of bar and tavern owners under the Dram Shop Act based on the case of Build It and They Will Drink, Inc. v. Strauch. The act outlines exceptions where licensees can be held civilly liable for selling alcohol to minors or visibly intoxicated individu

0 views • 12 slides

Progress of Network Architecture Work in FG IMT-2020

In the Network Architecture Group led by Namseok Ko, significant progress has been made in defining the IMT-2020 architecture. The work has involved gap analysis, draft recommendations, and setting framework and requirements. Phase 1 focused on identifying 19 architectural gaps, such as demands for

1 views • 11 slides

Improving GPGPU Performance with Cooperative Thread Array Scheduling Techniques

Limited DRAM bandwidth poses a critical bottleneck in GPU performance, necessitating a comprehensive scheduling policy to reduce cache miss rates, enhance DRAM bandwidth, and improve latency hiding for GPUs. The CTA-aware scheduling techniques presented address these challenges by optimizing resourc

0 views • 33 slides

Enhancing Multi-Node Systems with Coherent DRAM Caches

Exploring the integration of Coherent DRAM Caches in multi-node systems to improve memory performance. Discusses the benefits, challenges, and potential performance improvements compared to existing memory-side cache solutions.

0 views • 28 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

0 views • 48 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Understanding RowPress: A New Read Disturbance Phenomenon in Modern DRAM Chips

Demonstrating and analyzing RowPress, a novel read disturbance phenomenon causing bitflips in DRAM chips. Different from RowHammer vulnerability, RowPress showcases effective solutions on real Intel systems with DRAM chips.

0 views • 46 slides

Managing DRAM Latency Divergence in Irregular GPGPU Applications

Addressing memory latency challenges in irregular GPGPU applications, this study explores techniques like warp-aware memory scheduling and GPU memory controller optimization to reduce DRAM latency divergence. The research delves into the impact of SIMD lanes, coalescers, and warp-aware scheduling on

0 views • 33 slides

Panopticon: Complete In-DRAM Rowhammer Mitigation

Despite extensive research, DRAM remains vulnerable to Rowhammer attacks. The Panopticon project proposes a novel in-DRAM mitigation technique using counter mats within DRAM devices. This approach does not require costly changes at multiple layers and leverages existing DRAM logic for efficient miti

0 views • 17 slides

Proposed Way Forward for Service-Oriented Architecture (SOA) in Space Missions

Proposed establishment of a Working Group by the CESG to develop a Service-Oriented Architecture (SOA) framework for space mission operations within the CCSDS. The focus includes identifying services, use cases, architecture definitions, and business cases to enhance CCSDS-wide interoperability and

0 views • 7 slides

Understanding DRAM Errors: Implications for System Design

Exploring the nature of DRAM errors, this study delves into the causes, types, and implications for system design. From soft errors caused by cosmic rays to hard errors due to permanent hardware issues, the research examines error protection mechanisms and open questions surrounding DRAM errors. Pre

0 views • 31 slides

Introduction to Y86 Instruction Set Architecture

Y86 Instruction Set Architecture is a simplified pseudo-language based on x86 (IA-32) architecture. It involves implementing the Fetch-Decode-Execute cycle, where instructions are fetched from memory, decoded, and executed. The Y86 ISA offers a simpler set of instructions and formats compared to x86

0 views • 25 slides

Transparent Hardware Management of Stacked DRAM for Memory Systems

Explore the innovative use of stacked DRAM as Part of Memory (PoM) to increase overall memory capacity and eliminate duplication. The system involves OS-managed PoM, challenges, and the potential of hardware-managed PoM to reduce OS-related overhead. Learn about the practical implications and evalua

0 views • 24 slides

Challenges and Solutions in Memory Hierarchies for System Performance Growth

The evolution of memory scaling poses challenges for system performance growth due to limitations in memory hierarchy, capacity gaps, and DRAM scaling obstacles. The need for alternative technologies and architectural support to address these challenges is highlighted, focusing on reducing latency,

0 views • 23 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

0 views • 37 slides

Understanding Power Consumption in Memory-Intensive Databases

This collection of research delves into the power challenges faced by memory-intensive databases (MMDBs) and explores strategies for reducing DRAM power draw. Topics covered include the impact of hardware features on power consumption, experimental setups for analyzing power breakdown, and the effec

0 views • 13 slides

Exploring Modern Architecture Trends: Expressionism and Bauhaus Movement

Delve into the world of modern architecture trends, focusing on Expressionist architecture in Europe during the early 20th century and the influential Bauhaus movement in Germany. Expressionist architecture emphasized emotional effects through distorted forms inspired by nature, while the Bauhaus sc

0 views • 10 slides

A Software Memory Partition Approach for Eliminating Bank-level Interference in Multicore Systems

Memory requests from different threads can cause interferences in DRAM banks, impacting performance. The solution proposed involves partitioning DRAM banks between threads to eliminate interferences, leading to improved performance and energy savings.

0 views • 32 slides

Enhancing DRAM Performance with ChargeCache: A Novel Approach

Reduce average DRAM access latency by leveraging row access locality with ChargeCache, a cost-effective solution requiring no modifications to existing DRAM chips. By tracking recently accessed rows and adjusting timing parameters, ChargeCache achieves higher performance and lower DRAM energy consum

0 views • 33 slides

Understanding Memory Hierarchy and Different Computer Architecture Styles

Delve into the concepts of memory hierarchy, cache optimizations, RISC architecture, and other architecture styles in embedded computer architecture. Learn about Accumulator and Stack architectures, their characteristics, advantages, and example code implementations. Explore the differences between

0 views • 52 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

Understanding Memory System Design Tradeoffs in Computer Architecture

Explore the complexities of designing a memory system for computer architecture. Delve into the tradeoffs between area, power, and latency, considering the limitations of using only flip-flops, SRAM cells, or DRAM cells. Discover the challenges in creating an efficient memory system that balances st

0 views • 88 slides

CLR-DRAM: Dynamic Capacity-Latency Trade-off Architecture

CLR-DRAM introduces a low-cost DRAM architecture that enables dynamic configuration for high capacity or low latency at the granularity of a row. By allowing a single DRAM row to switch between max-capacity and high-performance modes, it reduces key timing parameters, improves system performance, an

0 views • 42 slides

Locality-Aware Caching Policies for Hybrid Memories

Different memory technologies present unique strengths, and a hybrid memory system combining DRAM and PCM aims to leverage the best of both worlds. This research explores the challenge of data placement between these diverse memory devices, highlighting the use of row buffer locality as a key criter

0 views • 34 slides

Understanding the Impact of On-Die ECC on DRAM Error Characteristics

The BEER project explores how on-die ECC complicates DRAM reliability studies by concealing error characteristics. It aims to uncover the unique ECC function of DRAM chips and infer error locations in error-prone cells. The study highlights the challenges in identifying and correcting bit flips obfu

0 views • 17 slides