Understanding Sequential Circuit Timing and Clock Frequency

Sequential circuit timing is crucial for designing digital systems. The minimum clock period, slack values, clock frequency, and critical paths play key roles in determining the operational speed and performance of sequential circuits. By analyzing flip-flop timing parameters, combinatorial logic delays, and critical paths, designers can optimize clocking strategies for efficient circuit operation.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

ECE 352 Digital System Fundamentals Sequential Circuit Timing Sequential Circuit Timing 1 1

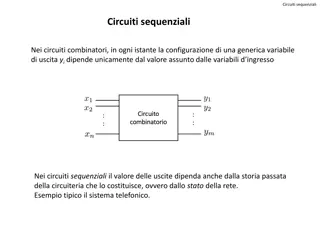

Sequential Circuit Timing How fast can we clock a sequential circuit? D Q FF1 Sequential Circuit Timing A D Q Y FF0 CLK B The answer depends on both the flip-flop timing parameters and the delays of combinational logic elements in the circuit Flip-flop output changes must propagate through the circuit to the flip-flop inputs before the next clock edge 2 2

Minimum Clock Period (tmin) The minimum clock period is the smallest feasible clock period Need time for a change to get out of a flip-flop, through the circuit, and be present at another flip-flop input before the start of the set-up time tp = tmin tmin = tpd+ tcomb+ ts Sequential Circuit Timing CLK tpd tcomb ts tcombis the longest delay of any path between a flip-flop output and a flip-flop input We do NOT consider paths from circuit inputs 3 3

Slack (tslack) The difference between actual clock period (tp) and minimum clock period tslack = tp tmin tp = tmin tp > tmin Sequential Circuit Timing CLK CLK tpd tcomb ts tslack ts How should we interpret slack values? Positive: could run the circuit faster (don t have to!) Negative: trying to run the circuit too fast Zero: running the circuit as fast as it can go Probably not a good idea just in case 4 4

Clock Frequency The clock speed of the sequential circuit Faster clock higher frequency Maximum circuit frequency: fmax = 1 / tmin Actual circuit frequency: f = 1 / tp Remember: Clock period is ps, ns, s, ms, s Frequency is Hz, kHz, MHz, GHz If tmin= 10ns Sequential Circuit Timing fmax = 1 1 1 tmin= 10 ns= 10 8 s=108 Hz=100 MHz 5 5

Critical Path Longest (largest-delay) path that begins and ends at a flip-flop Can begin and end at the same FF! Only the paths that begin and end at a flip-flop Not looking at the path(s) from the circuit input(s) Sequential Circuit Timing D1 = A Q0 D Q FF1 Note: the circuit s asynchronous reset is not shown here for simplicity Y = Q0 B A D Q Y FF0 CLK B D0 = Q1( A+ Q0) 6 6

Do Not Memorize Parameter Values! Do not memorize the values of timing parameters you are about to see Actual timing parameters depend on the technology used and the design of the structure Logic manufacturers have to specify these for their products You will be given timing parameter values for any question asked in this class Sequential Circuit Timing You do have to know the meaning of each parameter (propagation delay, set-up time, etc.) 7 7

Critical Path Example 1 Find tmin, given the following delays (in ns): tpd = 3, ts = 2, tNOT = 2, tAND = 3, tOR = 4, tXOR = 6, tXNOR = 8 Sequential Circuit Timing 6 Compare all FF FF paths to find the max combinational delay tcomb D Q FF1 2 3 A D Q 4 8 Y FF0 CLK B tmin = tpd + tcomb + ts 8 8

Critical Path Example 1 Find tmin, given the following delays (in ns): tpd = 3, ts = 2, tNOT = 2, tAND = 3, tOR = 4, tXOR = 6, tXNOR = 8 Path 1 Sequential Circuit Timing 6 Compare all FF FF paths to find the max combinational delay tcomb D Q FF1 Path 3 2 3 A D Q 4 8 Y FF0 Path 2 CLK B tcomb(path1) = tXOR = 6ns tcomb(path2) = tOR + tAND = 7ns tcomb(path3) = tAND = 3ns tmin = tpd + tcomb + ts = 3 + 7 + 2 = 12ns 9 9

Critical Path Example 2 Find tmin, given the following delays (in ns): tpd = 3, ts = 2, tNOT = 2, tAND = 3, tOR = 4, tXOR = 9, tXNOR = 8 Path 1 Sequential Circuit Timing 9 Compare all FF FF paths to find the max combinational delay tcomb D Q FF1 Path 3 2 3 A D Q 4 8 Y FF0 Path 2 CLK B tcomb(path1) = tXOR = 9ns tcomb(path2) = tOR + tAND = 7ns tcomb(path3) = tAND = 3ns tmin = tpd + tcomb + ts = 3 + 9 + 2 = 14ns 10 10

Critical Path Pitfall Input paths should NOT be considered when computing fmax = 1/tmin We only care about FF FF delays Sequential Circuit Timing D Q paths not used to calculate tmin FF1 A D Q Y FF0 CLK B 11 11

Hold Time Violations Hold time can be violated if a change at a flip-flop output can propagate through the circuit to a flip- flop input before the end of the hold time Can occur if th > tpd+ tcomb,min Need to consider only the fastest (least delay) path from flip-flop output to flip-flop input Most flip-flops are now designed so th < tpd In that case, hold time cannot be violated even when a flip-flop output is directly connected to a flip-flop input Sequential Circuit Timing A D Q D Q D Q Y CLK 12 12

Synchronization There can be problems when inputs to a synchronous circuit change asynchronously Setup/hold time violations if a flip-flop input changes too close to the active clock edge Unequal delay may cause input changes to show up in different cycles instead of in the same cycle Synchronizing input signals In general, all inputs to a synchronous circuit must be synchronized(aligned to the circuit s clock) unless they come from another synchronous circuit using the same clock Sequential Circuit Timing 13 13

Synchronization Problem Assume that in the FSM below the next state is 002 if A=0 and 112 if A=1 Sequential Circuit Timing 10 D Q 2ns FF1 1 0 logic A 0 8ns D Q FF0 CLK Suppose signal A changes from 0 1 at 5ns before the positive clock edge what happens? Assume tS and tH are not violated 14 14

Adding a Synchronizer To solve the problem, add a flip-flop to synchronize the changes in A to the clock. Sequential Circuit Timing synchronizer D D Q Q 2ns 2ns FF1 FF1 logic logic D Q A A 8ns 8ns D D Q Q FF0 FF0 CLK CLK Now, input changes can only propagate to FF1/FF0 immediately after a clock edge, so we can guarantee correct operation except 15 15

Metastability Synchronizer input could change at any time What if the change violates the synchronizer FF s setup/hold time requirements? Input transition may not affect FF output (not so bad ) Input transition may induce a metastable state that occurs with some probability (very bad ) A metastable state persists for a probabilistic time Eventually settles at 1 or 0 non-deterministic Mitigating metastability A chain of FFs reduces the probability These problems can NOT be completely eliminated! Sequential Circuit Timing 16 16

More Asynchronous Issues Don t use flip-flop asynchronous preset/clear inputs for anything other than the global reset The flip-flops respond immediately to these inputs, so they should never be driven by signals within the synchronous circuit Sequential Circuit Timing Synchronous design provides a set of rules that make the design process easier! We need to be aware of asynchronous issues when interfacing with other circuits We need to be aware of design pitfalls that can cause asynchronous behavior in our circuits 17 17

2-Bit Counter D Q D RST Q CLR Sequential Circuit Timing +1 +1 D Q D RST Q CLR Y Y CLK CLK 0 1 2 0 1 2... NEVER drive the flip-flop s asynchronous preset/clear inputs with your synchronous circuit. They are only to be used for a power-on reset. 0 1 0 1 0... 18 18

Danger Ahead: Clock Gating May be tempting to use logic to change or disable the clock signal used by one or more FFs But the gating logic is likely to cause incorrect behavior! Our design methodology depends on the clock edge arriving to all FFs simultaneously Lots of research and money invested in design tools to ensure this is true Delays of clock gating logic make it not true Clock gating is used extensively in low-power circuit design But ONLY by VERY EXPERIENCED designers! Sequential Circuit Timing 19 19

ECE 352 Digital System Fundamentals Sequential Circuit Timing Sequential Circuit Timing 20 20