MPC5748G Cut 2.0/3.0 Errata Summary Comparison

This presentation compares the errata summary between MPC5748G cut 2.0 and cut 3.0 versions. It highlights various discrepancies and issues identified in both versions, ranging from potential sequencing issues to pad control problems. The comparison sheds light on the differences in erratum across these two versions of the MPC5748G, providing valuable insights for users and developers.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

MPC5748G (Calypso6M) Cut 2.0/3.0 Comparison Summary Version 1 20, July 2016 EXTERNAL USE

Introduction The purpose of this presentation is to compare MPC5748G cut 3.0 to MPC5748G cut 2.0 MPC5748G Version/Cut 2.0 SIUL2_MIDR1 [MAJOR_MASK] 0x1 Mask ID JTAG ID 1N81M 0x0988_101D 3.0 0N78S 0x2 0x0988_201D Calypso6M family part numbers: MPC5746G, MPC5747G, MPC5748G, MPC5747C, MPC5748C, EXTERNAL USE 1

MPC5748G errata summary The following erratum were published in MPC5748G cut 2.0 errata document Revision 2 (released June 2016) Find on nxp.com (search MPC5748G_1N81M ) EXTERNAL USE 2

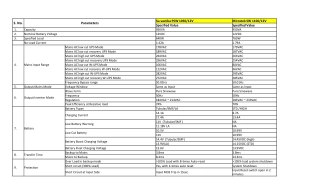

MPC5748G cut 2.0/3.0 errata summary Cut 2.0 1N81M Cut 3.0 0N78S Erratum ID Erratum Description e7885 ENET: Potential sequencing issue with TDAR in Multi-Queue mode YES no e7991 FLASH: Rapid Program or Erase Suspend fail status YES YES e8042 FCCU: EOUT signals are active, even when error out signaling is disabled YES no e8080 LINFlexD: TX pin gets set to High-Z when in IDLE state YES no e8180 HSM: e200z0 Nexus interface DQTAG implemented as variable length field in DQM message YES YES SMPU: Process Identifier region hit determination is not available in debug mode e10214 STCU & HSM: LBIST on devices with HSM enabled can cause stuck in reset ADC: Conversions on an open channel with the presampling feature enabled do not return the expected results e8406 YES no e8714 YES no e8759 FlexCAN: FD frame format not compliant to the new ISO/CD 11898-1: 2014-12-11 YES no e8770 FlexRAY: Missing TX frames on Channel B when in dual channel mode and Channel A is disabled YES YES e8868 WKPU: Wakeup Pads pull-ups cannot be enabled in Standby Mode YES no NEXUS: Mutli core tracing using NEXUS3 gives corrupted traces for the case when the cores are in the ratio of 2:1 e8870 YES no e8871 ME: In STANDBY/LPU STANDBY modes, if FIRC is disabled all 256kB of STANDBY RAM is retained YES no MEMU: After exit from LPU RUN mode, the MEMU_PROT registers are uninitialized which may impact the usage of MEMU e8880 YES no e8883 HSM: Input Output Control enables pad and alternative pad YES no EXTERNAL USE 3

MPC5748G cut 2.0/3.0 errata summary Cut 2.0 1N81M Cut 3.0 0N78S Erratum ID Erratum Description ME: For a supply voltage of greater than 5.3V the MCU may be reset during a LPU_STANDBY to LPU_RUN mode transition Flash: Flash internal regulation mode may lead to power-on-reset when in STANDBY and LPU modes e8898 YES no e8901 YES no e8902 STM: The STM Counter Register will not report count value when TEN is cleared YES no LINFlexD: Inconsistent sync field may cause an incorrect baud rate and the Sync Field Error Flag may not be set e8933 YES YES e8938 LINFlexD: Corruption of Tx data in LIN mode with DMA feature enabled (applicable to LIN1) YES no LINFlexD: Tx through DMA can be re-triggered after abort in LIN/UART modes or can prematurely end on the event of bit error with LINCR2[IOBE] bit being set in LIN mode (applicable only for LIN1) e8939 YES no e9076 FCCU: Fault Collection and Control Unit glitch filter behavior is indeterministic YES no MC_ME and LPU: JTAG TCK pin must be configured to ensure successful exit from STANDBY and LPU modes e9200 YES no e9321 ADC: Conversions may fail if Pre-Sampling is enabled YES no ENET: Not possible to set the entire range of the ENET Timer Compare Capture Register (ENET_TCCR0[TCC] and ENET_TCCR1[TCC]) IAHB: Default programming of Intelligent AHB Gasket pending read optimisation can lead to masters stalling or receiving incorrect or spurious data PFLASH: Calibration remap to flash memory not supported on 16KB and 32KB flash blocks in address range 0x00F90000-0x00FBFFFF e9328 YES no e9335 YES no e9873 YES YES e9978 eMIOS: Unexpected channel flag assertion during GPIO to MCB mode transition YES YES e9995 DSPI0 and DSPI1: Frame transfer does not restart in case of DSI parity error in master mode YES no EXTERNAL USE 4

MPC5748G cut 2.0/3.0 errata summary Cut 2.0 1N81M Cut 3.0 0N78S Erratum ID Erratum Description e9996 DSPI0 and DSPI1: Frame transfer does not restart after DSI frame matches pre-programmed value YES no STCU2: Unexpected STCU self-test timeout can occur when a short functional reset is triggered during execution of online self-test e10103 YES YES e10118 HSM: TRNG can only select FIRC for clock source YES YES e10132 LPU: Mode transition to LPU_STOP or LPU_STANDBY may not complete YES no LPU: LPU_RUN mode system clock must be preconfigured for undivided FIRC prior to LPU_STANDBY entry CMP: Analog Comparator 0 (CMP_0) output state is high-impedance during exit from STANDBY mode e10141 YES YES e10143 YES no e10214 STCU & HSM: LBIST on devices with HSM enabled can cause stuck in reset YES no MC_ME: The transition from DRUN/RUN mode to STANDBY will not complete if a wake-up is triggered in a 50nS window. MC_ME & LPU: The transition between DRUN/RUN mode to STANDBY or DRUN/RUN mode to LPU_RUN may not complete if EXR is asserted. MC_ME & LPU: The transition between DRUN/RUN mode to STANDBY or DRUN/RUN mode to LPU_RUN may not complete if any LVD is asserted or PORST goes low FlexCAN: Transition of the CAN FD operation enable bit may lead FlexCAN logic to an inconsistent state. MC_ME & LPU: The transition between DRUN/RUN mode to STANDBY or DRUN/RUN mode to LPU_RUN may not complete if a reset is asserted. e10323 YES no e10361 YES no e10362 YES no e10368 YES YES e10440 YES no EXTERNAL USE 5

Cut 3.0 errata fixes additional information Cut 2.0 1N81M Cut 3.0 0N78S Erratum ID Erratum Description Separate control for each output: HSM control register: HSM_IOCTL[D0_EN0] enables output of PI[6] HSM_IOCTL[D0_EN1] enables output of PI[7] HSM_IOCTL[D0_EN2] enables output of PD[12] HSM_IOCTL[D0_EN3] enables output of PB[12] HSM control register: HSM_IOCTL[D0_EN0] enables output for both PI[6] & PD[12] HSM_IOCTL[D0_EN1] enables output for both PI[7] & PB[12] HSM: Input Output Control enables pad and alternative pad control e8883 FlexCAN: FD frame format not compliant to the new ISO/CD 11898-1: 2014-12-11 e8759 ISO/WD 11898-1: 2013-12-13 ISO/CD 11898-1: 2014-12-11 Pull-up/down enabled via the WKPU_WIPUER. By default pull-down is selected at SIUL2_MSCRx[PUS] = 0 (set to 1 for pull-up) WKPU: Wakeup Pads pull-ups cannot be enabled in Standby Mode Pull-down enabled via the WKPU_WIPUER e8868 EXTERNAL USE 6

Cut 3.0 added functionality Cut 2.0 1N81M Cut 3.0 0N78S Item Module Description Statistical counters to behave the same as legacy FEC (Fast Ethernet Controller). Statistical counters (ENET_IEEE_R_FRAME_OK and ENET_IEEE_R_OCTETS_OK) do not increment when ENET_RCR[BC_REJ]=1 and ENET_RCR[PROM]=0. Pulse stretching for ENET_TCSR[TMODE] = 4'b1110 or 4'b11X1. Enhancement to Ethernet switch for VLAN. VLAN resolution table allows VLAN ID specific tag removal. NEW_1 Ethernet Not supported Supported NEW_2 Ethernet Not supported Supported NEW_3 EthernetSwitch Not supported Supported When in external regulation mode the PMC uses a counter to delay the exit from a low power mode to ensure the external power supply is ready and stable. By default the counter delay is 1mS. Functionality has been added so that the counter value can be programmed via a DCF record stored in UTEST flash. This allows the low power mode exit time to be optimised based on the specification of the external power supply. If the external power supply remains enabled through the low power mode the delay can be bypassed. PMC (External Voltage Regulator mode) Not supported Delay counter fixed at 1mS NEW_4 Supported EXTERNAL USE 7

BAF Version BAF Version Applicable device: Cut 2.0 1N81M BAF 02.02.00.01 BAF 02.08.00.01 Alpha release for Cut 3.0 (0N78S) Production release for Cut 3.0 (0N78S) (Details will be published in later version of this document, after closure of Alpha release validation) BAF 02.09.xx.xx EXTERNAL USE 8

BAF differences BAF 02.02.00.01 Operation BAF 02.08.00.01 Operation Item Functional Change When the following conditions are true, the BAF will not handle the ECC exception and will force a destructive reset of the SOC. When the following conditions are true, the BAF will handle the ECC exception and will resume the boot header scan in the next boot header location. All conditions must be true: i. A multi-bit ECC error is present in one of the memory locations in list A ii. A multi-bit ECC error is present in a valid BAF boot header location iii. The BAF does not find a valid boot header in a location preceding (ii), thereby forcing a read of location (ii). All conditions must be true: i. A multi-bit ECC error is present in one of the memory locations in list A ii. A multi-bit ECC error is present in a valid BAF boot header location iii. The BAF does not find a valid boot header in a location preceding (ii), thereby forcing a read of location (ii). Improved handling of multiple ECC errors caused by SSCM in BAF during boot header search. BAF_1 List A: 0x0100_0000 - 0x0100_001F 0x0104_0000 - 0x0104_001F 0x0108_0000 - 0x0108_001F 0x010C_0000 - 0x010C_001F 0x0040_4000 - 0x0040_401F 0x00F8_C000 0x00F8_C01F List A: 0x0100_0000 - 0x0100_001F 0x0104_0000 - 0x0104_001F 0x0108_0000 - 0x0108_001F 0x010C_0000 - 0x010C_001F 0x0040_4000 - 0x0040_401F 0x00F8_C000 0x00F8_C01F EXTERNAL USE 9

BAF differences BAF 02.02.00.01 Operation BAF 02.08.00.01 Operation Item Functional Change During BAF operation: - If an error occurs during an HSM access to flash whilst searching for a valid boot header, the error status bit (C55FMC_MCR[ERR]) and error address (C55FMC_ADR[ADDR]) will be updated appropriately. An HSM CPU exception will be triggered. - If an error also occurs during a BAF access to flash whilst searching for a valid boot header, before the HSM exception handler has cleared the error status, the BAF exception handler will read the error address (C55FMC_ADR[ADDR]) associated with the HSM error, rather than the BAF error. During BAF operation: - If an error occurs during an HSM access to flash whilst searching for a valid boot header, the error status bit (C55FMC_MCR[ERR]) and error address (C55FMC_ADR[ADDR]) will be updated appropriately. An HSM CPU exception will be triggered. - If an error also occurs during a BAF access to flash whilst searching for a valid boot header, before the HSM exception handler has cleared the error status, the BAF exception handler will read the error address location in the Z4 core Machine Check Error Registers (MCAR & MCSR) to obtain the address for the BAF error. Improved handling of multiple errors caused by HSM in BAF during boot header search BAF_2 In this case, the BAF cannot handle the error and will force a destructive reset of the SOC. In this case, the BAF will handle the exception and will resume the boot header scan in the next boot header location. During BAF cache invalidation, if the abort condition is reported, the BAF will restart the cache invalidation. During BAF cache invalidation, if the abort condition is reported, the BAF will not handle this. Improved Handling of BAF Cache Invalidation BAF_3 In this scenario, the cache may not be fully invalidated & may contain random data that appears as a valid cache entry. In the case where restarting the cache invalidation does not clear the abort condition, the BAF watchdog will cause a destructive reset of the SOC. EXTERNAL USE 10

BAF differences BAF 02.02.00.01 Operation BAF 02.08.00.01 Operation Item Functional Change The detection of un-correctable ECC error for an instruction located in cache is disabled. In case of such an error the cache will return an errant instruction leading to unknown behaviour. The MCU will boot without applying the DCF records for the following conditions: A multi-bit ECC occurs at the DCF Start Record in UTEST flash (0x0040_0300) during the SSCM scan The Soft DCF Record Start Address (located at 0x0040_00C0) is not 0x0040_0300 During BAF operation, if an error occurs in the instruction cache, the cache controller with either correct the error or automatically invalidate the cache. BAF_4Improved Handling of BAF Instruction- Cache Errors BAF stops application boot if the DCF records are not parsed by SSCM because of multi-bit ECC at DCF Start Record at 0x0040_0300 The BAF checks for a multi-bit ECC at 0x0040_0300 and if detected the BAF will force a destructive reset of the MCU. BAF_5 EXTERNAL USE 11

Revision History Revision Changes Approvers V0 Pre-release of Initial revision (excluding BAF updates) - - - MPC5748G Applications Lead Engineer MPC5748G Design Lead Engineer MPC5748G Systems & Applications Engineering Manager V1 Initial release - - - MPC5748G Applications Lead Engineer MPC5748G Design Lead Engineer MPC5748G Systems & Applications Engineering Manager EXTERNAL USE 12