Understanding Shift Registers: Introduction and Classification

Explore the world of shift registers, including buffer registers, and different modes of operation like serial in/serial out, serial in/parallel out, parallel in/serial out, and parallel in/parallel out. Learn about the construction, operation, and classification of registers in digital systems.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

Topics Introduction Buffer Register Classification of Register Shift Registers and their modes Bidirectional Shift Register Universal Shift Register 1. 2. 3. 4. 5. 6.

Introduction Register is an important application of Flip-Flop. Flip- Flop is a 1 bit memory cell which can be used for storing the digital data. To increase the storage capacity in terms of number of bits, we have to use a group of flip-flop. Such a groups of flip-flop is known as a Register . Thus register is a group of flip-flops. The n-bit register will consist of n number of flip flops.

Buffer Register Constructed by using D flip-flop. We can use any type of edge triggering. But here it is a positive triggered D flip-flop. Operation The data is to be stored is B3B2B1B0 = 1 0 1 0. These bits are connected to each D-Flip-flops. Then the clock is applied and corresponding output will be Q3Q2Q1Q0 = B3B2B1B0 = 1 0 1 0

Buffer Register 4 bits input B0 B3 B1 B2 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK Q0 Q1 Q3 Q2 Outputs

Operation of Buffer Register 4 bits input B0 B3 B1 B2 1 0 0 1 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK 1 0 0 1 Q0 Q1 Q3 Q2 Outputs

Classification of Registers : Mode of operation Serial in serial out Serial in Parallel out Parallel in Serial out Parallel in Parallel out (SISO) (SIPO) (PISO) (PIPO) Shift Right Shift Left

Shift Register Sr. No. Mode Illustrative Diagram Comments Data bits shift from Left to Right by 1 position per clock cycle. SISO (Shift Right) O/P I/P 1. FF3 FF2 FF1 FF0 Data bits shift from Right to Left by 1 position per clock cycle. O/P I/P SISO (Shift Left) FF3 FF2 FF1 FF0 2. I/P All o/p bits are made aval. simult. after 4-clcok pulse FF3 FF2 FF1 FF0 3. SIPO O/P All applied simult and. After 4-clk pulse the required o/p is available serially. i/p bits are I/P 4. PISO O/P FF3 FF2 FF1 FF0

Serial input Serial Output (Shift Left Mode) Din 0 0 0 0 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK Serial Data Output Serial Shift left register Before application of clock let assume all outputs are zero and apply MSB bit of the number to entered to Din. So Din = D0 = 1.

Serial input Serial Output (Shift Left Mode) Apply the clock . On the first falling edge of clock, the FF-0 is SET and the stored data in the register is Q3Q2Q1Q0 = 0 0 0 1 Din 1 1 0 0 0 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK Serial Data Output

Serial input Serial Output (Shift Left Mode) Apply the NEXT bit to Din . So if Din =1. As soon as the next positive edge of the clock hits. FF- 1 will SET and the stored data changes to, Din Q3Q2Q1Q0 = 0 0 1 1 1 1 1 0 0 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK Serial Data Output

Serial input Serial Output (Shift Left Mode) Apply the NEXT bit to Din . So if Din =1. As soon as the next positive edge of the clock hits. FF- 2will SET and the stored data changes to, Din Q3Q2Q1Q0 = 0 1 1 1 1 1 1 0 1 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK Serial Data Output

Serial input Serial Output (Shift Left Mode) Apply the NEXT bit to Din . So if Din =1. As soon as the next positive edge of the clock hits. FF- 3will SET and the stored data changes to, Din Q3Q2Q1Q0 = 1 1 1 1 1 1 1 1 1 Q3 Q0 D3 D0 Q2 Q1 D2 D1 FF-3 FF-0 FF-2 FF-1 CLK Serial Data Output

Summary of shift left operation CLK Q3 Q2=D3 Q1=D2 Q0=D1 Serial input Din = D0 0 0 0 0 0 0 0 1 1 0 0 1 1 1 0 1 1 1 1 1 1 1 1 1

Serial input Serial Output (Shift Right Mode) Din D3 Q3 D2 D1 D0 Q2 Q1 Q0 FF-3 FF-2 FF-1 FF-0 CLK Serial Output

Serial input Parallel Output (SIPO) In this operation the data is entered serially and taken out in parallel. That means first the data is loaded bit by bit. The output are disabled as the loading is taking place. Number of clock cycles required to load a four bits data is 4. Hence the speed of operation of SIPO mode is same as that of SISO mode. Din D0 Q0 D1 D2 D3 Q1 Q2 Q3 FF-0 FF-1 FF-2 FF-3 CLK Q3 Q2 Q0 Q1

Parallel input Parallel Output (PIPO) In this operation the data are entered parallel. The 4-bit binary input B0, B1, B2, B3 is applied to data inputs D0, D1, D2 and D3 respectively of the four flip-flops. As soon as a positive clock edge is applied, the input binary bits will be loaded into the flip-flops simultaneously. The loaded bits will appear simultaneously to the output side. ONLY ONE CLOCK IS ESSENTIAL TO LOAD ALL THE BITS. B0 B1 B2 B3 D0 Q0 D1 D2 D3 Q1 Q2 Q3 FF-0 FF-1 FF-2 FF-3 CLK Q3 Q2 Q0 Q1

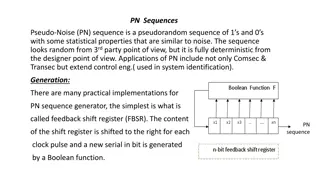

Parallel input Serial Output (PISO) In this operation the data are entered parallel. Output of pervious FF is connected to the input of the next via a combinational circuit. The binary input data B0, B1, B2, B3 is applied through the same the combinational circuit. There are two modes in which this circuit can work namely shift mode or load mode.

B0 B1 B2 B3 Shift/ Load 5 1 3 6 2 4 D0 Q0 D1 D2 D3 Q1 Q2 Q3 FF-0 FF-1 FF-2 FF-3 CLK Serial Data O/P

MODE BIT M M=0 Shift Left M=1 Shift Right Serial Shift Left Input DL Serial Shift Right Input DR 7 3 5 8 4 6 1 2 D3 Q3 D2 D1 D0 Q2 Q1 Q0 FF-3 FF-2 FF-1 FF-0 CLK

4-bits Universal Shift Register Mode Control Register Operation S1 S0 0 0 No change 0 1 Shift Right 1 0 Shift Left 1 1 Parallel load

Applications of shift Register 1. For Temporary data storage. 2. For multiplication and division 3. As a delay line 4. Ring Counter 5. Parallel to serial converter