Improving Qubit Readout with Autoencoders in Quantum Science Workshop

Dispersive qubit readout, standard models, and the use of autoencoders for improving qubit readout in quantum science are discussed in the workshop led by Piero Luchi. The workshop covers topics such as qubit-cavity systems, dispersive regime equations, and the classification of qubit states through

3 views • 22 slides

Understanding FELIX Phase II Run 4 and Versal Prime ACAP Device

Explore the advancements in FELIX Phase II Run 4, leveraging Xilinx Versal Prime ACAP Device, showcased at the 3rd CERN System-on-Chip Workshop. Witness massive improvements in trigger rates, data readout rates, and interactions per bunch crossing. Dive into the hardware details and Versal Prime's c

2 views • 36 slides

SMuRF: SLAC Microresonator RF Readout

SMuRF group at SLAC developed a cutting-edge RF readout system for cryogenic micro-resonators used in research. The system features cold resonators tuned with TES current and a flux ramp to eliminate 1/f noise. Key technical challenges include noise, linearity, wide bandwidth, and computation power.

3 views • 16 slides

Verification Environment for ALTIROC3 ASIC in ATLAS High Granularity Timing Detector

The verification environment for the ALTIROC3 ASIC in the ATLAS High Granularity Timing Detector is crucial for the upgrades in the ATLAS HL-LHC experiment, aiming to improve particle detection performance in the forward region, mitigate pile-up effects, and provide luminosity measurement. The ALTIR

7 views • 26 slides

Modelling and Exploration of Coarse-Grained Reconfigurable Arrays Using CGRA-ME Framework

This content discusses the CGRA-ME framework for modelling and exploration of Coarse-Grained Reconfigurable Arrays (CGRA). It covers the objectives, architecture description, inputs required, and tools included in the framework. CGRA-ME allows architects to model different CGRA architectures, map ap

2 views • 33 slides

Enhancing National Lab Internship Programs for ASIC Design Students

Establishing regular internship programs at National Labs for ASIC design students to bridge the gap between academia and industry. This initiative aims to provide students exposure, on-the-job experience, and advance collaborative projects while enhancing technical expertise and potential job oppor

0 views • 6 slides

Particle Readout System Overview

This presentation covers the Particle Readout System for events happening on August 18, 2024, detailing the system requirements, detectors involved such as the Time Projection Chamber (TPC) and Forward Tracker (FT), monitoring devices like Beam Position Monitors (BPM), as well as the Forward Tracker

0 views • 30 slides

Understanding DAQ Trigger Issues in SoLID Experiment

Explore DAQ trigger challenges faced in the SoLID experiment through examples, including trigger goals, data readout specifics, and experiment setups. Learn about managing high luminosity, reducing data rates, improving signal quality, and handling bottleneck issues for effective data acquisition. D

0 views • 22 slides

Inexpensive Digital Azimuth Readout Challenge by Paul Wade W1GHZ

This challenge calls for creating an inexpensive digital remote readout for azimuth, particularly useful in EME and microwaves. The project involves expertise with microprocessors like PIC, Arduino, Raspberry Pi, etc. The goal is to develop a functional system, share the plans, and the parts expense

0 views • 12 slides

Advancements in Pixel Readout R&D for Large Liquid Argon Time-Projection Chambers

Explore the latest developments in pixel readout research and development for large liquid argon time-projection chambers (LArTPCs) presented by Dan Dwyer at the CYGNUS Collaboration Meeting. Learn about signal characteristics, wire signal ambiguity, challenges in true 3D readout, and the innovative

0 views • 13 slides

Advancements in PET Readout Technology: PETAT1 Time-Sorting Readout ASIC

Cutting-edge PET readout systems now utilize specialized ASICs for data acquisition from SiPMs, eliminating the need for FPGAs and reducing complexity, space requirements, and power consumption. The PETAT1 ASIC, developed by P. Fischer and team at Heidelberg University, enables time-ordered hit data

0 views • 18 slides

Advanced Technologies for Particle Detection and Monitoring

Cutting-edge technology such as HVCMOS RD50-CMOS project along with CaRIBOu and Xilinx ZC706 evaluation board are being employed for precise measurements in E-TCT with passive and active pixel detectors. The development of Radiation Monitor Sensor Boards for ITk, involving sensors like RadFETs and d

0 views • 6 slides

Concept for ALICE Upgrade: Gating Grid by Howard Wieman

The Technical Design Report outlines a plan to use GEM detectors for the TPC readout in ALICE upgrade, addressing issues with positive ion back flow. A modified gating grid design is proposed to block 100% of the back flow while maintaining data rate. The concept involves specific parameters and ope

0 views • 14 slides

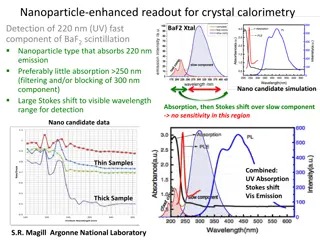

Nanoparticle-Enhanced Readout for Crystal Calorimetry: BaF2 Scintillation Detection

Nanoparticles with specific absorption and emission properties are explored to enhance the readout process for BaF2 crystal calorimetry, focusing on detecting the fast 220nm UV component. The goal is to achieve a large Stokes shift to the visible wavelength range for efficient detection, while minim

0 views • 7 slides

Intensive Study on CsI Crystal Readout by Hamamatsu MPPC

This study presents detailed analysis of a 3x3x18 cm³ CsI crystal readout using a Hamamatsu large area MPPC. Various tests were conducted on the MPPC and electronics setup, including laser pulsing and signal reduction. The results show improved time resolution and slewing correction, enhancing the

0 views • 23 slides

Advances in Nanoparticle-Enhanced Photosensors for UV Light Detection and Quantum Confinement Research

Nanoparticle-enhanced photosensors are being developed by Steve Magill at Argonne National Laboratory for UV light detection, utilizing quantum confinement to enhance electronic and optical properties. Quantum confinement creates discrete energy levels in nanoparticles smaller than the electron wave

0 views • 30 slides

Efficient Virtual Segmentation for Large-scale Detector Systems

Highly segmented detectors with millions to billions of readout channels require a practical approach for simulation and reconstruction. Implementing each channel separately is impractical, necessitating the use of virtual segmentation to define readouts for different detector components. Dependenci

0 views • 11 slides

Advancements in Readout R&D at LNF

The LNF crew, led by Benussi, is engaged in various activities at LNF, including studies on alternative gas mixtures, different GE1/1 gap sizes, material aging, readout optimization, and strips layout. Work is in progress on designing a dedicated PDB readout board for a GEM chamber, alongside improv

0 views • 8 slides

Comparison of Charge Sharing Mechanisms in HERD SCD

This study delves into the analysis of charge sharing mechanisms in the HERD SCD using simulations and experimental data. It explores the impact of coupling capacitors on charge sharing efficiency and readout strip performance under various conditions to enhance signal detection and improve CCE. The

0 views • 21 slides

Advancements in Large-Area 3D Charge Readout for LArTPCs

Demonstrations featuring large-area 3D charge readout for Liquid Argon Time Projection Chambers (LArTPCs) were showcased by Peter Madigan at NorCal HEP-EXchange in December 2018. The challenges of readout in high-rate environments were discussed, along with the potential of pixelated TPCs in 3D LArT

0 views • 13 slides

Understanding VHDL for ASIC Design: A Comprehensive Guide

Explore the world of VHDL for ASIC designs, covering topics such as modeling, simulation, HDLs in digital system design, anatomy of a VHDL model, port identifier modes, and data types. Learn how to define entities and architectures, declare I/O ports, handle signal directions, and understand naming

0 views • 41 slides

Advances in ILD Detector Design and TPC R&D

Explore the latest developments in ILD detector optimization and TPC research, focusing on enhancing event reconstruction accuracy and energy resolution. Learn about the ILD concept based on particle flow, the ILD group activities, organizational structure, technical advancements, and TPC readout te

0 views • 22 slides

Enhancing Workforce Development in Electronics for High Energy Physics (HEP)

Addressing the challenge of finding expertise in electronics, particularly in digital logic development for FPGA and ASIC, this initiative focuses on creating tools, structures, codebases, and educational programs to efficiently train the next generation. The aim is to improve local training efforts

0 views • 6 slides

Hardware Offload BoF Discussion at Netdev01

Discussion at the Hardware Offload BoF session during Netdev01 focused on preserving the Linux networking model, exchanging ideas on capability determination, and addressing challenges in emulating hardware devices in switch models. Participants explored topics such as managing devices in a generic

0 views • 5 slides

Dual-Readout Calorimeter for CepC: Overview and Key Features

The dual-readout calorimeter for CepC, as discussed in the International Review in Beijing, September 2018, is designed to optimize electromagnetic, hadronic, and jet resolution. With features like large sampling fraction for good EM resolution, event-by-event correction for EM fluctuations, and int

0 views • 22 slides

Development Updates for ProtoDUNE Phase II: CRP Modifications and Testing

Updates on the development of Charged Readout Plane (CRP) for ProtoDUNE Phase II driven by lessons from commissioning and operation in ProtoDUNE-DP. Major topics include modifications for CRP mechanical structure, new LEM development, cold box improvements, and testing plans. Detailed steps per syst

0 views • 7 slides

Advancements in CATIROC Technology for Neutrino Observatories

CATIROC is a smart readout ASIC developed for experiments like JUNO, a neutrino observatory. With applications in photon counting, energy measurement, and data processing, CATIROC offers advanced features such as charge and time measurements, digital data conversion, and trigger outputs for improved

0 views • 20 slides

Overview of ICARUS LAr-TPC Installation and Testing

Detailed overview of the installation and testing procedures for the ICARUS Liquid Argon Time Projection Chamber (LAr-TPC) readout electronics. The system comprises front-end amplifiers, ADC systems, optical links for data transmission, mini-crates housing the electronics boards, power supplies, and

0 views • 6 slides

Beam Test Results with BCM and TowerJazz CMOS F9 Weekly

Bojan Hiti from Jožef Stefan Institute in Ljubljana, Slovenia conducted a series of tests involving BCM prototype readout chip and TowerJazz CMOS at CERN SPS H6. The experiments included beam tracking, analog readout, and chip configurations for the ATLAS Beam Condition Monitor upgrade. Detailed re

0 views • 19 slides

Challenges and Key Concepts in Building and Running a Large-Scale Instrumental Array

The GRAND project involves building and running a massive array of detectors over a vast area, with a focus on simplicity and cost-effectiveness. Key components include signal reconstruction, background discrimination, broadband antennas, readout electronics, and data transfer considerations. The bu

0 views • 10 slides

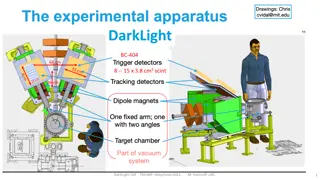

DarkLight CM TRIUMF May/June 2023 Prototype Scintillator Development Details

The DarkLight project at TRIUMF in May/June 2023 involves the development of prototype scintillators with specific requirements for triggering, timing adjustments, and readout capabilities. Various images depict different components such as SiPMs, front-end readout cards, and TOF Alpha bars. The pro

0 views • 14 slides

DARE180U Platform Enhancements in Release 5.6 - AMICSA 2018

The DARE180U platform introduces radiation-hardened ASIC design capabilities on UMC 0.18μm CMOS technology for space and high-energy physics applications. Supported by ESA and featuring ITAR-free components, it offers libraries, IP, and design services for front-end and back-end design flow. The pl

0 views • 19 slides

Challenges and Common Solutions in Implementing Full Streaming Readout for Sub-Detector Technologies

Implementing full streaming readout with proposed sub-detector technologies and DAQ system concept poses challenges including proper data alignment, risks of data loss, and background noise affecting data rates. The transition point for electronic components from detector-specific to common solution

0 views • 9 slides

Overview of Phase 0 Experiment with Straw Trackers at HADES

The Phase 0 Experiment involves including straw trackers in the program before PANDA commences at HADES. The upgrade features two new Forward Straw Tracker stations (STS1, STS2) for testing under experimental conditions. The physics program includes radiative hyperon decays, with STS1/2 tasked for s

0 views • 8 slides

Radio Frequency Readout Device (RFRD) for Tightness Measurement of Anchor Bolts

The Radio Frequency Readout Device (RFRD) Phase II project aims to reduce the time needed to check the tightness of nuts on anchor bolts. By utilizing a passive RFRD that measures capacitance changes in washers, the system offers a wireless, cost-effective solution for monitoring nut tightness. With

0 views • 27 slides

Advanced Concepts in Detector Design for High-Energy Physics Experiments

Advanced concepts in detector design for high-energy physics experiments are explored in this detailed document. It covers various aspects such as parameters, conceptual designs, radiation lengths of typical structures, thermal performance requirements, and cooling options. The content delves into s

0 views • 7 slides

Understanding High-Level Synthesis (HLS) Process

High-Level Synthesis (HLS) is an automated design process that converts functional specifications into optimized hardware implementations at the Register-Transfer Level (RTL). It offers efficient hardware development using software specifications and program logic synthesis. HLS tools such as Verilo

0 views • 33 slides

CEPC Time of Flight and Outer Tracker with LGAD Updates

Updates on the progress of CEPC's Time of Flight and Outer Tracker with LGAD by Yunyun Fan from IHEP. The information covers sensor design, CEPCSW progress, mechanics design for cooling the ASIC, hit rate estimations for electronics, and backups. Collaboration with Italian colleagues is highlighted

0 views • 7 slides

asic design course online

Learn how to unlock your full potential in ASIC design with the online course offered by Takshila-vlsi.com. Take your career to new heights by learning from industry experts.\n\n\/\/ \/product\/asic-verification\/

3 views • 1 slides

SLAC CRYO: Waveform Digitizer/Serializer for Cryogenic TPC Experiments

SLAC is developing the CRYO ASIC, a high-performance waveform digitizer and serializer optimized for cryogenic operation in experiments like DUNE. The CRYO ASIC offers advanced features such as single-chip integration, programmability, on-chip regulation, and design for reliability. Operating in a 1

0 views • 23 slides