Advancements in PET Readout Technology: PETAT1 Time-Sorting Readout ASIC

Cutting-edge PET readout systems now utilize specialized ASICs for data acquisition from SiPMs, eliminating the need for FPGAs and reducing complexity, space requirements, and power consumption. The PETAT1 ASIC, developed by P. Fischer and team at Heidelberg University, enables time-ordered hit data streaming by allowing each chip to process data from SiPM inputs independently and merge it for output. This innovative approach improves efficiency and scalability, making it particularly beneficial for Total Body PET Scanners with numerous channels in restricted spaces.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

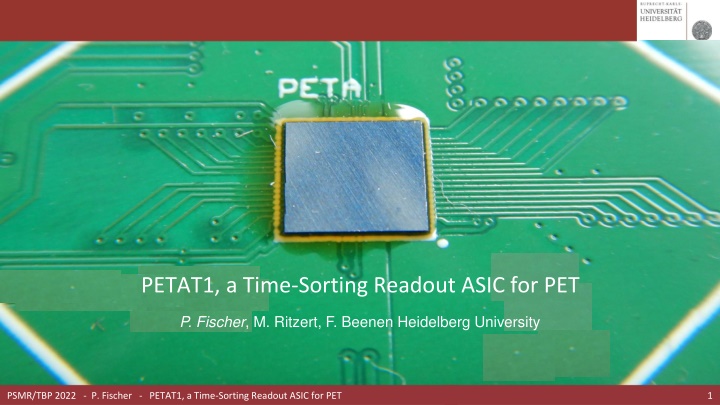

PETAT1, a Time-Sorting Readout ASIC for PET P. Fischer, M. Ritzert, F. Beenen Heidelberg University PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 1

State if the Art PET Readout Most modern PET readout systems use specialized ASIC to read SiPMs These transfer their data to FPGAs for data aggregation Power for Chips Power Power Regulators SiPMs FE Power Regulators Hyperion III platform as presented e.g. by D. Schug yesterday here Config. Flash Flash Program Configuration SiPMs FE FPGA Slow Control Timing Signal Out (optical?) Data Out SiPMs FE HV for SiPM HV FPGA & its infrastructure add complexity, space, power, need cooling, This is particularly problematic for Total Body PET Scanners with many channels and restricted space Can this be improved ? Yes. (this talk ) PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 3

Basic Concept Each chip generates own data from SiPM inputs (amplify, time stamp, integrate, get amplitude) In addition, chips can receive (serial) data from other chips. Each chip merges the data and sends it out (serially) - No more FPGA required! SiPMs SiPMs SiPMs PETAT PETAT PETAT SiPMs SiPMs SiPMs PETAT PETAT PETAT Time sorted! This approach allows it to generate a time-ordered hit data stream! PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 4

Inside PETAT1 (simplified) Data packet with time stamp Hits in FIFOs are time ordered! Time sorting merge operation. Easy! Time ordered serial input streams 9 Ser/Par FIFO (256) 8 5 2 1 Ser/Par Hit stream 1 Remove Select oldest hit Hit stream N 7 Ser/Par FIFO (256) 6 1 TDC / ADC 3 Cor. 3 FIFO (16) 2 Select oldest hit TDC / ADC - Cor. SiPMs Timeout event generator Global stuff: Bias, Time Base, ... TDC / ADC 5 Cor. PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 5

The Fabricated PETAT1 Chip PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 7

Starting Point: PETA8 My group has developed the PETA8 SiPM readout chip: 32 Channels ~13 mW / channel (analogue + digital, incl. global blocks) TDC with 50 ps / bin Charge integrator with 9 Bit ADC JTAG, neighbour Logic, solder balls, This chip / its predecessor is being used by several PET/MRI scanner projects: SAFIR (ETH Z rich, see J. Debus s talk yesterday here) RF penetrable PET (C. Levin et al., Stanford University) (others upcoming) PETA8 chip photograph System CRT is ~194 ps / 242 ps PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 8

PETAT1 PETAT1 has been designed and fabricated in 180nm CMOS technology It comes as a naked die of 5 x 6 mm2size (upper / lower rows are test structures) Solder Balls in 500 m pitch allow for simple flip chip soldering PWD_B TDC_N MONA ID<2> ID<0> i<14> i<30> InjHi TMS TCK TDC_P MOND ID<3> ID<1> i<15> i<31> InjLo TDO SUB TDI GNDO GNDA VDDO VDDA VDDA VDDA i<12> i<13> i<29> i<28> GNDA GNDD GNDD GNDD GNDD GNDA i<25> i<24> i<8> i<9> VDDA VDDD VDDD VDDD VDDB VDDA i<11> i<10> i<26> i<27> GNDA GNDD GNDD GNDD GNDB GNDA i<22> i<23> i<7> i<6> Vprog VDDA VDDD VDDD VDDD VDDA i<20> i<21> i<5> i<4> GNDO GNDA GNDA GNDA VDDO VDDA i<16> i<18> i<2> i<0> INHIBIT_N Trigger_N SerOut_N Child0_N Child1_N Ctrl_N Clk_N i<17> i<1> INHIBIT_P Trigger_P SerOut_P Child0_P Child1_P Ctrl_P PETAT1 flipped to a test PCB Clk_P i<19> SUB i<3> PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 9

(Signals and Pins) PETAT1 has very few mandatory pins: Category Pins Mandatory Signals Category Slow Control Pins 4 1 1 (diff.) 1 1 1 1 (diff.) 1 Optional Signals JTAG: TCK, TMS, TDI, TDO PowerDown Digital Injection 2ndanalogue Injection (Lo / Hi) Analogue monitor for debugging Digital monitor for debugging Inhibit = Gating Programming of Chip-ID Power 4 Analogue, Digital SiPM Inputs 32 Single ended inputs Test Slow / Fast Control 1 (diff.) 4 Fast Reset, configuration, Unique (static) Chip ID TDC 1 (diff.) Clock ~600 MHz Misc Readout 1 (diff.) 2 (diff.) 1 (diff.) Clock Serial Child inputs Serial Output Optional pins PWD_B TDC_N MONA ID<2> ID<0> i<14> i<30> InjHi TMS TCK Test 1 Analogue Injection TDC_P MOND ID<3> ID<1> i<15> i<31> InjLo TDO SUB TDI GNDO GNDA VDDO VDDA VDDA VDDA i<12> i<13> i<29> i<28> GNDA GNDD GNDD GNDD GNDD GNDA i<25> i<24> i<8> i<9> This simplifies PCB and system design significantly (no analogue pins!) VDDA VDDD VDDD VDDD VDDB VDDA i<11> i<10> i<26> i<27> GNDA GNDD GNDD GNDD GNDB GNDA i<22> i<23> i<7> i<6> Vprog VDDA VDDD VDDD VDDD VDDA i<20> i<21> i<5> i<4> GNDO GNDA GNDA GNDA VDDO VDDA i<16> i<18> i<2> i<0> INHIBIT_N Trigger_N SerOut_N Child0_N Child1_N Ctrl_N Clk_N i<17> i<1> INHIBIT_P Trigger_P SerOut_P Child0_P Child1_P Ctrl_P Clk_P i<19> SUB i<3> PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 10

Test Setup Custom USB 3.0 Board with FPGA: clock serin data USB3.0 FT601Q data USB HUB FPGA XC7A35 PETAT1 USB2.0 FT2232 TUSB8020BI config output data PC FPGA generates serial input data (emulating other chips) sends it to PETAT1 receives output data & stores it Data is read via USB and analysed Only single chips tested so far All digital tests as expected PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 11

Simulation PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 12

(Very Simplistic!) Simulation to Demonstrate Feasibility in PET Scanner RI = 30 cm, LZ = 150cm. Varying # of crystals and readout chips Very simple PET : No absorption, scatter,... Time resolution is perfect to ease reconstruction with ToF Fully simulated digitally (i.e. cycle accurate) all (up to 1024!) chips Study output data. Reconstruct Image for consistency check One readout chip serves this area - 1024 = 32 x 32 chips - 32768 crystals - (d ,dZ) ~ (7,11) mm 64 = 8 x 8 chips PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 13

Source, Decays, Hits, Reconstruction Reconstruction - Hit position degraded by crystal size - ToF with perfect time resolution Generated decays: Homogeneous sphere of R=15 cm Hits on PET cylinder PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 14

Chip Connection Topologies PETAT PETAT PETAT Linear chain: Balanced Tree: PETAT PETAT PETAT PETAT PETAT PETAT PETAT + simple topology - Hits in last chips must wait long -> buffer load - More complex interconnect PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 15

Expected and Simulated Maximum Data Rate At our present clock of 312.5 MHz and 80 bit events (incl. 8B10B), the link limit is 3.9 Mevents/s This corresponds to a source activity of ~2.1 MBq (losses at cylinder ends, no absorption. No sharing!) Architecture is FULLY efficient up to the max. rate! No safety margin needed! PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 17

Study of Data Losses chip Image shows data loss in each chip for just acceptable and 2 x too high hit rates for linear chain Differences between topologies are clearly visible in overload condition: Losses in Tree are still very balanced PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 18

Final FPGA Processing Achievable rate per chain is ~16 MHits/s (@ ~1 GHz transport, 8B10B, 48 Bit / Hit) 8 MBq For higher activities, must use several chains. For N=32 chains, can read 260 MBq The N serial chains can be combined in ONE final FPGA per SCANNER: time sorted list of all hits in scanner! Chain N time sort and merge chip/ chan z/phi ser / par cluster energy calc. cluster energy cut cluster z/phi calc. timeout removal time coinc. gain correct To PC Chain 1 Chain 0 RAM RAM N x 1 bit @ 1 Gbps N x 48 Bit @ 16 MHz 48 Bit @ Discard lonesome hits Discard wrong energies N x 16 MHz FPGA preprocessing reduces data volume to PC to a minimum! PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 19

Summary, Next Steps We propose a hierarchical data collection for PET Data No FPGA close to R/O ASICs, minimal # components, reduced power, compact design This allows on-the-fly time-sorting of PET events. Final data merging requires only one global FPGA Real time hit processing and data reduction, immediate rejection of singles, energy cuts, . We have designed, fabricated and successfully tested a first prototype chip PETAT1 We have set up a cycle-accurate sim. of >1000 chips to study data losses vs. topology, FIFO sizes, We have combined this with a first very simple PET Monte Carlo to demonstrate feasibility Next Steps Hardware test of multiple chips , more realistic PET sim., design improvements, new chip with latest SiPM FE Build a demo scanner ? PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 20

Thank you for your attention PSMR/TBP 2022 - P. Fischer - PETAT1, a Time-Sorting Readout ASIC for PET 21