Network Function Abstraction A delicate question of (CPU) affinity?

Exploring the delicate balance of CPU affinity in network function abstraction, including challenges, benefits, and solutions like CPU pinning for network workloads. Learn about the impact on performance and scalability, as well as the importance of proper configuration in virtual and physical envir

3 views • 40 slides

Understanding the Basics of Computer Hardware and CPU

Explore the fundamental concepts of information technology, focusing on hardware components like the CPU, control unit, ALU, registers, and cache memory. Learn about the functions of these parts and how they contribute to a computer's performance and speed.

3 views • 37 slides

Understanding Computer Architecture in CSE502

Exploring the intricate details of computer architecture in CSE502, covering concepts such as instruction commit, pipeline stages, program execution order, CPU state management during context switches, and implementation in the CPU. The focus is on the sequential part and the unified register file,

1 views • 26 slides

Understanding Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

MIPS CPU Design Using Verilog and Instruction Set Architecture Overview

Explore the world of MIPS CPU design using Verilog with a deep dive into Instruction Set Architecture (ISA), SPIM instruction formats, addressing modes, and more. Learn about the key components such as Program Counter (PC), Instruction Memory (IM), Register Files (RF), Arithmetic Logic Unit (ALU), D

1 views • 29 slides

Introduction to Intel Assembly Language for x86 Processors

Intel Assembly Language is a low-level programming language designed for Intel 8086 processors and their successors. It features a CISC instruction set, special purpose registers, memory-register operations, and various addressing modes. The language employs mnemonics to represent instructions, with

2 views • 12 slides

Understanding Interrupts in Embedded Systems

In embedded systems, interrupts play a crucial role in letting peripherals notify the CPU of state changes. They are events external to the current process that disrupt the normal flow of instruction execution, typically generated by hardware devices. By using interrupts, CPUs can efficiently handle

1 views • 12 slides

Understanding von Neumann Architecture in Parallel & Distributed Systems

Exploring the von Neumann architecture, this lecture delves into the components like main memory, CPU, registers, and data transfer. It discusses the bottleneck problem and modifications made to enhance CPU performance, such as caching methods. The web presentation offers insights into key aspects o

0 views • 23 slides

Understanding Cache Memory in Computer Architecture

Cache memory is a crucial component in computer architecture that aims to accelerate memory accesses by storing frequently used data closer to the CPU. This faster access is achieved through SRAM-based cache, which offers much shorter cycle times compared to DRAM. Various cache mapping schemes are e

2 views • 20 slides

Evolution of Microprocessors: A Historical Overview

The history of microprocessors traces back to Fairchild Semiconductors in 1959, leading to the founding of Intel in 1968. The evolution from 4-bit to 64-bit microprocessors by Intel revolutionized computing. Key milestones include the Intel 4004 and 4040 (4-bit), 8008, 8080, and 8085 (8-bit), and th

2 views • 44 slides

Hardware-Assisted Virtualization: VT-x Overview and Implementation

Explore the key concepts of hardware-assisted virtualization using Intel VT-x technology for CPU virtualization, VMX transitions, and VM control structures. Understand the motivation behind VT-x, CPU virtualization techniques, and the benefits of VT-x in simplifying VMM software. Dive into VMX opera

2 views • 28 slides

What are the Top Features of Dell XPS 13 Laptop?

Looking for a high-performance laptop? The Dell XPS 13, available at Dubai Laptop Rental, features a 6th gen Intel Core i7 processor, 256GB SSD, and Intel Iris Graphics. For more details on Laptop Rental Dubai call us at 050-7559892.

3 views • 2 slides

Understanding CPU Scheduling in Operating Systems

In a single-processor system, processes take turns running on the CPU. The goal of multiprogramming is to keep the CPU busy at all times. CPU scheduling relies on the alternating CPU and I/O burst cycles of processes. The CPU scheduler selects processes from the ready queue to execute when the CPU i

1 views • 26 slides

Intel Software OneAPI Level Zero Sysman Overview

Introducing Intel Software OneAPI Level Zero Sysman, a powerful API that provides fine-grained control over accelerator devices, offering features such as monitoring power profiles, controlling device performance, and managing peer-to-peer interconnects. With a focus on security and flexibility, Lev

0 views • 24 slides

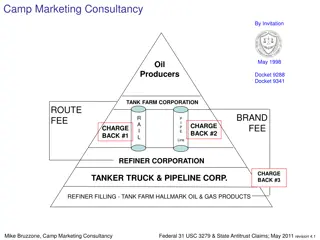

Camp Marketing Consultancy Overview in Oil and Gas Industry

Camp Marketing Consultancy, led by Mike Bruzzone, provides consultancy services to oil and gas companies, particularly in the area of marketing and sales strategies. The consultancy firm specializes in establishing route fees, brand fees, and chargebacks within the industry. Through various marketin

0 views • 4 slides

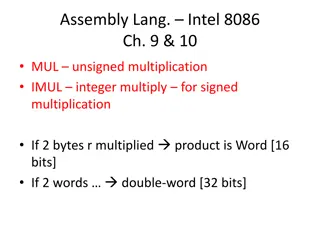

Assembly Language Programming in Intel 8086: Multiplication, Division, and Array Handling

Assembly language programming in Intel 8086 involves operations like unsigned and signed multiplication using MUL and IMUL instructions, respectively, along with division using DIV and IDIV instructions. This programming also encompasses handling arrays through the use of DUP to define arrays with c

0 views • 10 slides

Accelerate AI Performance with DirectML on Intel Hardware by Szymon Marcinkowski

Learn about leveraging DirectML on Intel hardware to boost AI performance, including insights on Windows AI ecosystem, DirectML optimizations, scaling AI models, and tools like Windows ML, ONNX Runtime, and more.

0 views • 17 slides

Evolution of Intel Microprocessors: From 4004 to Pentium 4

Explore the history of Intel microprocessors, from the groundbreaking 4004 and 8008 to the evolution of 16-bit and 32-bit processors like the 8086 and the Pentium 4. Discover how Moore's Law has driven advancements in transistor count and processing capabilities in the world of microprocessors.

0 views • 39 slides

Understanding Cache Memory in Computer Systems

Explore the intricate world of cache memory in computer systems through detailed explanations of how it functions, its types, and its role in enhancing system performance. Delve into the nuances of associative memory, valid and dirty bits, as well as fully associative examples to grasp the complexit

0 views • 15 slides

Overview of Intel 8086 Microprocessor and Internal Architecture

Intel 8086 microprocessor is a vital component in electronics, with an internal architecture comprising BIU and EU. The BIU handles bus operations, instruction fetching, and address calculation, while the EU executes instructions from the instruction queue. The pin diagram and internal architecture

0 views • 19 slides

Exploring Distributed File Systems with NVMM and RDMA

This content delves into the integration of Non-Volatile Memory Modules (NVMM) and Remote Direct Memory Access (RDMA) in Distributed File Systems. It covers various aspects such as new hardware architectures, NVM concepts and technologies, Intel Optane DC memories, incorporation of NVM in memory and

0 views • 22 slides

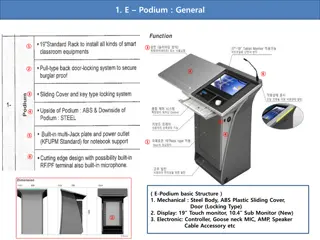

Overview of E-Podium Specifications and Components

The E-Podium is equipped with a steel body, touch monitors, a PC with Intel i3 processor, controller, and various electronic components. The display includes a 19" touch monitor and a 10.4" sub-monitor. The PC features a motherboard with Intel H61 chipset, Intel HD2000 graphics, and dual-channel DDR

0 views • 8 slides

Exploring Kubernetes Load Balancing with P4 Intel IPU Team

This presentation delves into Kubernetes load balancing and network functions using P4 Intel IPU technology. It covers service load balancing, control plane overview, P4 program logical view, demo initial setup, evaluation conclusions, and acknowledgements. The team aims to reduce CPU utilization, i

0 views • 8 slides

Secure Cloud Applications with Intel SGX - OSDI 2014 Presentation Summary

This presentation discusses the challenges of trusting cloud environments and proposes solutions utilizing Intel SGX technology. It explores the need for secure execution of applications on untrusted cloud platforms, presents existing solutions, and introduces the concept of Haven for private execut

0 views • 33 slides

Understanding Microprocessor Architecture and Instruction Processing

Explore the basic architecture of a microprocessor, including CPU registers, memory locations, and instruction processing steps. Learn about Intel microprocessor components, addressing modes, and the operation of pipeline microprocessors. Understand the role of control units, ALU, and bus interfaces

0 views • 38 slides

Understanding CPU Structure and Function in Computer Organization and Architecture

Exploring the intricate details of CPU architecture, this content delves into the essential tasks of fetching, interpreting, processing, and writing data. It discusses the significance of registers, user-visible registers, general-purpose registers, and condition code registers in CPU operations. Ad

0 views • 83 slides

Understanding CPU Architecture in Computing for GCSE Students

Explore the fundamental concepts of CPU architecture, including the Von Neumann Architecture, common CPU components like ALU and CU, and how characteristics such as Clock Speed and Cache Size impact performance. Learn about the Fetch-Execute Cycle and the essential hardware components of a computer

0 views • 18 slides

Streamlining OEM Validation Process at Intel: A Comprehensive Overview

Abstractable library offers a simplified approach for OEM validation test cases at Intel. The history and present validation practices, including an example test case, phases like analysis and design, provide insights into the process. The content delves into setting up the Integrated Test Environme

0 views • 34 slides

Intel CPU Architectures Overview: Evolution and Features

Explore the evolution and key features of various Intel CPU architectures including Pentium, Core, and Pentium 4 series. Learn about the pipeline stages, instruction issue capabilities, branch prediction mechanisms, cache designs, and memory speculation techniques employed in these processors. Gain

0 views • 11 slides

Understanding the Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

Understanding Processor Generations and VM Sizing for Azure Migration

Exploring the impact of processor generations on CPU performance, factors like clock speed, instruction set, and cache size are crucial. Choosing the right-sized VM plays a vital role in optimizing Azure migration. Passmark CPU Benchmark results provide insights on Intel processor generations for Az

0 views • 9 slides

Cutting-Edge Training Architecture Overview

Delve into the latest training innovations featuring NVIDIA Volta, Intel NNP-T/I, ScaleDeep, and vDNN. Learn about the impressive capabilities of the NVIDIA Volta GPU, Intel NNP-T with Tensor Processing Clusters, and Intel NNP-I for inference tasks. Explore the intricacies of creating mini-batches,

0 views • 32 slides

Understanding Operating System Concepts: Multiprogramming, Multiprocessing, Multitasking, and Multithreading

In the realm of operating systems, terms like multiprogramming, multiprocessing, multitasking, and multithreading can often be confusing due to their similar appearance but distinct meanings. These concepts play a crucial role in efficiently managing resources in a computing system, particularly in

0 views • 6 slides

Understanding CPU Scheduling Concepts at Eshan College of Engineering, Mathura

Dive into the world of CPU scheduling at Eshan College of Engineering in Mathura with Associate Professor Vyom Kulshreshtha. Explore topics such as CPU utilization, I/O burst cycles, CPU burst distribution, and more. Learn about the CPU scheduler, dispatcher module, scheduling criteria, and the impl

0 views • 18 slides

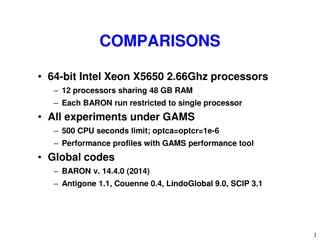

Performance Comparison of Optimization Solvers on Intel Xeon X5650 Processors

Experiment results comparing the performance of optimization solvers (BARON, Antigone, LindoGlobal, SCIP, Couenne) on Intel Xeon X5650 2.66Ghz processors with 48GB RAM. The study includes 369 NLPs from various libraries and an aggregate analysis of 1740 NLPs and MINLPs. Performance profiles generate

0 views • 6 slides

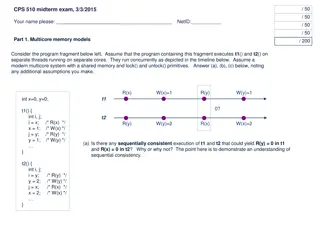

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Understanding Barrel Shifter in CPU Design

Barrel shifter is a vital component in CPU architecture, enabling shifting and rotating operations on data inputs based on control signals. The shifter consists of two main blocks - Shift-and-Rotate Array (SARA) and Control Logic. SARA, designed with multiple stages of cells, executes shift and rota

0 views • 12 slides

Understanding CPU Virtualization and Execution Control in Operating Systems

Explore the concepts of CPU virtualization, direct execution, and control mechanisms in operating systems illustrated through a series of descriptive images. Learn about efficient CPU virtualization techniques, managing restricted operations, system calls, and a limited direct execution protocol for

0 views • 18 slides

Enhancing gem5's GPUFS Support for Improved Simulation Speed

Addressing challenges in application scaling, this project focuses on enhancing gem5's GPUFS support to improve simulation speed by functionally simulating memory copies and adding KVM CPU-GPU support. The introduction covers prior CPU-GPU support in gem5, ML support, and the introduction of GPUFS s

0 views • 19 slides

Illustrated Design of a Simplified CPU with 16-bit RAM

Demonstrates the design of a basic CPU with 11 instructions and 4096 16-bit RAM, showcasing the assembly of a general-purpose computer using gates and registers. The CPU comprises 8 key registers for various functions, employing a sequential circuit for instruction execution. The machine language pr

0 views • 31 slides