Understanding Manufacturing Readiness Levels (MRLs) in Defense Technology

Manufacturing Readiness Levels (MRLs) are a vital tool in assessing the manufacturing maturity and associated risks of technology and products in defense acquisitions. They provide decision-makers with a common understanding of the maturity levels to support informed decisions throughout the acquisi

1 views • 12 slides

Army Rapid Capabilities and Critical Technologies Office Symposium 2023

LTG Robert A. Rasch, Jr., U.S. Army Director of Hypersonics, Directed Energy, Space, and Rapid Acquisition, presented updates on various defense projects at the Space and Missile Defense Symposium 2023. Topics included the Long Range Hypersonic Weapon program, Mid-Range Capability development, and D

5 views • 11 slides

Understanding Manufacturing Readiness Levels (MRLs) in Defense Acquisition

The Joint Defense Manufacturing Technology Panel (JDMTP) establishes Manufacturing Readiness Levels (MRLs) as a risk identification tool for assessing the manufacturing maturity, risks, and capabilities related to defense technology production. MRLs provide decision-makers with a common understandin

0 views • 14 slides

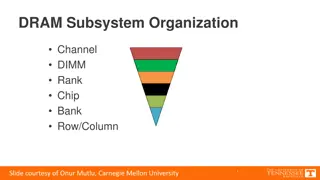

Understanding the Organization of DRAM Subsystem Components

Explore the intricate structure of the DRAM subsystem, including memory channels, DIMMs, ranks, chips, banks, and rows/columns. Delve into the breakdown of DIMMs, ranks, chips, and banks to comprehend the design and functioning of DRAM memory systems. Gain insights into address decoding, row/column

0 views • 16 slides

Future of Radiological and Nuclear Defense Programs and Capabilities

The Radiological and Nuclear Defense Capability Development Directorate discusses the responsibility for modernizing and procuring defense capabilities in the face of radiological and nuclear threats. The Department of Defense outlines strategic priorities to ensure the ability to survive and prevai

1 views • 10 slides

Transforming NLP for Defense Personnel Analytics: ADVANA Cloud-Based Platform

Defense Personnel Analytics Center (DPAC) is enhancing their NLP capabilities by implementing a transformer-based platform on the Department of Defense's cloud system ADVANA. The platform focuses on topic modeling and sentiment analysis of open-ended survey responses from various DoD populations. Le

0 views • 13 slides

Essential Self Defense Tips and Techniques for Personal Safety

Explore the world of self-defense with insights from BJJ Black Belt Alex Vamos. Learn about physical and mental self-defense, enhancing awareness, important skills to master, assessing safety in hangout spots, and trusting your instincts to stay safe from potential threats.

3 views • 24 slides

Computer Architecture: Understanding SRAM and DRAM Memory Technologies

In the field of computer architecture, SRAM and DRAM are two prevalent memory technologies with distinct characteristics. SRAM retains data as long as power is present, while DRAM is dynamic and requires data refreshing. SRAM is built with high-speed CMOS technology, whereas DRAM is more dense and b

1 views • 38 slides

Graduate School Defense Committee Guidelines

Comprehensive guidelines for thesis/dissertation defense committees at The Graduate School, SUNY ESF. Includes details on committee structure, purpose of defense, roles of members, scheduling, and more.

0 views • 15 slides

High-Throughput True Random Number Generation Using QUAC-TRNG

DRAM-based QUAC-TRNG provides high-throughput and low-latency true random number generation by utilizing commodity DRAM devices. By employing Quadruple Row Activation (QUAC), this method outperforms existing TRNGs, achieving a 15.08x improvement in throughput and passing all 15 NIST randomness tests

0 views • 10 slides

SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Processing Using DRAM

SIMDRAM introduces a novel framework for efficient computation in DRAM, aiming to overcome data movement bottlenecks. It emphasizes Processing-in-Memory (PIM) and Processing-using-Memory (PuM) paradigms to enhance processing capabilities within DRAM while minimizing architectural changes. The motiva

2 views • 14 slides

Understanding Unsoundness of Mind as a Defense in Law

The concept of unsoundness of mind as a defense in law is explored through principles of criminal liability and historical legal perspectives. The defense under Section 84 of the Indian Penal Code provides immunity for acts committed by individuals incapable of understanding the nature of their acti

1 views • 20 slides

Defense Presentation of "TITLE OF DISSERTATION" by Doctoral Candidate

This presentation features the defense process of a dissertation by a doctoral candidate, covering aspects such as the problem statement, theoretical framework, research questions, methodology, and findings. The defense includes committee introductions, dissertation presentation, audience questions,

0 views • 12 slides

Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the n

0 views • 43 slides

Dram Shop Act and Premises Liability for Bar and Tavern Owners

Understanding the liabilities and responsibilities of bar and tavern owners under the Dram Shop Act based on the case of Build It and They Will Drink, Inc. v. Strauch. The act outlines exceptions where licensees can be held civilly liable for selling alcohol to minors or visibly intoxicated individu

0 views • 12 slides

Improving GPGPU Performance with Cooperative Thread Array Scheduling Techniques

Limited DRAM bandwidth poses a critical bottleneck in GPU performance, necessitating a comprehensive scheduling policy to reduce cache miss rates, enhance DRAM bandwidth, and improve latency hiding for GPUs. The CTA-aware scheduling techniques presented address these challenges by optimizing resourc

0 views • 33 slides

Enhancing Multi-Node Systems with Coherent DRAM Caches

Exploring the integration of Coherent DRAM Caches in multi-node systems to improve memory performance. Discusses the benefits, challenges, and potential performance improvements compared to existing memory-side cache solutions.

0 views • 28 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

0 views • 48 slides

Understanding the Good Faith Personnel Action Defense in Workers' Compensation Cases

Exploring the application of the good faith personnel action defense in workers' compensation cases, examining relevant case law, factors for consideration by medical-legal evaluators and judges, and the Rolda v. Pitney Bowes, Inc. decision that established the analytical framework for this defense.

1 views • 36 slides

The Parasomnia Defense: Unusual Mental Health Defense in State v. Joseph A. Mitchell Case

The case of State v. Joseph A. Mitchell involves shocking events where Mitchell killed his son, attacked his daughter, and attempted suicide. The defense presented focuses on parasomnia, indicating Mitchell had no memory of the events due to a sleep disorder. Bizarre and odd facts, including Mitchel

4 views • 44 slides

Understanding Criminal Defenses and Legal Concepts

Explore the intricate realm of criminal defenses, from Mens Rea to Actus Reus, and delve into various defense strategies such as alibi, excuse defense, defense of self, property, and others. Uncover the nuances of legal concepts like infancy and not criminally responsible excuses in the context of c

2 views • 19 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Understanding RowPress: A New Read Disturbance Phenomenon in Modern DRAM Chips

Demonstrating and analyzing RowPress, a novel read disturbance phenomenon causing bitflips in DRAM chips. Different from RowHammer vulnerability, RowPress showcases effective solutions on real Intel systems with DRAM chips.

0 views • 46 slides

Managing DRAM Latency Divergence in Irregular GPGPU Applications

Addressing memory latency challenges in irregular GPGPU applications, this study explores techniques like warp-aware memory scheduling and GPU memory controller optimization to reduce DRAM latency divergence. The research delves into the impact of SIMD lanes, coalescers, and warp-aware scheduling on

0 views • 33 slides

Panopticon: Complete In-DRAM Rowhammer Mitigation

Despite extensive research, DRAM remains vulnerable to Rowhammer attacks. The Panopticon project proposes a novel in-DRAM mitigation technique using counter mats within DRAM devices. This approach does not require costly changes at multiple layers and leverages existing DRAM logic for efficient miti

0 views • 17 slides

Understanding DRAM Errors: Implications for System Design

Exploring the nature of DRAM errors, this study delves into the causes, types, and implications for system design. From soft errors caused by cosmic rays to hard errors due to permanent hardware issues, the research examines error protection mechanisms and open questions surrounding DRAM errors. Pre

0 views • 31 slides

Legal Updates on Michigan FOIA, Brady v. Maryland, and Defense Counsel's Role

Explore legal topics such as the Michigan Freedom of Information Act, Brady v. Maryland, and the role of defense counsel in the legal system. Learn about the rights and obligations of prosecutors, defense attorneys, and law enforcement officers in ensuring fair trials and access to evidence.

0 views • 44 slides

Crafting Persuasive Defense Theories for Trial Success

Explore the art and science of cross-examination, theory development, and defense strategies in trial storytelling. Learn the essential components of a compelling defense theory, emphasizing factual, legal, and emotional aspects. Discover examples illustrating effective defense strategies for presen

0 views • 35 slides

Transparent Hardware Management of Stacked DRAM for Memory Systems

Explore the innovative use of stacked DRAM as Part of Memory (PoM) to increase overall memory capacity and eliminate duplication. The system involves OS-managed PoM, challenges, and the potential of hardware-managed PoM to reduce OS-related overhead. Learn about the practical implications and evalua

0 views • 24 slides

Challenges and Solutions in Memory Hierarchies for System Performance Growth

The evolution of memory scaling poses challenges for system performance growth due to limitations in memory hierarchy, capacity gaps, and DRAM scaling obstacles. The need for alternative technologies and architectural support to address these challenges is highlighted, focusing on reducing latency,

0 views • 23 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

0 views • 37 slides

Understanding Power Consumption in Memory-Intensive Databases

This collection of research delves into the power challenges faced by memory-intensive databases (MMDBs) and explores strategies for reducing DRAM power draw. Topics covered include the impact of hardware features on power consumption, experimental setups for analyzing power breakdown, and the effec

0 views • 13 slides

A Software Memory Partition Approach for Eliminating Bank-level Interference in Multicore Systems

Memory requests from different threads can cause interferences in DRAM banks, impacting performance. The solution proposed involves partitioning DRAM banks between threads to eliminate interferences, leading to improved performance and energy savings.

0 views • 32 slides

Enhancing DRAM Performance with ChargeCache: A Novel Approach

Reduce average DRAM access latency by leveraging row access locality with ChargeCache, a cost-effective solution requiring no modifications to existing DRAM chips. By tracking recently accessed rows and adjusting timing parameters, ChargeCache achieves higher performance and lower DRAM energy consum

0 views • 33 slides

Sustainable Procurement Practices in Defense Department

Sustainable procurement practices play a crucial role in the Defense Department, focusing on reducing emissions, enhancing eco-labeling, and promoting administrative cooperation. Initiatives such as reciprocal defense procurement agreements and memoranda of understanding with qualifying countries co

0 views • 85 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

CLR-DRAM: Dynamic Capacity-Latency Trade-off Architecture

CLR-DRAM introduces a low-cost DRAM architecture that enables dynamic configuration for high capacity or low latency at the granularity of a row. By allowing a single DRAM row to switch between max-capacity and high-performance modes, it reduces key timing parameters, improves system performance, an

0 views • 42 slides

Defense Cost Reporting and Systems Overview

Defense Cost Analysis and Reporting Systems (CSDR) provide the cost community with essential data for developing independent cost estimates within major defense acquisition programs. The Defense Automated Cost Information Management System (DACIMS) offers instant access to historical cost informatio

0 views • 19 slides

Locality-Aware Caching Policies for Hybrid Memories

Different memory technologies present unique strengths, and a hybrid memory system combining DRAM and PCM aims to leverage the best of both worlds. This research explores the challenge of data placement between these diverse memory devices, highlighting the use of row buffer locality as a key criter

0 views • 34 slides