ANALOG AND DIGITAL ELECTRONICS 21CS33

Explore the world of analog and digital electronics through the lens of registers, counters, and flip-flops. Dive deep into the operation of these components, learn how to transfer data between registers, build and analyze shift registers, construct timing diagrams, and understand binary counters. D

0 views • 112 slides

VHDL Programming for Sequential Circuits

Explore VHDL programming for sequential circuits including SR Latch, D Latch, SR Flip Flop, JK Flip Flop, and D Flip Flop. Each code snippet is provided along with its corresponding logic and description. Gain insights into designing sequential circuits using VHDL.

13 views • 7 slides

Understanding Binary Counters and Types of Counters

Binary counters are registers used to count clock pulses, while binary counters follow the binary number sequence. There are two types of counters: serial/asynchronous counters and parallel/synchronous counters. Serial counters change output flip-flop to next flip-flop, requiring minimal hardware bu

12 views • 21 slides

APAC Position, Navigation, and Timing Solution Market Analysis & Forecast

The Asia-Pacific position, navigation, and timing (PNT) solution (satellite) market is estimated to reach $1,410.5 million by 2033 from $466.1 million in 2023, at a CAGR of 11.71% during the forecast period 2023-2033.\nRead Report Overview: \/\/bisresearch.com\/industry-report\/asia-pacific-position

11 views • 3 slides

Understanding Sequential Logic in NUS CS2100 Lecture #19

Explore the concepts of sequential logic in Lecture #19 by Aaron Tan at NUS, covering memory elements, latches, flip-flops, asynchronous inputs, synchronous sequential circuits, and different types of sequential circuits. Delve into the distinction between combinatorial and sequential circuits, memo

2 views • 26 slides

Position, Navigation, and Timing Solution Market Forecast to 2033

The global position, navigation, and timing (PNT) solution (satellite) market is estimated to reach $5.24 billion in 2033 from $1.23 billion in 2022, at a CAGR of 10.85% during the forecast period 2023-2033.\nRead Report Overview: \/\/bisresearch.com\/industry-report\/position-navigation-timing-solu

0 views • 3 slides

Understanding D Latches and Flip-Flops in Digital Systems

Digital systems rely on storage elements like D latches and flip-flops to store key information from the past. These structures can hold values of 1 or 0 based on certain control signals, ensuring deterministic behavior. Clock signals are essential for regulating when these storage elements can upda

0 views • 15 slides

Machine Learning for Predicting Path-Based Slack in Timing Analysis

Utilizing machine learning to forecast path-based slack in graph-based timing analysis offers a solution for optimizing power and area efficiency in the design process. The Static Timing Analysis incorporates accurate path-based analysis (PBA) and fast graph-based analysis (GBA) to estimate transiti

1 views • 31 slides

DNN Inference Optimization Challenge Overview

The DNN Inference Optimization Challenge, organized by Liya Yuan from ZTE, focuses on optimizing deep neural network (DNN) models for efficient inference on-device, at the edge, and in the cloud. The challenge addresses the need for high accuracy while minimizing data center consumption and inferenc

0 views • 13 slides

Basic Computer Organization and Design - Timing and Control

The timing of all registers in a basic computer is governed by a master clock generator, with clock pulses controlling the flip-flops and registers in the system. Two main types of control organization are Hardwired Control and Micro-programmed Control. The former uses digital circuitry like gates a

1 views • 4 slides

Understanding Shift Registers in Digital Electronics

Shift registers are a fundamental concept in digital electronics where binary numbers are shifted from one flip-flop to the next. They come in various types like SISO, SIPO, PISO, and PIPO, serving different purposes such as delay lines, data converters, sequential memory, and ring counters. The ope

0 views • 10 slides

Understanding Synchronous and Asynchronous Counters in Digital Electronics

Explore the concepts of synchronous (parallel) and asynchronous (ripple) counters in digital electronics, where ripple counters enable clock sharing among flip-flops and synchronous counters apply the same clock to all. Learn to design J-K and up-down counters using flip-flops with examples and stat

1 views • 4 slides

Understanding Counters in Sequential Circuits

Counters in sequential circuits are crucial components used for counting clock cycles and measuring time intervals. They are composed of flip-flops that progress through a sequence of states based on clock pulses. This sequential circuit has no inputs other than the clock pulse and relies on its int

1 views • 22 slides

Understanding Flip-Flop Timing Parameters in Digital Systems

In digital systems, flip-flop timing parameters are crucial for proper operation. Synchronous inputs must remain stable before and after the clock edge to ensure correct storage of values. Clock frequency, setup time, hold time, and propagation delay play key roles in signal integrity. By considerin

0 views • 9 slides

Understanding Sequential Counters in Digital Circuits

Sequential counters, comprised of flip-flops, are essential in digital circuits for counting clock cycles. They advance through states based on clock pulses and can measure time intervals. The circuit's output state solely depends on its present state, with transitions occurring at each clock pulse.

0 views • 22 slides

Overview of Multivibrators: Types and Applications

Multivibrators are electronic circuits used for various applications such as oscillators, timers, and flip-flops. They consist of two amplifying devices cross-coupled by resistors or capacitors. The three main types are astable, monostable, and bistable multivibrators, each serving different purpose

0 views • 10 slides

Designing a Traffic Signal Timing Plan: Steps and Guidelines

This comprehensive guide covers the essential steps involved in designing a traffic signal timing plan, including determining lane configurations, proposing phase plans, identifying critical volumes, recommending phase plans, and establishing clearance intervals. It also provides insights into aspec

1 views • 26 slides

Preventing Active Timing Attacks in Low-Latency Anonymous Communication

This research addresses the vulnerabilities of onion routing to timing attacks and proposes solutions to prevent active timing attacks, focusing on low-latency anonymous communication systems. Various problems related to timing attacks in onion routing are analyzed, including the role of adversaries

0 views • 52 slides

Numerical Abstract Domain with Max Operator in Timing Analysis

Explore a numerical abstract domain based on expression abstraction and the Max operator with applications in timing analysis. The challenges in timing analysis, such as disjunctive and non-linear bounds, are discussed along with simple examples illustrating these concepts. The difficulty of proving

0 views • 21 slides

Harvesting and Postharvest Techniques for Quality Seed Production

Understand the importance of harvesting crops at the right timing to maximize seed quality. Learn about half-matured and full-matured stages, postharvest ripening, and indicators for precise timing. Discover the significance of counting days from flowering/pollination for determining harvest timing.

0 views • 24 slides

Verilog FF Circuit Examples & Assignments Overview

Delve into Verilog FF circuit examples such as Gated D Latch and D Flip-Flop. Understand blocking and non-blocking assignments, their differences, and practical implications. Learn when to use each assignment method in Verilog design for combinational always blocks.

0 views • 17 slides

Altera Tools & Basic Digital Logic Lab Prep Activities

In preparation for the lab, tasks include registering on the Altera website, ordering required boards, installing software, familiarizing with DE0-Nano-SOC board, exploring digital logic concepts, and practicing Verilog circuits like half adder, full adder, D Flip Flop. The activities involve downlo

0 views • 13 slides

IEEE802.15-14-0110-01-0mag MAC Timing Discussion Points for IEEE 802.15.4 Revision

Initial discussion document submitted by Benjamin A. Rolfe from Blind Creek Associates addressing MAC timing issues in the IEEE 802.15.4 standard revision. The document identifies potential problems, provides a list of questions for consideration, and outlines areas for improvement. It includes stat

0 views • 8 slides

Cesarean Delivery Timing Guidelines for Women with Prior Uterine Scars

Society for Maternal Fetal Medicine provides cesarean delivery timing recommendations for women with prior uterine scars. For those with a history of classical cesarean, the risk of uterine rupture guides the timing of repeat cesarean. Similarly, women with prior myomectomy should plan delivery betw

0 views • 10 slides

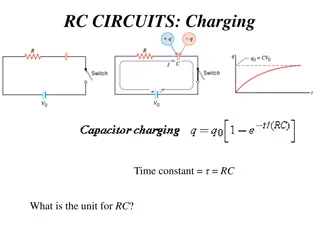

Applications of RC Circuits in Electronics and Biomedical Devices

RC circuits play a crucial role in various applications such as camera flashes, timing devices in automobiles, and heart pacemakers. These circuits involve charging and discharging a capacitor through a resistor, controlling voltage pulses for precise timing. In devices like camera flashes, the flas

0 views • 7 slides

NTN RRM Timing Related Requirements for Xiaomi Devices at 3GPP TSG-RAN4 Meeting #98-e

The agenda item for the 3GPP TSG-RAN4 Meeting #98-e involves discussing NTN RRM timing related requirements, specifically focusing on UE timing synchronization for Xiaomi devices. Key aspects include UE transmit timing error limits, timing advance accuracy, and UE timer accuracy requirements for NTN

0 views • 6 slides

WylasTiming - Wireless Semi-Automatic Timing System Overview

WylasTiming is a wireless semi-automatic timing system developed in Australia, utilizing off-the-shelf hardware and Android handsets. It provides accurate timing with automatic race starting and instantaneous data transmission. The timekeeper simply stops the clock at the end of the race, and data i

0 views • 15 slides

Simplifying Post-Silicon Timing Diagnosis with NGSPA Tool

Explore how the NGSPA tool by Intel simplifies post-silicon timing diagnosis, replacing costly machines with a CAD application running on an x86 server, saving resources and enabling parallelized CAD operations. Learn about the challenges in post-silicon speed debugging, the importance of static tim

0 views • 26 slides

Understanding Timing Models in Cell Design Environments

Delve into the intricacies of timing models for cells in design environments, exploring factors affecting delay, output transitions, linear and non-linear models, and the use of table models in cell libraries to specify delays and timing checks. Discover how input transitions and output capacitance

0 views • 11 slides

Understanding Timing Vulnerabilities in Computing Systems

Explore the evolution of timing attacks in computing systems, from traditional crypt-analysis to modern web-focused techniques. Discover the gap in implementing security measures and how universities can bridge this disparity. Delve into the history, challenges, and implications of timing vulnerabil

0 views • 26 slides

Industrial All Risk Insurance Overview

Industrial All Risk (IAR) insurance provides comprehensive coverage for material damage, business interruption, and various perils such as fire, burglary, machinery breakdown, and more. The policy indemnifies against a range of risks including fire, theft, negligence, and excludes perils like war or

0 views • 8 slides

Enhancing Student Engagement with Flip in Asynchronous Online Classes

Explore the use of Flip for student engagement in asynchronous online classes through real student feedback and examples. Learn how Flip encourages interaction and collaboration, making online learning more dynamic and engaging for students. Discover various ways to use Flip for assignments, discuss

0 views • 15 slides

Discussion on Timing Mask Requirement for ULSUP-TDM in RAN4#94e Meeting

In the RAN4#94e and #94e-Bis meetings, discussions were held on the timing mask requirement for ULSUP-TDM, particularly focusing on sub-topics like evaluating uplink timing differences between LTE and NR, clarifying present time mask conditions, and testing time mask requirements. The key issue cent

0 views • 4 slides

Understanding Static Timing Analysis in Advanced VLSI Design

Static timing analysis is a crucial aspect of VLSI design, helping predict chip performance before fabrication. This article explores the importance of static timing analysis, its effectiveness, and the limitations of dynamic simulation tools like SPICE. Learn about the challenges in testing critica

0 views • 76 slides

Rectangular Dissections and Edge-Flip Chains in Lattice Triangulations

Explore equitable rectangular dissections and their applications in VLSI layout, graph mapping, and combinatorial problems in this scholarly work by Dana Randall from Georgia Institute of Technology. Discover the concept of partitioning an n x n lattice region into n2/a rectangles or areas where cor

0 views • 32 slides

Understanding Sequential Circuit Timing and Clock Frequency

Sequential circuit timing is crucial for designing digital systems. The minimum clock period, slack values, clock frequency, and critical paths play key roles in determining the operational speed and performance of sequential circuits. By analyzing flip-flop timing parameters, combinatorial logic de

0 views • 20 slides

Rainbow Cycles in Flip Graphs and Associahedra: Combinatorial Study

Exploring rainbow cycles and associated properties in the context of flip graphs and triangulations, this study delves into the diameter, realiability, automorphism group, and more of the associahedron. Motivated by binary reflected Gray codes, the research aims to find balanced Gray codes for vario

0 views • 23 slides

Flip The Museum: Extending Audience Engagement with Gamification

The project 'Flip The Museum' aims to revolutionize museum experiences by waking up visitors with interactive content. Through a mobile and web-based platform, teachers and curators can customize the museum journey for visitors, making it both educational and fun. The platform utilizes gamification

0 views • 11 slides

Understanding Variable Valve Timing (VVT) in Internal Combustion Engines

Variable Valve Timing (VVT) optimizes engine performance by adjusting valve duration, timing, and lift according to engine speed, enhancing torque, power, and fuel efficiency. VVT operates by varying intake valve opening/closing, regulating valve timing, and adjusting lift for better volumetric effi

0 views • 14 slides

Understanding Covert Timing Channels in Network Security

Covert timing channels are a method of leaking sensitive information across networks by violating security policies. These channels rely on conveying information through packet arrival patterns rather than the contents of the packets. Military applications, detection by USA government agencies, and

0 views • 26 slides