Best Tire Shop in Jacksonville for Smooth Journeys

Rely on our tire experts to guide you through the fundamentals of tire maintenance, provide insights on pre-maintenance checks, and assist you in selecting the ideal set for your vehicle. Big Chief Tire is the best Tire Shop in Jacksonville for Smooth Journeys. For more information please visit http

2 views • 2 slides

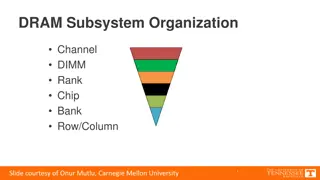

Understanding the Organization of DRAM Subsystem Components

Explore the intricate structure of the DRAM subsystem, including memory channels, DIMMs, ranks, chips, banks, and rows/columns. Delve into the breakdown of DIMMs, ranks, chips, and banks to comprehend the design and functioning of DRAM memory systems. Gain insights into address decoding, row/column

0 views • 16 slides

Best Smoke shop in Metro Park

If you\u2019re looking for a Smoke shop in Metro Park, Then contact Paradise Vape and Smoke Shop. They aim to provide great service being that they are a family-owned small business. Call them anytime if you have any questions in regards to their products and the industry. You can rest assured that

0 views • 6 slides

Best Shop Fitouts in Inchicore

Forja Works offers the Best Shop Fitouts in Inchicore. Their expertise lies in creating and innovating spaces through custom builds and woodworking. From bespoke carpentry to interior design, branding activation to production design, shop fitouts to woodwork creations, They offer a comprehensive sui

1 views • 6 slides

Machine Shop Safety Guidelines

Training safety guidelines for machine guarding, inspections, maintenance, recordkeeping, and emergency response protocols are crucial for a safe machine shop environment. The presentation emphasizes the importance of following general shop safety and housekeeping practices, maintaining clear egress

0 views • 18 slides

Computer Architecture: Understanding SRAM and DRAM Memory Technologies

In the field of computer architecture, SRAM and DRAM are two prevalent memory technologies with distinct characteristics. SRAM retains data as long as power is present, while DRAM is dynamic and requires data refreshing. SRAM is built with high-speed CMOS technology, whereas DRAM is more dense and b

3 views • 38 slides

Innovative Shop Safety System Implementation for Student Machine Shop

Implementing a cutting-edge Shop Safety System in a student machine shop to streamline training verification, automate record-keeping, and ensure safety compliance. Utilizing RFID-enabled Watcards for seamless student identification and tracking. The system features interactive stations, automated f

0 views • 11 slides

Understanding Implications of IG Empowerment Act and Paperwork Reduction Act

The IG Empowerment Act provides beneficial provisions for Inspector Generals (IGs) such as exemptions from certain acts, including the Computer Matching Act and Paperwork Reduction Act. The Paperwork Reduction Act requires federal agencies, including IGs, to obtain OMB clearance before conducting su

1 views • 25 slides

High-Throughput True Random Number Generation Using QUAC-TRNG

DRAM-based QUAC-TRNG provides high-throughput and low-latency true random number generation by utilizing commodity DRAM devices. By employing Quadruple Row Activation (QUAC), this method outperforms existing TRNGs, achieving a 15.08x improvement in throughput and passing all 15 NIST randomness tests

0 views • 10 slides

SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Processing Using DRAM

SIMDRAM introduces a novel framework for efficient computation in DRAM, aiming to overcome data movement bottlenecks. It emphasizes Processing-in-Memory (PIM) and Processing-using-Memory (PuM) paradigms to enhance processing capabilities within DRAM while minimizing architectural changes. The motiva

2 views • 14 slides

Amaira pet shop | Teacup Poodle Puppies | Poodle Dog Breeder

Amaira pet shop is a top-notch teacup poodle puppies supplier. We dedicated genuine & purebred poodle puppies, shih tzu puppies, & golden retriever with vaccinated also. Choose your furry friend at our well-know pet shop. Choose Amaira Pet Shop if yo

1 views • 5 slides

Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the n

0 views • 43 slides

Dram Shop Act and Premises Liability for Bar and Tavern Owners

Understanding the liabilities and responsibilities of bar and tavern owners under the Dram Shop Act based on the case of Build It and They Will Drink, Inc. v. Strauch. The act outlines exceptions where licensees can be held civilly liable for selling alcohol to minors or visibly intoxicated individu

0 views • 12 slides

Improving GPGPU Performance with Cooperative Thread Array Scheduling Techniques

Limited DRAM bandwidth poses a critical bottleneck in GPU performance, necessitating a comprehensive scheduling policy to reduce cache miss rates, enhance DRAM bandwidth, and improve latency hiding for GPUs. The CTA-aware scheduling techniques presented address these challenges by optimizing resourc

0 views • 33 slides

Are you looking for a Tobacco Shop in Pine Cove?

Are you looking for a Tobacco Shop in Pine Cove? The Cigar Box & Lounge is your ultimate destination for premium tobacco products and a luxurious smoking experience in Fern Valley.Our cigar shop and tobacco shop offer an extensive selection of high-q

0 views • 6 slides

H2-Wasserstoff-Shop.com.pptx

Willkommen im H2 Wasserstoff Shop, Ihrer ersten Adresse f\u00fcr modernste Wasserstofftechnologie und -l\u00f6sungen. Im H2 Wasserstoff Shop widmen wir uns der F\u00f6rderung der Zukunft sauberer Energie durch hochwertige Wasserstoffprodukte und inno

0 views • 10 slides

H2-Wasserstoff-Shop.pdf

Willkommen im H2 Wasserstoff Shop, Ihrer ersten Adresse f\u00fcr modernste Wasserstofftechnologie und -l\u00f6sungen. Im H2 Wasserstoff Shop widmen wir uns der F\u00f6rderung der Zukunft sauberer Energie durch hochwertige Wasserstoffprodukte und inno

3 views • 10 slides

Enhancing Multi-Node Systems with Coherent DRAM Caches

Exploring the integration of Coherent DRAM Caches in multi-node systems to improve memory performance. Discusses the benefits, challenges, and potential performance improvements compared to existing memory-side cache solutions.

0 views • 28 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

0 views • 48 slides

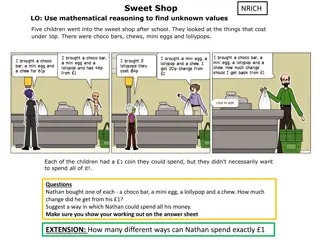

Sweet Shop Mathematical Problem Solving

Five children visited a sweet shop with £1 each to spend on items costing under 50p. The children purchased various sweets, and the task involves finding change received, determining ways to spend all the money, and solving extensions involving different combinations of purchases. The question also

0 views • 7 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Understanding RowPress: A New Read Disturbance Phenomenon in Modern DRAM Chips

Demonstrating and analyzing RowPress, a novel read disturbance phenomenon causing bitflips in DRAM chips. Different from RowHammer vulnerability, RowPress showcases effective solutions on real Intel systems with DRAM chips.

0 views • 46 slides

Managing DRAM Latency Divergence in Irregular GPGPU Applications

Addressing memory latency challenges in irregular GPGPU applications, this study explores techniques like warp-aware memory scheduling and GPU memory controller optimization to reduce DRAM latency divergence. The research delves into the impact of SIMD lanes, coalescers, and warp-aware scheduling on

0 views • 33 slides

Panopticon: Complete In-DRAM Rowhammer Mitigation

Despite extensive research, DRAM remains vulnerable to Rowhammer attacks. The Panopticon project proposes a novel in-DRAM mitigation technique using counter mats within DRAM devices. This approach does not require costly changes at multiple layers and leverages existing DRAM logic for efficient miti

0 views • 17 slides

Understanding DRAM Errors: Implications for System Design

Exploring the nature of DRAM errors, this study delves into the causes, types, and implications for system design. From soft errors caused by cosmic rays to hard errors due to permanent hardware issues, the research examines error protection mechanisms and open questions surrounding DRAM errors. Pre

0 views • 31 slides

New Kind of Shop for Stationery and More

Ms. Shahana Huda introduces a unique shop where you can purchase stationery items, food, school uniforms, and clothes without the need for bargaining. This shop offers a variety of benefits and essentials, making it a convenient one-stop destination for all your needs.

0 views • 25 slides

Delicieuse Delicieuse Sweets Shop - A Dream to Inspire

Sara Michel Shehadeh, a 13-year-old Jordanian/Armenian with a baking degree, dreams of opening a delightful sweets shop inspired by France. Her shop will cater to all ages, especially sugar lovers, offering a wide range of delectable treats from cupcakes to waffles. With a focus on quality and custo

0 views • 8 slides

Transparent Hardware Management of Stacked DRAM for Memory Systems

Explore the innovative use of stacked DRAM as Part of Memory (PoM) to increase overall memory capacity and eliminate duplication. The system involves OS-managed PoM, challenges, and the potential of hardware-managed PoM to reduce OS-related overhead. Learn about the practical implications and evalua

0 views • 24 slides

Challenges and Solutions in Memory Hierarchies for System Performance Growth

The evolution of memory scaling poses challenges for system performance growth due to limitations in memory hierarchy, capacity gaps, and DRAM scaling obstacles. The need for alternative technologies and architectural support to address these challenges is highlighted, focusing on reducing latency,

0 views • 23 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

0 views • 37 slides

Understanding Power Consumption in Memory-Intensive Databases

This collection of research delves into the power challenges faced by memory-intensive databases (MMDBs) and explores strategies for reducing DRAM power draw. Topics covered include the impact of hardware features on power consumption, experimental setups for analyzing power breakdown, and the effec

0 views • 13 slides

A Software Memory Partition Approach for Eliminating Bank-level Interference in Multicore Systems

Memory requests from different threads can cause interferences in DRAM banks, impacting performance. The solution proposed involves partitioning DRAM banks between threads to eliminate interferences, leading to improved performance and energy savings.

0 views • 32 slides

Enhancing DRAM Performance with ChargeCache: A Novel Approach

Reduce average DRAM access latency by leveraging row access locality with ChargeCache, a cost-effective solution requiring no modifications to existing DRAM chips. By tracking recently accessed rows and adjusting timing parameters, ChargeCache achieves higher performance and lower DRAM energy consum

0 views • 33 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

The Civil Rights Act of 1964 and the Supreme Court

In the 1960s, Congress passed the Civil Rights Act of 1964, a pivotal legislation that prohibited discrimination in public accommodations. This act represented a significant shift in focus towards minority rights. The Supreme Court's past rulings on the Civil Rights Act of 1875 influenced Congress t

0 views • 24 slides

CLR-DRAM: Dynamic Capacity-Latency Trade-off Architecture

CLR-DRAM introduces a low-cost DRAM architecture that enables dynamic configuration for high capacity or low latency at the granularity of a row. By allowing a single DRAM row to switch between max-capacity and high-performance modes, it reduces key timing parameters, improves system performance, an

0 views • 42 slides

Best Auto Mechanic in Scarborough Village

If you want the Best Auto Mechanic in Scarborough Village, visit K&J's Auto Ltd. \u95fd\u7ca4\u8f66\u884c. They are your local trusted auto repair shop and auto body shop based in Dorset Park, Scarborough. Their mechanical shop and body shop cover an

1 views • 6 slides

Locality-Aware Caching Policies for Hybrid Memories

Different memory technologies present unique strengths, and a hybrid memory system combining DRAM and PCM aims to leverage the best of both worlds. This research explores the challenge of data placement between these diverse memory devices, highlighting the use of row buffer locality as a key criter

0 views • 34 slides

Understanding the Impact of On-Die ECC on DRAM Error Characteristics

The BEER project explores how on-die ECC complicates DRAM reliability studies by concealing error characteristics. It aims to uncover the unique ECC function of DRAM chips and infer error locations in error-prone cells. The study highlights the challenges in identifying and correcting bit flips obfu

0 views • 17 slides