Dual Core Project Setup and Debugging Management

Explore a guide on setting up and managing dual-core projects for compilation and debugging with insights on Cortex-M4, Cortex-M0, and handling shared resources. Discover tips and tricks for efficient dual-core debugging workflows.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

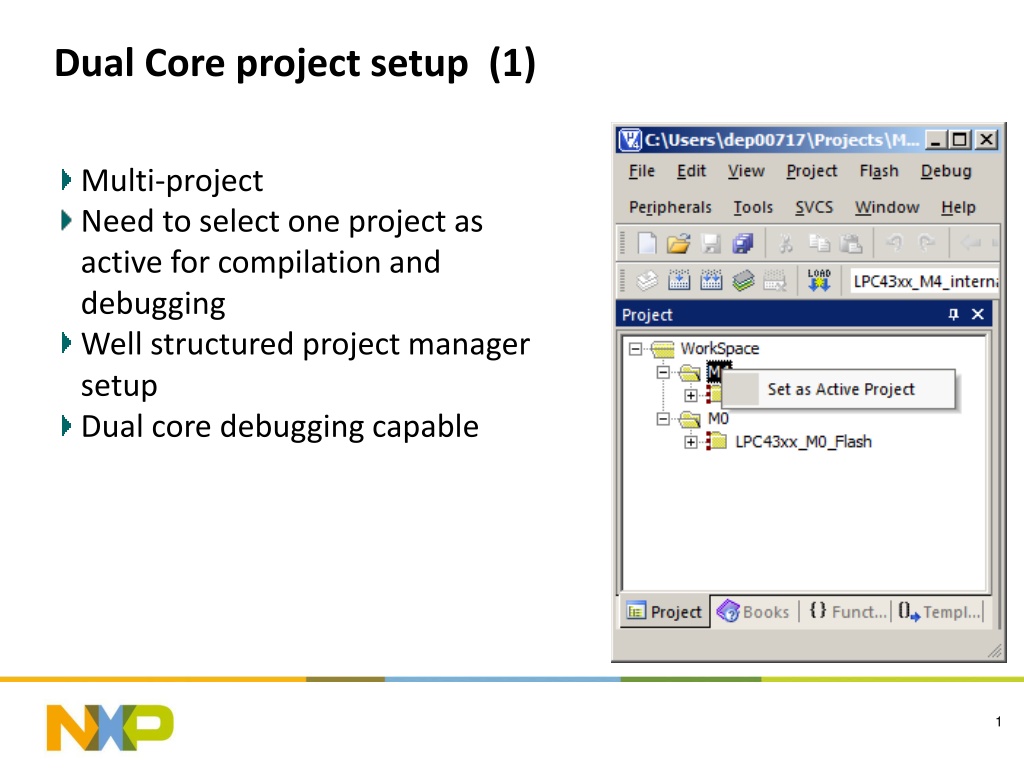

Dual Core project setup (1) Multi-project Need to select one project as active for compilation and debugging Well structured project manager setup Dual core debugging capable My favourite #1 1

Dual Core project setup (2) Two entities of Vision for compilation and debugging (possible with other IDEs as well) Dual core debugging capable Most seperated setup, e.g. for 2 different software teams Entity #1 Entity #2 2

Dual Core project setup (3) Single project with selection of different targets Possible with Vision and EWARM Makes dual core debugging quite complicated 3

Dual Core: Hints & Tricks (1) The Cortex-M0 is held in reset after a chip reset. If it starts running without getting a proper initialisation (program counter must point to reasonable executable code) then dreadful things may happen. Take care of the reset bit for the M0 in register RESET_CTRL1. Don t set it to 0 by accident, e.g. with RESET_CTRL1 = 0; The Cortex-M4 and the Cortex-M0 share the same JTAG lines. This means that connecting one of the cores with a Reset after Connect will cause a reset of the chip. The second core will be heavily affected by this reset. You must use JTAG and not SWD as communication interface Always take care of the consequences when connecting the debugger to the second core Normal order: Connect Cortex-M4 normally Write a while(1) instruction into memory using a script file and set the PC of the Cortex-M0 to this address. Then let it out of reset. Connect the Cortex-M0 silently 4

Dual Core: Hints & Tricks (2) Peripherals, bus systems and memory are shared resources. Always plan carfully which core controls what. Overlapping memory or shared access to the same peripheral is pretty hard to debug, so it s better to avoid this in advance. There is no special hardware mechanism for the communication between the cores. In principle there are 3 ways to do that: Sending an event from core #1 causes an IRQ on core #2 Connect external pins to each other and use their IRQ mechanisms Do polling on memory locations 5