Comprehensive Guide to 8085 Microprocessor Interrupts and Pin Diagram

Explore the PIN diagram of the 8085 microprocessor, understand interrupts, including hardware interrupts like TRAP, RST, INTR, and the classification of interrupts such as maskable, non-maskable, vectored, and more. Learn about the sequence of steps during interrupts and their significance in microp

12 views • 31 slides

727003-B21 HP BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT

Refurbished | HP 727003-B21 | BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/727003-b21-hp-bl460c-g9-e5-2695-v3-14-core-processor-kit\/

0 views • 1 slides

Understanding Cache and Virtual Memory in Computer Systems

A computer's memory system is crucial for ensuring fast and uninterrupted access to data by the processor. This system comprises internal processor memories, primary memory, and secondary memory such as hard drives. The utilization of cache memory helps bridge the speed gap between the CPU and main

1 views • 47 slides

Understanding Interrupts in Embedded Systems

In embedded systems, interrupts play a crucial role in letting peripherals notify the CPU of state changes. They are events external to the current process that disrupt the normal flow of instruction execution, typically generated by hardware devices. By using interrupts, CPUs can efficiently handle

1 views • 12 slides

Buy 872012-B21 HPE BL460C GEN10 XEON-S 4110 PROCESSOR KIT

Refurbished | HPE 872012-B21 | BL460C GEN10 XEON-S 4110 PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/872012-b21-hpe-bl460c-gen10-xeon-s-4110-processor-kit\/

0 views • 1 slides

Understanding Computer System Architectures

Computer systems can be categorized into single-processor and multiprocessor systems. Single-processor systems have one main CPU but may also contain special-purpose processors. Multiprocessor systems have multiple processors that share resources, offering advantages like increased throughput, econo

2 views • 25 slides

Understanding Processor Interrupts and Exception Handling in Zynq Systems

Learn about interrupts, exceptions, and their handling in Zynq Systems. Explore concepts like interrupt sources, Cortex-A9 processor interrupts, interrupt terminology, and the difference between pooling and hardware interrupts. Gain insights into interrupt service routines, interrupt pins, interrupt

0 views • 60 slides

In-Depth Look at Pentium Processor Features

Explore the advanced features of the Pentium processor, including separate instruction and data caches, dual integer pipelines, superscalar execution, support for multitasking, and more. Learn about its 32-bit architecture, power management capabilities, internal error detection features, and the ef

0 views • 24 slides

Understanding Timers and Interrupts in Operating Systems

This content discusses the importance of timers and interrupts in operating systems, focusing on how they facilitate preemptive multitasking. It covers how hardware timer interrupts help in preemption of processes by the kernel, ensuring efficient task scheduling and resource management in modern op

4 views • 18 slides

Understanding Pipelined Control in Processor Architecture

Explore the intricacies of pipelined control in processor design, detailing the control signals required at each stage of the pipeline. Learn about data hazards, forwarding, and stalling techniques to ensure efficient instruction execution. Dive into the concept of optimized control values for strea

0 views • 16 slides

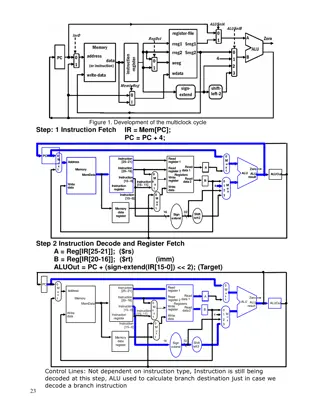

Development of Multiclock Cycle in Processor

The development process of the multiclock cycle in a processor is explained in detail through different steps, including instruction fetch, decode, register fetch, execution, and write-back for R-type instructions. Control lines and branching execution are also covered in the description. The conten

0 views • 5 slides

Overview of Inter-Processor Communication (IPC) in Processor Communication Link

Overview of Inter-Processor Communication (IPC) entails communication between processors, synchronization methods, and supported device types. The IPC architecture supports diverse use cases with various thread combinations and messaging types, catering to multi- or uni-processor environments. The A

0 views • 110 slides

Understanding Interrupts in Computer Systems

Interrupts in computer systems play a crucial role in handling various events and managing the flow of instructions. This content discusses the types of interrupts, causes, handling procedures, and the role of supervisory modes in modern computers. It covers topics such as internal and external inte

0 views • 29 slides

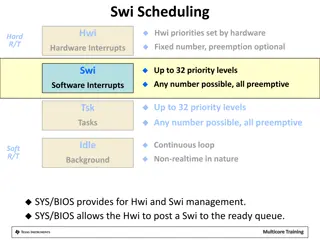

Real-Time Interrupt Handling and Scheduling in SYS/BIOS

This content covers the management of hardware and software interrupts, interrupt priorities, scheduling rules, and execution flow for real-time systems using SYS/BIOS. It discusses the handling of interrupts by the Hardware Interrupt (Hwi) and Software Interrupt (Swi) components, priority levels, p

0 views • 4 slides

Understanding Interrupt Processing in Operating Systems

An interrupt in an operating system disrupts the normal sequence of instructions executed by the processor. When an interrupt occurs, the OS takes control, saves the state of the interrupted process, analyzes the interrupt, and passes control to the appropriate routine. There are six classes of inte

0 views • 15 slides

Understanding MIPS I/O and Interrupt Handling

Delve into the world of MIPS architecture, exploring how I/O operations and interrupts are managed. Learn about memory organization, system functions, I/O registers, and kernel data. Discover how SPIM facilitates input and output handling, including reading from the keyboard and managing output. Div

0 views • 18 slides

Understanding Computer Organization: Instruction Set Architecture and Interrupts

Explore the critical concepts of Computer Organization focusing on Instruction Set Architecture (ISA) and Interrupts. ISA serves as the interface between hardware and software, enabling programmers to write machine language programs effectively. Learn about Application Binary Interface (ABI), interr

0 views • 26 slides

Out-of-Order Processor Design Exploration

Explore the design of an Out-of-Order (OOO) processor with an architectural register file, aggressive speculation, and efficient replay mechanisms. Understand the changes to renaming, dispatch, wakeup, bypassing, register writes, and commit stages. Compare Processor Register File (PRF) based design

0 views • 29 slides

Understanding Interrupts in PIC16F Microcontrollers

Explore the key sources of interrupts in PIC16F627A/628A/648A, accessing registers, enabling interrupts, and managing local interrupts such as Timer 0 alarms and B0 pin changes. Learn how to set interrupts on desired events and understand the corresponding flag bits for interrupt occurrence.

0 views • 17 slides

Understanding Interrupts and Timers in Microcontrollers

Microprocessors function as finite state machines, with instructions loaded from memory and executed in sequence. However, interrupts allow for urgent out-of-turn servicing of signals, providing a way to handle asynchronous events. Learn how to utilize interrupts efficiently with examples on Arduino

0 views • 9 slides

Understanding Interrupt Processing Sequence in X86 Processors

X86 processors have 256 software interrupts, functioning similarly to a CALL instruction. When an INT n instruction is executed, the processor follows a sequence involving pushing the flag register, clearing flags, finding the correct ISR address, and transferring CPU control. Special interrupts lik

0 views • 10 slides

Understanding Operating System Interrupts and System Calls

Explore the fundamentals of operating system interrupts and system calls in COMP.530. Learn about synchronous and asynchronous interrupts, control flow handling, and the hardware tools available for irregular control flow. Delve into the key building blocks of operating systems such as context switc

0 views • 30 slides

Understanding Interrupts in 8051 Microcontroller

Interrupts in 8051 microcontrollers allow the system to respond to asynchronous events while multitasking on a single CPU, giving the illusion of handling many things simultaneously. They introduce the concept of priority, enabling preference over simultaneous interrupts. The interrupt vectors deter

0 views • 13 slides

Understanding Fundamental Concepts of Interrupts in Embedded Systems

Explore the fundamental concepts of interrupts in embedded systems, including interrupt handling, maskability, priority, service routines, and interrupt vectors. Learn how interrupts allow the CPU to handle special events efficiently, coordinate I/O activities, and prevent CPU tie-up, enhancing syst

0 views • 57 slides

Understanding Microcontroller Interrupts and Applications

Explore the fundamental concepts of interrupts, PWM, timer/counters, and ADC in microcontrollers. Learn how to use interrupts for tasks like LED blinking, control LED brightness with PWM, and read voltage using ADC. Get insights on interrupt routines, enabling interrupts through registers, and tips

0 views • 32 slides

Understanding Interrupt Handling with LPC2148 in Electronics & Telecommunication

Introduction to interrupt handling with LPC2148 focusing on ARM processors, IRQ, FIQ, associated registers, interrupt enabling, types of interrupts (FIQ, Vectored IRQ, Non-Vectored IRQ), and differences between Vectored and Non-Vectored interrupts in the context of LPC2148. Discusses interrupt sourc

0 views • 15 slides

Understanding Interrupt Handling in MSP430 Embedded Systems

This lab explores the intricacies of handling interrupts in MSP430, covering types of interrupts, enabling interrupts, and the execution flow when an interrupt is requested and serviced. Topics include interrupt service routines, clearing interrupt flags, and enabling/disabling maskable interrupts.

0 views • 23 slides

Understanding Interrupts and MicroBlaze in Advanced Embedded Systems

Dive into the world of interrupts in embedded systems with a focus on MicroBlaze architecture. Learn how interrupts enable multitasking, the process of handling interrupts, and generating interrupts in MicroBlaze. Explore custom IP integration and gain insights into interrupt-driven programming. Dis

0 views • 32 slides

Understanding Timers and Scheduled Interrupts in Physics 124

The lecture covers timer basics for Arduino Uno/Nano, discussing available timers, prescaler options, PWM frequencies, and implementation details. It explains prescaling and frequency concepts, wrap times for Timer0, Timer1, and Timer2, and the importance of timed interrupts for creating a schedule

0 views • 21 slides

Understanding Computer Architecture Interrupts and Exceptions

Computer architecture interrupts and exceptions are essential for handling external events and unexpected conditions during program execution. Interrupts are caused by external events such as I/O requests, timers, or hardware failures, while exceptions occur due to specific instruction executions. W

0 views • 19 slides

Understanding Arduino Timer and External Interrupts

Interrupts play a crucial role in Arduino programming, allowing for immediate responses to external events. This content covers the concepts of timer interrupts and external interrupts, their applications, and how to use them effectively in Arduino projects. It explains how interrupts work, provides

0 views • 11 slides

Understanding Interrupts in Embedded Systems using MicroBlaze

Dive into the world of interrupts in embedded systems with a focus on using the MicroBlaze soft core processor and custom IP to handle interrupts efficiently. Learn about the significance of interrupt service routines, interrupt handling process, and how to generate interrupts in MicroBlaze for seam

0 views • 30 slides

Understanding Processor Cycles and Machine Cycles in 8085 Microprocessor

Processor cycles in microprocessors like 8085 involve executing instructions through machine cycles that are essential operations performed by the processor. In the 8085 microprocessor, there are seven basic machine cycles, each serving a specific purpose such as fetching opcodes, reading from memor

0 views • 17 slides

Understanding Exceptional Control Flow in Computer Systems

Control flow mechanisms in computer systems have evolved to handle exceptional events triggered by external system states. This includes exceptions, interrupts, and context switches that enable the CPU to respond to events like data arrival, user inputs, and system timeouts. Exception handling invol

0 views • 66 slides

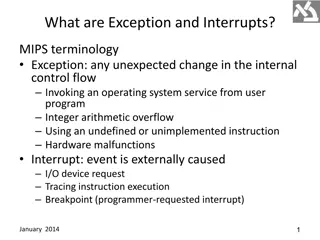

Exception Handling and Interrupts in MIPS Architectures

Exception and interrupts in MIPS play a crucial role in handling unexpected events and external requests efficiently. Exceptions include changes in control flow, arithmetic overflows, and hardware malfunctions, while interrupts are externally caused events like I/O requests. When an exception occurs

1 views • 29 slides

Understanding Processor Organization in Computer Architecture

Processor organization involves key tasks such as fetching instructions, interpreting instructions, processing data, and storing temporary data. The CPU consists of components like the ALU, control unit, and registers. Register organization plays a crucial role in optimizing memory usage and control

0 views • 21 slides

Understanding Processor Structure and Function in Computing

Explore the key components and functions of processors in computing, including user-visible and control status registers, instruction cycle, instruction pipelining, processor tasks like data processing and instruction interpretation, and the roles of arithmetic and logic units and control units. Lea

0 views • 61 slides

Understanding Processor Generations and VM Sizing for Azure Migration

Exploring the impact of processor generations on CPU performance, factors like clock speed, instruction set, and cache size are crucial. Choosing the right-sized VM plays a vital role in optimizing Azure migration. Passmark CPU Benchmark results provide insights on Intel processor generations for Az

0 views • 9 slides

Understanding User and Kernel Modes in Operating Systems

The content provided discusses various aspects of user and kernel modes in operating systems through a set of true/false questions related to user programs, CPU interrupts, heap management, and process behavior in different modes. It touches on the role of the kernel in managing virtual memory, hand

0 views • 10 slides

Understanding Context Switching and User-Kernel Interaction in Operating Systems

Context switching in operating systems involves a seamless transition between user-level threads without the kernel's awareness. User-level code manages register state and stack pointers, while user-kernel mode switching requires changing processor privilege levels and agreement on information excha

0 views • 25 slides