Understanding Interrupts in Computer Systems

Interrupts in computer systems play a crucial role in handling various events and managing the flow of instructions. This content discusses the types of interrupts, causes, handling procedures, and the role of supervisory modes in modern computers. It covers topics such as internal and external interrupts, register management during interrupts, interrupt handling procedures, and the transition to supervisory mode for privileged access. Additionally, it addresses common scenarios such as arithmetic overflow and divide-by-zero errors.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

COMP541 Interrupts, DMA, Serial I/O Montek Singh Nov 19, 2014 1

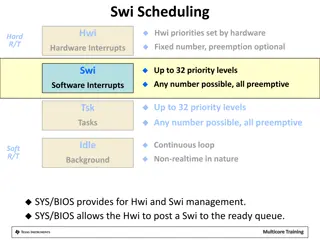

Interrupts Two main kinds Internal Error when executing an instruction Floating point exception Virtual memory page fault Trying to access protected memory Invalid opcode! System call requested by software To request OS services External I/O 2

Internal More complicated because two possible actions may abort instruction access to protected memory not allowed or, OS corrects the situation and restarts instruction e.g., virtual memory page fault Question: What happens for arithmetic overflow/divide-by-0? 3

When Interrupt Occurs Interrupt enable register Sometimes levels of interrupts individually enabled/disabled PC is changed to new location One or more interrupt locations stored vectored interrupts Or a fixed location example: MIPS (e.g., 0xC000 0000) Old PC saved to register or stack Many machines have stack pointer 4

Registers Sometimes registers saved by hardware Some machines have one or more sets of registers Often: software must save registers Push them onto stack Return from interrupt Some CPUs provide a special instruction to return from interrupt rfi or iret Others use the standard procedure return instruction jr, ret, etc. Restore registers before returning 5

Cause of Interrupt Need way to determine what caused interrupt Note it can be more than one thing Vectored Interrupts Different types cause branches to different locations Sometimes prioritized Register to store cause Cause register 6

Supervisory Mode Modern computers have user mode and one or more supervisory modes User mode restricted Can t write to many system registers, such as interrupt enable Can t write to some parts of memory Usually I/O restricted Interrupts cause switch to supervisory mode In this mode, software has access to several privileged parts of the system e.g.: kernel memory, IE register, etc. Question: Which interrupts? 7

Some Interrupt Hardware An example implementation Interrupts ORed Response if IE and at end of instruction Ack interrupt Vector address to PC new PC calculated using the interrupt number e.g., IntNum * a + b Save current PC on stack to return 8

Return from interrupt Very similar to return from procedure Some additional actions PSR holds IE bit Restoring PSR turns interrupts on 9

Exception (from Patterson Hennessey, multicycle MIPS) MIPS has a simpler impl. Branch to fixed addr PC 4 stored Just two causes Undefined instruction and arithmetic overflow 10

Restarting Instruction? Imagine the interrupt (exception) was a page fault Need to get the page, and then rerun the instruction Hence: subtract 4 from PCPlus4, so this instruction is redone Keeping instructions simple/short helps out! Otherwise may need to save some intermediate state Imagine block-move instruction such as the Pentium MOVS moves/copies an entire string (of variable length) in a single instruction! 11

Types of I/O Programmed I/O Direct Memory Access (DMA) 12

Direct Memory Access (DMA) Programmed I/O is when CPU reads/writes every word Specific instructions included for I/O, e.g.: in 0xff00 out 0xffe0 Problem: overhead is high; nothing else getting done on CPU Especially for mass-storage devices like disk DMA: Let device controller read/write mem directly CPU goes about its usual business of executing other instructions delegates the reading/writing to DMA controller typically cannot access memory while DMA is going on! 13

DMA Protocol DMA protocol DMA device takes over main bus Becomes bus master Asserts addresses Basically interfaces to memory or memory controller 14

How? DMA device requests bus (assert BR) CPU grants request (assert BG) CPU takes its signals to Hi-Z now DMA can use its signals to connect with memory no conflict with CPU s signals (they are floating) 15

Transfer Modes Several types of transfer modes Continuous: DMA controller transfers all data (say a disk sector) at once As many memory cycles as data Burst: DMA controller cycle steals, takes a cycle at end of every CPU instruction Note: today s processors are more sophisticated there is a memory controller ( Northbridge ) sits in-between CPU and memory Why? Memories are more complex, caches, etc. 1

End of DMA Controller needs to inform CPU De-assert BR Then CPU lowers BG and proceeds 17

DMA Controller Needs typical I/O signals Interrupt request Status of device Also needs controls for DMA transfer Memory address Word count 18

Typical Driver Interface Software drivers Set the memory address Set word count Assert GO (usually bit in control word) DMA controller starts copying and requests interrupt when transfer complete 20

Trends in Communications Older bus standards, such as ISA and PCI, were parallel (conventional bus ) Newer (PCI Express) use serial channels (lanes) So slots for slower devices can be x1 Slots for devices such as GPUs can be x16 (max x32 in spec) 16 lane PCI-E (below) 1 lane (right)

Disks Change from ATA/IDE to SATA IDE had 16 data channels SATA has 2 twisted pair (xmit and recv)

RS-232/UART Called Asynchronous But both sides have precise clocks Agree on speed Receiver syncs during start bit 23

USB One master The PC Idea was to have thin cables and plug and play Specs include hardware and software We only cover hardware 24

USB Packet serial I/O Four wires total +5v and GND Two signal wires Twisted pair Differential signaling Differential 1 is D+ > 2.8v and D- < 0.3v Differential 0 is opposite Also a single-ended zero when D+ & D- low (end of packet, reset, disconnect) 25

Speed Three speeds High is 480 Mb/s (USB 2.0) Full is 12 Mb/s (USB 1.1) Low is 1.5 Mb/s (USB 1.0) New Super Speed, 5Gb/s!! (USB 3.0) High speed starts as full, then handshakes and transitions High and low speeds interpret zeros and ones inverted 26

Coding NRZI Non-Return to Zero Inverted Transition if sending 0, none if sending 1 Bit stuffing Since a string of 1s causes no transitions, synchronization may be lost A zero is stuffed in after six consecutive ones Sync field Each packet starts with a sync 8 bits: 00000001 27

Packets Won t go into details 28

Summary Many types of I/O memory-mapped is most common different devices given different address ranges many different device protocols PS/2: keyboard, mice RS-232: serial ports USB: most common today also Firewire, Thunderbolt, ethernet also monitors, displays we did VGA (other higher resolutions also possible) DVI is most common today 29