Development of Multiclock Cycle in Processor

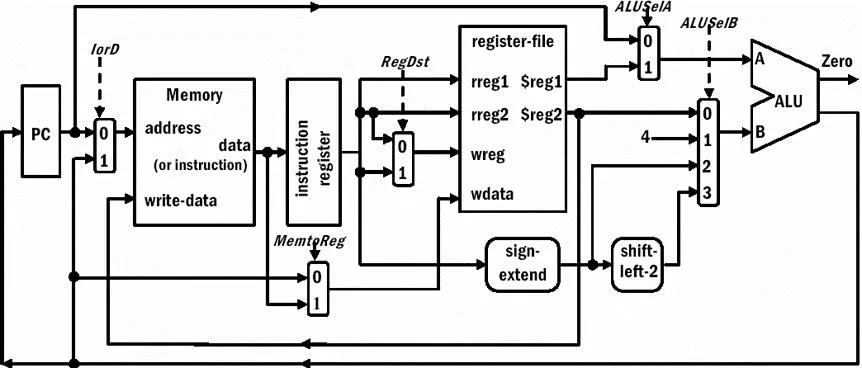

The development process of the multiclock cycle in a processor is explained in detail through different steps, including instruction fetch, decode, register fetch, execution, and write-back for R-type instructions. Control lines and branching execution are also covered in the description. The content provides insights into the intricate workings of processor cycles and highlights key operations involved at each stage.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

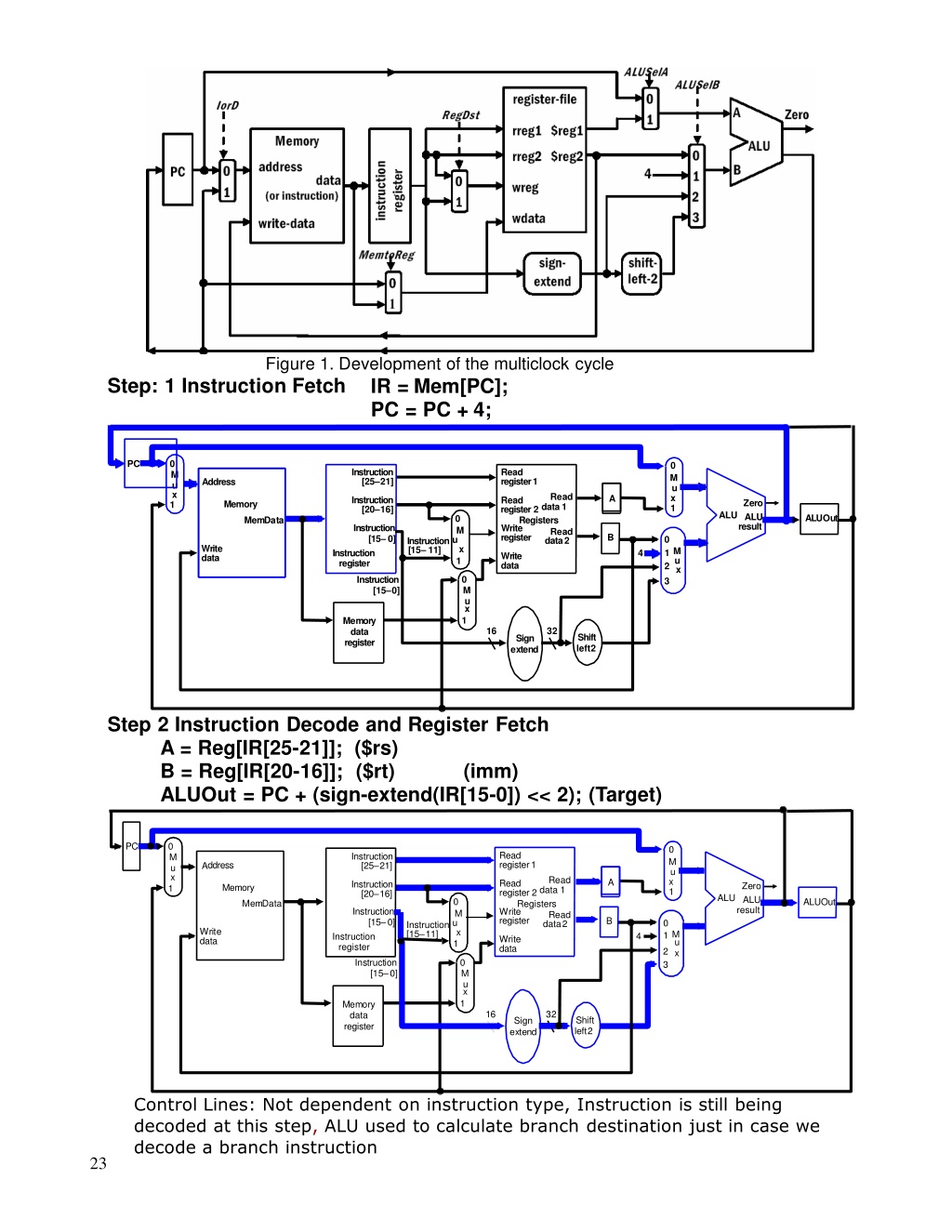

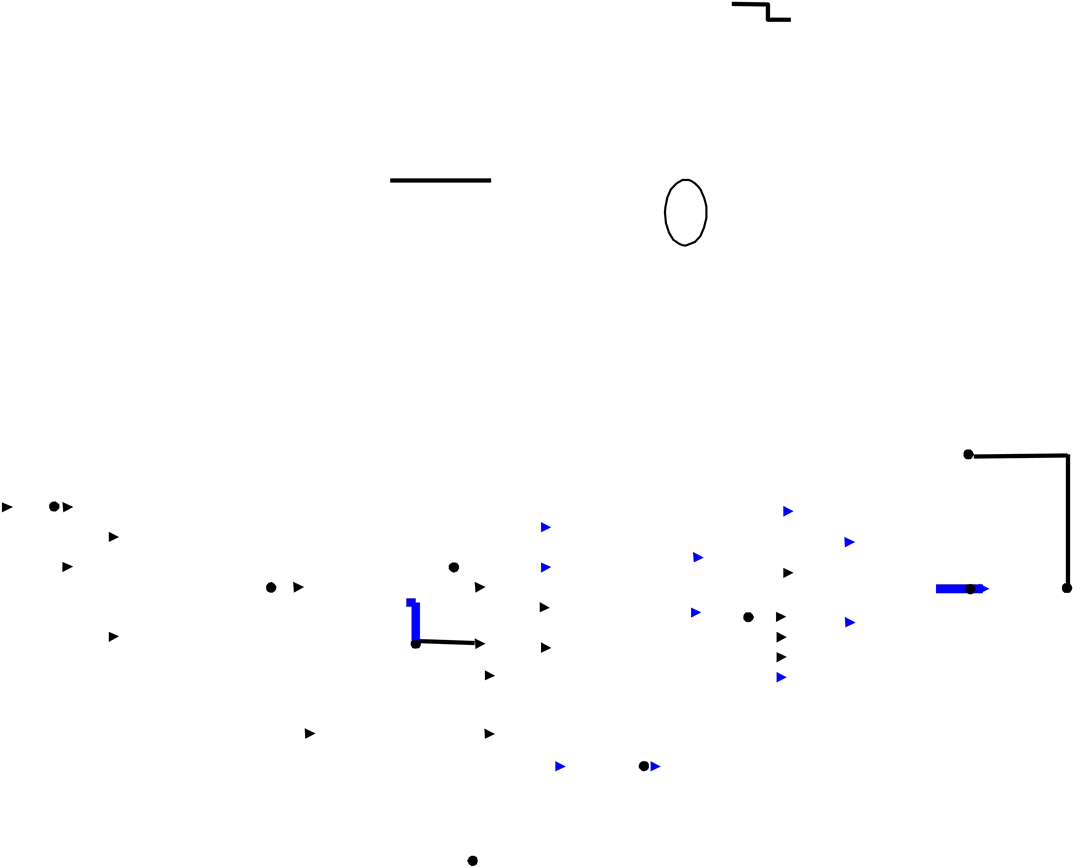

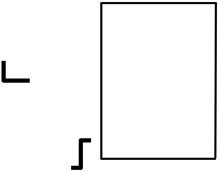

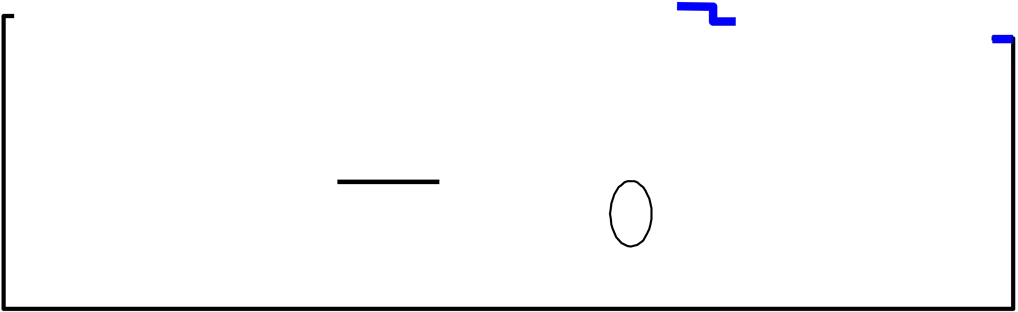

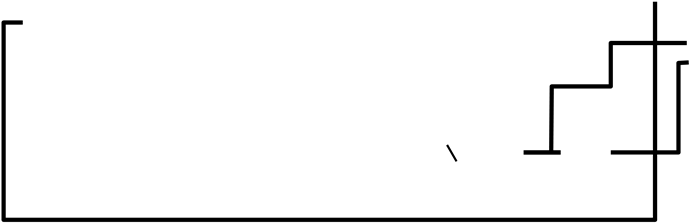

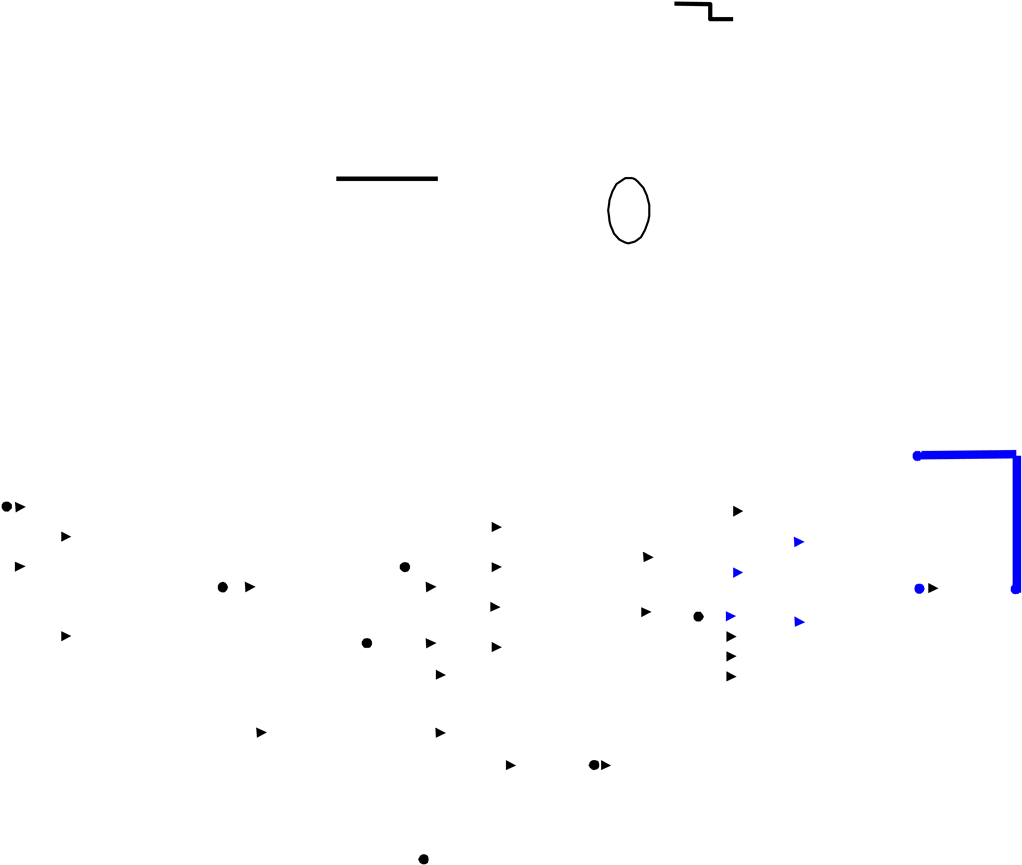

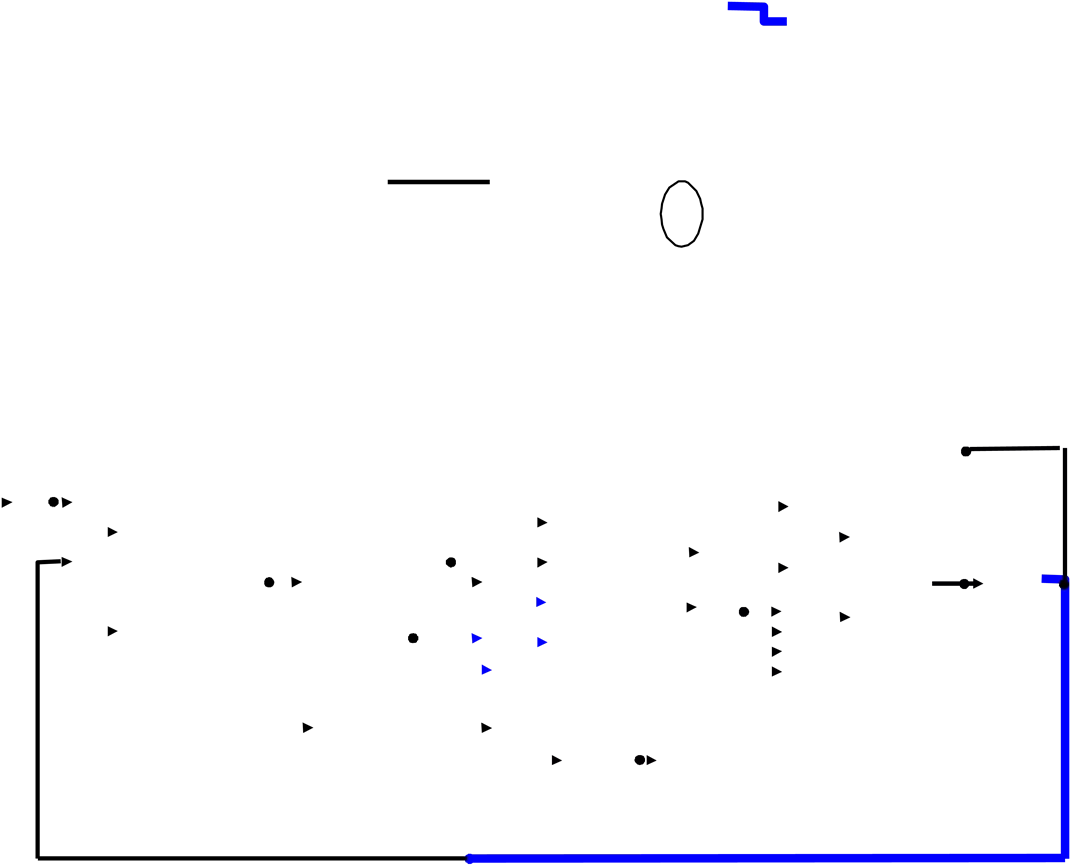

Figure 1. Development of the multiclock cycle Step: 1 Instruction Fetch IR = Mem[PC]; PC = PC + 4; PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Instruction [20 16] Read register 2 data 1 Registers Write Zero Memory ALU ALU result ALUOut 0 MemData Instruction [15 0] Instruction register M Read data2 register B 0 Instructionu [15 11] Write data x 1M 2u 4 Write data 1 x 0 M u x 1 Instruction [15 0] 3 Memory data register 16 32 Shift left2 Sign extend Step 2 Instruction Decode and Register Fetch A = Reg[IR[25-21]]; ($rs) B = Reg[IR[20-16]]; ($rt) ALUOut = PC + (sign-extend(IR[15-0]) << 2); (Target) (imm) PC 0 M u x 1 0 M u x 1 Read register1 Instruction [25 21] Address Read A Read register 2 data 1 Registers Write Instruction [20 16] Zero Memory ALU ALU result 0 ALUOut MemData Instruction [15 0] Instruction register M Read data2 register B Instructionu [15 11] 0 1 M Write data x 4 Write data u 1 2 x Instruction [15 0] 0 M u x 1 3 Memory data register 16 32 Shift left2 Sign extend Control Lines: Not dependent on instruction type, Instruction is still being decoded at this step, ALU used to calculate branch destination just in case we decode a branch instruction 23

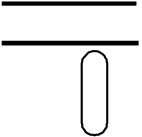

Step 3 R-Type Execution ALUOut = A op B; PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Read register 2 data 1 Registers Write Instruction [20 16] Zero Memory ALUALU result ALUOut 0 MemData Instruction [15 0] Instruction register M Read data2 register B 0 1M 2u Instruction u [15 11] Write data x 4 Write data 1 x Instruction [15 0] 0 M u x 1 3 Memory data register 16 32 Shift left2 Sign extend Step 4 R-Type Write Back Reg[IR[15-11]] = ALUOut; ($rd ALUOut) This is the last step for R-Type PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Read register 2 data1 Instruction [20 16] Zero Memory ALUALU ALUOut 0 MemData Registers Write register result Instruction [15 0] M Read data2 B Instructionu [15 11] 0 1M 2 x 1 Write data 4 Instruction register Write data u x 0 M u x 1 Instruction [15 0] 3 Memory data register 16 32 Shift left2 Sign extend Step 3: Branch Execution if (A == B) PC = ALUOut (target) This is the last step for Branch PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Read register 2 data1 Instruction [20 16] Zero Memory ALUALU result ALUOut 0 MemData Registers Write register Instruction [15 0] M Read data2 B 0 1M 2 Instruction u [15 11] Write data x 4 Instruction register Write data u 1 x Instruction [15 0] 0 M u x 1 3 Memory data register 16 32 Sign extend Shift left2 24

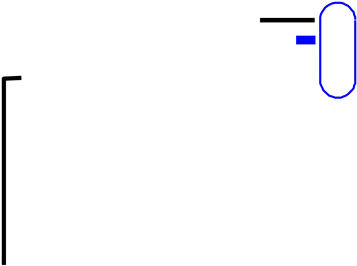

Step 3: Memory Execution ALUOut = A + sign-extend(IR[15-0]); PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Instruction [20 16] Read register 2 data 1 Registers Write Zero Memory ALU ALU result ALUOut 0 MemData Instruction [15 0] Instruction register M Read data2 register B 0 1M 2 Instruction u [15 11] Write data x 4 Write data u 1 x Instruction [15 0] 0 M u x 1 3 Memory data register 16 32 Shift left2 Sign extend Step 4: Load Memory MDR = Memory[ALUOut]; PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Read register 2 data1 Instruction [20 16] Zero Memory ALUALU ALUOut 0 MemData Registers Write register result Instruction [15 0] M Read data2 B 0 1 M 2 Instruction u [15 11] x 1 Write data 4 Instruction register Write data u x Instruction [15 0] 0 3 M u x 1 Memory data register 16 32 Sign extend Shift left2 Step 4: Store Write Back Memory[ALUout] = B; This is the last step for Store PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Read register 2 data 1 Registers Write Instruction [20 16] Zero Memory ALU ALU ALUOut 0 MemData result Instruction [15 0] M Read data2 register B 0 1M 2 Instruction u [15 11] x Write data 4 Instruction register Write data u 1 x 0 Instruction [15 0] 3 M u x 1 Memory data register 16 32 Shift left2 Sign extend 25

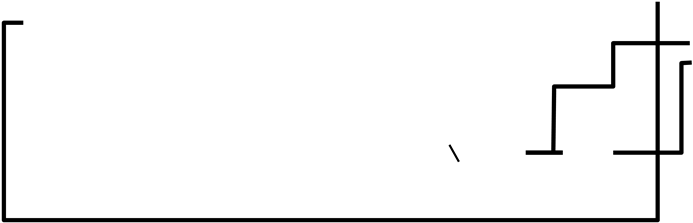

Step 5: Load Write Back Reg[IR[20-16]] = MDR; This is the last step for Load PC 0 0 M u x 1 Instruction [25 21] Read register1 M u x 1 Address Read A Read register 2 data 1 Registers Write Instruction [20 16] Zero Memory ALU ALU ALUOut 0 MemData result Instruction [15 0] M Read data2 register B 0 1M 2 Instruction u [15 11] Write data x 1 4 Instruction register Write data u x Instruction [15 0] 0 3 M u x 1 Memory data register 16 32 Shift left2 Sign extend

1; 1; 1; 00; 1; 27