Understanding Electromigration Effects in IC Interconnect Lines

Background: As IC circuits advance, preventing failures like electromigration is crucial. Vacancies lead to potential failures in metal interconnects by causing macroscopic voids and hillocks. Explore the governing equations and physics interfaces behind the migration of vacancies in IC circuits. Im

0 views • 14 slides

Understanding CMOS Layers and Interconnect Design in Semiconductor Manufacturing

This content provides detailed insights into the CMOS layers, n-well process, p-well process, twin-tub process, metal interconnect layers, gate design, and layout strategies involved in semiconductor manufacturing. Explore the images and descriptions to grasp the complexities of MOS arrays, gate con

0 views • 27 slides

Analysis of "The Scarlet Ibis" by James Hurst

In "The Scarlet Ibis" by James Hurst, the narrator reflects on his relationship with his physically disabled brother, Doodle. Set in the American South during WWI, the story explores themes of brotherhood, fear, and the consequences of pride and cruelty. Through the protagonist's actions and the tra

0 views • 18 slides

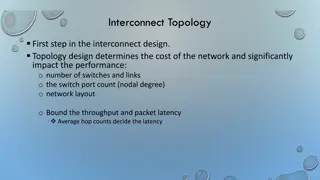

Understanding Interconnect Topology Design and Performance Metrics

Interconnect topology design plays a crucial role in determining the cost and performance of a network. Factors such as the number of switches and links, switch port count, network layout, throughput, packet latency, average hop counts, nodal degree, hop count, and diameter are essential considerati

0 views • 38 slides

Challenges in ERCOT Transmission Infrastructure & Operations

Poor transmission infrastructure and restrictive interconnect practices in ERCOT are leading to dangerous operations, congestion issues, and generation revenue impacts. Concerns include increased RAS proposals, challenges with GTC management, and minimalist interconnect processes. The need for impro

0 views • 9 slides

Comprehensive Overview of myResearch Portal for Sponsored Research at ORIS

Real-time web-based access to administrative data related to primary investigator's sponsored research at ORIS. The portal includes features for compliance approvals, financial accounts management, and delegation control. Access is granted to PSU employees with DUO authentication. Financial data fro

0 views • 18 slides

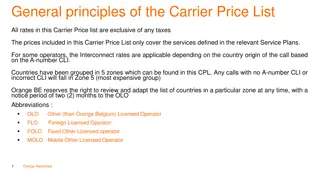

Overview of Carrier Price List and Country Groupings

The Carrier Price List outlines rates exclusive of taxes, covering defined services. Countries are grouped into zones, affecting interconnect rates. The list includes Zone 1 (Belgium, EU, EFTA, China, India) and subsequent groups. Orange BE may adjust country zoning.

0 views • 8 slides

IBIS Interconnect: Models and Task Group Overview

The IBIS Interconnect draft explores models representing package and on-die interconnect, with separate or combined approaches for on-die, package, supply, and signal interconnect. The IBIS Interconnect Task Group, comprising major contributors such as Altera, Cadence Design Systems, Intel Corp, and

0 views • 10 slides

Overview of IBIS Interconnect Task Group Models

The IBIS Interconnect Task Group focuses on modeling package and on-die interconnects, with support for separate or combined interconnect models. They meet weekly to discuss contributions from major companies like Altera, Cadence, Intel, and more. The models include terminals for differential signal

0 views • 17 slides

Understanding Net Metering with FPUA Fort Pierce Utilities Authority

Net metering enables customers to own or lease renewable generation, interconnect with the electric system, and offset consumption. Customers can use solar energy in their homes and the excess energy generated can be sold back to the grid. The rate utilities pay for excess generation varies and is s

0 views • 11 slides

Unified Approach for Performance Evaluation and Debug of System on Chip in Early Design Phase

This presentation discusses the challenges related to system-on-chip design, focusing on bandwidth issues, interconnect design, and DDR efficiency tuning. It explores the evolution of performance evaluation methods and the limitations of existing solutions. The need for a unified approach for early-

0 views • 28 slides

Machine Learning of Interconnect Coupling Delay and Transition Effects

This research paper explores the use of machine learning to study interconnect coupling delay and transition effects in VLSI design. It discusses the challenges of calibrating non-SI to SI timing reports, the impact of clock period adjustments on path slack, and the complexities involved in the cali

0 views • 32 slides

Understanding Cache Coherency and Multi-Core Programming

Explore the intricate world of cache coherency and multi-core programming through images and descriptions covering topics such as how cache shares data between cores, maintaining data consistency, CPU architecture, memory caching, MESI protocol, and interconnect bus communication.

0 views • 97 slides

Cutting-Edge Interconnect Technology for High-Performance Computing

Explore the world of high-performance embedded computing through images and descriptions detailing key components like terrestrial autonomous vehicles, wireless infrastructure, FPGA-based data exchange, and more. The content dives into fault tolerance, data processing, redundant computing, and hardw

0 views • 12 slides

Enhancing IBIS-AMI Models for Improved Signal Sampling

Proposed by Hansel Desmond Dsilva and team, this draft suggests adding a new parameter in the AMI_Init flow to provide sampling position details, addressing a key gap in IBIS-AMI specifications. The proposal aims to enhance accuracy and consistency for silicon design across EDA tools, advocating for

0 views • 21 slides

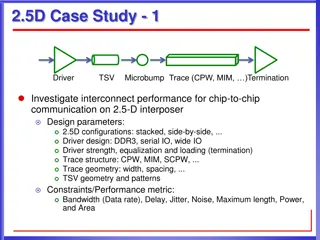

Investigating Chip-to-Chip Communication Performance on 2.5D Interposer

Investigate the performance of chip-to-chip communication on a 2.5D interposer by analyzing interconnect parameters such as configurations, driver design, trace structure, TSV geometry, and channel modeling. Explore methods like SPICE simulation and MATLAB GUI for performance estimation and optimiza

0 views • 18 slides

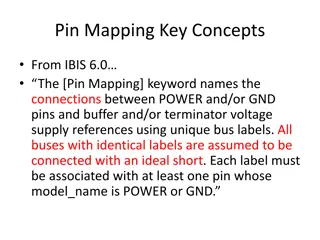

Understanding Pin Mapping and Interconnect in IBIS 6.0

Pin Mapping in IBIS 6.0 defines the connections between POWER/GND pins and buffer/terminator voltage supplies using unique bus labels. Interconnects between VDD pins and buffer supply terminals are crucial, with all pins associated with a named supply being shorted together. Draft 9 Interconnects an

0 views • 6 slides

Understanding Idempotence Bugs in Intermittent Systems

Energy-harvesting devices enable computing in inaccessible environments, but intermittent execution can lead to bugs and inconsistent updates. The impact of I/O-dependent idempotence bugs in intermittent systems is explored, highlighting the challenges and the need for tools like IBIS for bug detect

0 views • 28 slides

InterConnect A/S - Driving Innovation in Legal Technology

InterConnect A/S, established in 1996 in Svendborg, Denmark, specializes in software development and ERP/database systems. As a key player in the LIT Pilot Project, they are actively involved in developing a search machine for legal interpreters and translators. With a strong track record in project

0 views • 16 slides

High-Performance Gate Sizing with Signoff Timer: VLSI Design Challenges

This study delves into the intricate realm of gate sizing in VLSI design, focusing on optimizing power and delay through effective approaches and addressing challenges such as interconnect delay, inaccurate internal timers, and critical paths. Previous gate sizing techniques are evaluated, and a met

0 views • 34 slides

Understanding Changes in IBIS 6.2 Editorial Resolutions

Explore key updates in the IBIS 6.2 Editorial Resolutions, including new definitions, GND usage clarification, DUT vs. DIA descriptions, and model name guidelines. Learn about the distinctions between Device Under Test (DUT) and Device In Action (DIA) in IBIS files. Discover how IBIS files describe

0 views • 21 slides

Energy-Aware Optimization of BEOL Interconnect Stack Geometry

This study focuses on optimizing Back-End-of-Line (BEOL) interconnect stack geometry in advanced nodes for improved performance and energy efficiency. It explores the motivations, background, and potential benefits of Design-Aware Manufacturing (DAM) and Manufacturing-Aware Design (MAD) methodologie

0 views • 28 slides

Conference Venue and Accommodation Information for University of Paris-Est Creteil Event

The conference will be held at the Maison des Sciences de l'Environnement at the OSU-EFLUVE Observatory of University of Paris-Est Creteil in Creteil, France. The venue address is 5 Rue Pasteur Vallery Radot. Nearby hotels include Novotel Paris Creteil Le Lac and Hotel Ibis Creteil, providing conven

0 views • 4 slides