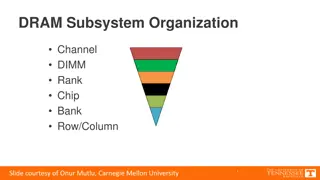

Understanding the Organization of DRAM Subsystem Components

Explore the intricate structure of the DRAM subsystem, including memory channels, DIMMs, ranks, chips, banks, and rows/columns. Delve into the breakdown of DIMMs, ranks, chips, and banks to comprehend the design and functioning of DRAM memory systems. Gain insights into address decoding, row/column

0 views • 16 slides

Computer Architecture: Understanding SRAM and DRAM Memory Technologies

In the field of computer architecture, SRAM and DRAM are two prevalent memory technologies with distinct characteristics. SRAM retains data as long as power is present, while DRAM is dynamic and requires data refreshing. SRAM is built with high-speed CMOS technology, whereas DRAM is more dense and b

3 views • 38 slides

Improving Low-Latency Buffer Status Reporting in IEEE 802.11

Proposal for enhancing the Buffer Status Report (BSR) mechanism in IEEE 802.11 to include timing constraints for transmitting latency-sensitive traffic. Suggestions involve adding TSPEC-based signaling and efficient mechanisms for Enhanced Traffic APs to ascertain low-latency traffic status. The cur

0 views • 12 slides

High-Throughput True Random Number Generation Using QUAC-TRNG

DRAM-based QUAC-TRNG provides high-throughput and low-latency true random number generation by utilizing commodity DRAM devices. By employing Quadruple Row Activation (QUAC), this method outperforms existing TRNGs, achieving a 15.08x improvement in throughput and passing all 15 NIST randomness tests

0 views • 10 slides

SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Processing Using DRAM

SIMDRAM introduces a novel framework for efficient computation in DRAM, aiming to overcome data movement bottlenecks. It emphasizes Processing-in-Memory (PIM) and Processing-using-Memory (PuM) paradigms to enhance processing capabilities within DRAM while minimizing architectural changes. The motiva

2 views • 14 slides

Analyzing and Improving Latency in IEEE 802.11 Networks

The document discusses controlling latency in IEEE 802.11 networks to meet the demands of emerging applications that require not only high throughput but also low latency. It covers aspects such as latency analysis, potential improvements, latency vs. reliability trade-offs, and latency improvement

4 views • 14 slides

Evaluation of Low-Latency Services in IEEE 802.11-23/1530r1

This document discusses the evaluation of supported low-latency services in the context of IEEE 802.11-23/1530r1, focusing on the reliability of WLAN, throughput, latency, and MPDU loss. It addresses the challenges in supporting new low-latency services such as AR/VR and industrial IoT, particularly

1 views • 11 slides

Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the n

0 views • 43 slides

Low Latency Requirements in Ultra-High Rate Communication

This document discusses the requirements and use cases of low latency in ultra-high rate communication scenarios, highlighting applications such as metaverse, cloud gaming, real-time video streaming, in-vehicle infotainment, and industrial PLC control. It also covers current methods to reduce latenc

1 views • 12 slides

Improving GPGPU Performance with Cooperative Thread Array Scheduling Techniques

Limited DRAM bandwidth poses a critical bottleneck in GPU performance, necessitating a comprehensive scheduling policy to reduce cache miss rates, enhance DRAM bandwidth, and improve latency hiding for GPUs. The CTA-aware scheduling techniques presented address these challenges by optimizing resourc

0 views • 33 slides

Enhancing Web Search Latency with DDS Prediction

This presentation delves into DDS Prediction, a technique designed to reduce extreme tail latency in web search engines by optimizing query execution times and parallelizing specific queries. It addresses the challenges of improving latency for all users and emphasizes the importance of achieving hi

0 views • 31 slides

Understanding Sources of Tail Latency in Hardware, OS, and Applications

Delve into the impact of latency on revenue, with real-world examples from companies like Amazon and Google. Explore the complexities of achieving low tail latency in large-scale applications and the approach to analyzing and mitigating latency sources at hardware, OS, and application levels.

0 views • 24 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

0 views • 48 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Understanding RowPress: A New Read Disturbance Phenomenon in Modern DRAM Chips

Demonstrating and analyzing RowPress, a novel read disturbance phenomenon causing bitflips in DRAM chips. Different from RowHammer vulnerability, RowPress showcases effective solutions on real Intel systems with DRAM chips.

0 views • 46 slides

Managing DRAM Latency Divergence in Irregular GPGPU Applications

Addressing memory latency challenges in irregular GPGPU applications, this study explores techniques like warp-aware memory scheduling and GPU memory controller optimization to reduce DRAM latency divergence. The research delves into the impact of SIMD lanes, coalescers, and warp-aware scheduling on

0 views • 33 slides

Panopticon: Complete In-DRAM Rowhammer Mitigation

Despite extensive research, DRAM remains vulnerable to Rowhammer attacks. The Panopticon project proposes a novel in-DRAM mitigation technique using counter mats within DRAM devices. This approach does not require costly changes at multiple layers and leverages existing DRAM logic for efficient miti

0 views • 17 slides

Impact of Latency on Player Performance in Cloud-based Games

Research conducted by Mark Claypool and David Finkel explores the effects of latency on player performance in cloud-based games. The study compares the impact of latency on both objective (performance) and subjective (quality) measures, highlighting how every 100ms increase in latency results in a 2

0 views • 21 slides

Enhancing Low Latency in IEEE 802.11 Networks

Various mechanisms for low latency in IEEE 802.11 networks are discussed, including C-TDMA, C-RTWT, TXOP Preemption, and HiP-EDCA. This proposal aims to improve initial control frame exchanges to prioritize low latency traffic transmission. By modifying exchange rules and allowing STAs to signal the

0 views • 12 slides

Understanding DRAM Errors: Implications for System Design

Exploring the nature of DRAM errors, this study delves into the causes, types, and implications for system design. From soft errors caused by cosmic rays to hard errors due to permanent hardware issues, the research examines error protection mechanisms and open questions surrounding DRAM errors. Pre

0 views • 31 slides

Achieving Bounded Latency in Data Centers: A Comprehensive Study

Data centers face challenges in providing consistent low latencies due to in-network interference and varying workloads. This study explores solutions to guarantee strong latency performance, mitigate latency variance, and minimize performance degradation for latency-sensitive applications. By analy

0 views • 18 slides

Challenges and Solutions in Memory Hierarchies for System Performance Growth

The evolution of memory scaling poses challenges for system performance growth due to limitations in memory hierarchy, capacity gaps, and DRAM scaling obstacles. The need for alternative technologies and architectural support to address these challenges is highlighted, focusing on reducing latency,

0 views • 23 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

0 views • 37 slides

Latency Measurement in IEEE 802.11 for Low Latency Applications

IEEE 802.11-20/0484r0 discusses the importance of latency measurement for low latency applications in WLAN technologies. The document emphasizes the need for improved worst-case latency and jitter, addressing interference issues to ensure guaranteed latency for scheduled transmissions. Various contr

0 views • 13 slides

Understanding Latency in JESD204B Links

Latency in a JESD204B link refers to the time it takes for a signal to travel from input to output, influenced by factors like system setup, device dependencies, clock propagation delays, and signal alignment. Definitions such as Sample-to-Serial Out (S2SO), Link Delay, and Link Latency are crucial

0 views • 46 slides

Understanding Power Consumption in Memory-Intensive Databases

This collection of research delves into the power challenges faced by memory-intensive databases (MMDBs) and explores strategies for reducing DRAM power draw. Topics covered include the impact of hardware features on power consumption, experimental setups for analyzing power breakdown, and the effec

0 views • 13 slides

Multi-AP Preemption for Low-Latency Traffic in IEEE 802.11 Networks

Discussion on the necessity of Multi-AP preemption for low-latency traffic in IEEE 802.11 networks. Addresses issues related to latency-sensitive traffic in overlapping basic service sets (OBSS). Proposes a general solution to enable OBSS APs to transmit urgent low-latency traffic without significan

0 views • 9 slides

New Queue Mechanism for Real-Time Application Considerations in July 2019

In July 2019, considerations were made for a new queue mechanism for real-time applications. The focus was on improving worst-case latency and jitter for latency-critical traffic, such as in online mobile gaming and manufacturing control. The proposed design aims to link access delay directly to req

0 views • 9 slides

Enhancing GPGPU Performance through Inter-Warp Heterogeneity Exploitation

This research focuses on addressing memory divergence issues in GPGPUs by exploiting inter-warp heterogeneity. By prioritizing mostly-hit warps and deprioritizing mostly-miss warps through Memory Divergence Correction (MeDiC), significant performance and energy efficiency improvements were achieved

0 views • 45 slides

Multi-AP Coordination for Low Latency Traffic Transmission

The document discusses the integration of multi-access point (AP) coordination to enhance the transmission of low-latency traffic in wireless networks. It addresses the challenges and introduces modes of operation capable of reducing latency and improving reliability for low-latency (LL) traffic tra

0 views • 9 slides

Enhancing DRAM Performance with ChargeCache: A Novel Approach

Reduce average DRAM access latency by leveraging row access locality with ChargeCache, a cost-effective solution requiring no modifications to existing DRAM chips. By tracking recently accessed rows and adjusting timing parameters, ChargeCache achieves higher performance and lower DRAM energy consum

0 views • 33 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

Overlapped Indication for Event-Based Low Latency Traffic Support in IEEE 802.11

The document discusses the importance of reducing latency in Ultra High Rate (UHR) PAR and Event Based Low Latency (LL) traffic support in IEEE 802.11 networks. It introduces the concept of preemption to enhance LL traffic handling and proposes an overlapped LL indication frame to address challenges

0 views • 13 slides

Understanding Memory System Design Tradeoffs in Computer Architecture

Explore the complexities of designing a memory system for computer architecture. Delve into the tradeoffs between area, power, and latency, considering the limitations of using only flip-flops, SRAM cells, or DRAM cells. Discover the challenges in creating an efficient memory system that balances st

0 views • 88 slides

CLR-DRAM: Dynamic Capacity-Latency Trade-off Architecture

CLR-DRAM introduces a low-cost DRAM architecture that enables dynamic configuration for high capacity or low latency at the granularity of a row. By allowing a single DRAM row to switch between max-capacity and high-performance modes, it reduces key timing parameters, improves system performance, an

0 views • 42 slides

Locality-Aware Caching Policies for Hybrid Memories

Different memory technologies present unique strengths, and a hybrid memory system combining DRAM and PCM aims to leverage the best of both worlds. This research explores the challenge of data placement between these diverse memory devices, highlighting the use of row buffer locality as a key criter

1 views • 34 slides

Understanding Divergence and the Divergence Theorem in Vector Fields

This content discusses the concept of divergence and the divergence theorem in vector fields through detailed examples and explanations. It covers topics such as finding divA in different coordinate systems, calculating charge density in regions based on given vector fields, and applying the diverge

0 views • 8 slides

IEEE 802.11-19/1942r1 Timing Measurement for Low Latency Features

The document discusses the necessity of measuring latency and jitter for IEEE 802.11be low-latency functions. It emphasizes the importance of precise measurement methods to evaluate quality and control low-latency features effectively. The presentation highlights the need for timing measurement to r

0 views • 13 slides

Understanding the Impact of On-Die ECC on DRAM Error Characteristics

The BEER project explores how on-die ECC complicates DRAM reliability studies by concealing error characteristics. It aims to uncover the unique ECC function of DRAM chips and infer error locations in error-prone cells. The study highlights the challenges in identifying and correcting bit flips obfu

0 views • 17 slides