IEEE 802.11-23/1288r0 Bandwidth Utilization Proposal

This proposal aims to improve bandwidth utilization in IEEE 802.11 networks by allowing devices to transmit on idle channels within the operating bandwidth. It addresses the inefficiencies caused by the current limitation where devices do not transmit on idle portions if the primary channel is busy.

2 views • 24 slides

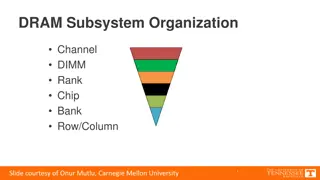

Understanding the Organization of DRAM Subsystem Components

Explore the intricate structure of the DRAM subsystem, including memory channels, DIMMs, ranks, chips, banks, and rows/columns. Delve into the breakdown of DIMMs, ranks, chips, and banks to comprehend the design and functioning of DRAM memory systems. Gain insights into address decoding, row/column

0 views • 16 slides

Challenges and Requirements for Bandwidth Indication in IEEE 802.11

The document discusses challenges and requirements related to bandwidth indication in RTS/CTS frames with PPDU in 320 MHz, focusing on scenarios where bandwidth signaling may lead to misinterpretation by stations. It highlights the need for dynamic bandwidth and preamble puncturing information in RT

3 views • 21 slides

Computer Architecture: Understanding SRAM and DRAM Memory Technologies

In the field of computer architecture, SRAM and DRAM are two prevalent memory technologies with distinct characteristics. SRAM retains data as long as power is present, while DRAM is dynamic and requires data refreshing. SRAM is built with high-speed CMOS technology, whereas DRAM is more dense and b

3 views • 38 slides

Proposal for Efficient Bandwidth Utilization in IEEE 802.11 Networks

This proposal aims to address the inefficient utilization of bandwidth in IEEE 802.11 networks by allowing stations to transmit on idle channels within their operating bandwidth. The document discusses the problem statement, high-level solution, relevant capabilities of transmitters and receivers, p

0 views • 15 slides

IEEE 802.11 Proposal for 320MHz Ranging Enhancement

This document discusses the proposal for enhancing IEEE 802.11 with support for 320MHz bandwidth ranging operations. It aims to improve ranging accuracy by expanding 802.11az frames and procedures to accommodate the increased bandwidth. The focus is on MAC-related changes, exploring different option

2 views • 26 slides

High-Throughput True Random Number Generation Using QUAC-TRNG

DRAM-based QUAC-TRNG provides high-throughput and low-latency true random number generation by utilizing commodity DRAM devices. By employing Quadruple Row Activation (QUAC), this method outperforms existing TRNGs, achieving a 15.08x improvement in throughput and passing all 15 NIST randomness tests

0 views • 10 slides

SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Processing Using DRAM

SIMDRAM introduces a novel framework for efficient computation in DRAM, aiming to overcome data movement bottlenecks. It emphasizes Processing-in-Memory (PIM) and Processing-using-Memory (PuM) paradigms to enhance processing capabilities within DRAM while minimizing architectural changes. The motiva

2 views • 14 slides

Understanding Performance Analysis of Digital Modulation Techniques

Explore the realm of digital modulation techniques such as ASK, FSK, PSK, QPSK, QAM, and more. Learn about bandwidth efficiency, baud rates, minimum bandwidth, and how to calculate them. Discover the importance of M-ary modulation and how it impacts data transmission rates and bandwidth requirements

4 views • 18 slides

Insights into DRAM Power Consumption and Design Concerns

Detailed experimental study reveals that DRAM power models may not provide accurate insights into power consumption. The increasing importance of managing DRAM power in system design is emphasized. The study delves into DRAM organization, operation, and power consumption patterns, highlighting the n

0 views • 43 slides

Improving GPGPU Performance with Cooperative Thread Array Scheduling Techniques

Limited DRAM bandwidth poses a critical bottleneck in GPU performance, necessitating a comprehensive scheduling policy to reduce cache miss rates, enhance DRAM bandwidth, and improve latency hiding for GPUs. The CTA-aware scheduling techniques presented address these challenges by optimizing resourc

0 views • 33 slides

Advances in White Light Cavity for Sensitivity and Bandwidth Optimization

The research discusses innovative ideas for enhancing sensitivity and bandwidth limits in the context of white light cavity technologies. It explores methods such as external/internal squeezing and signal recycling to surpass existing Mizuno Limits, shedding light on crucial issues for future upgrad

0 views • 27 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

0 views • 48 slides

Enhancing Support for Wider Bandwidth OFDMA in IEEE 802.11 Networks

The document discusses the implementation of Selective Spatial Transmission (SST) and Dynamic Subband Operation (DSO) to enable wider bandwidth OFDMA in IEEE 802.11be and 802.11bn standards. It covers enhancements for 80MHz, 160MHz, and 320MHz EHT DL and UL OFDMA transmissions, emphasizing the benef

0 views • 18 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Understanding RowPress: A New Read Disturbance Phenomenon in Modern DRAM Chips

Demonstrating and analyzing RowPress, a novel read disturbance phenomenon causing bitflips in DRAM chips. Different from RowHammer vulnerability, RowPress showcases effective solutions on real Intel systems with DRAM chips.

0 views • 46 slides

Panopticon: Complete In-DRAM Rowhammer Mitigation

Despite extensive research, DRAM remains vulnerable to Rowhammer attacks. The Panopticon project proposes a novel in-DRAM mitigation technique using counter mats within DRAM devices. This approach does not require costly changes at multiple layers and leverages existing DRAM logic for efficient miti

0 views • 17 slides

Understanding DRAM Errors: Implications for System Design

Exploring the nature of DRAM errors, this study delves into the causes, types, and implications for system design. From soft errors caused by cosmic rays to hard errors due to permanent hardware issues, the research examines error protection mechanisms and open questions surrounding DRAM errors. Pre

0 views • 31 slides

IEEE 802.11-23/2141r0 Dynamic Subband Operation Discussion

Discussion on Dynamic Subband Operation in IEEE 802.11-23/2141r0 focusing on enabling flexible bandwidth allocation between APs and non-APs for improved resource utilization and system performance. The proposal aims to address bandwidth mismatches and enhance efficiency in channel access allocation

0 views • 15 slides

Bandwidth and Packet Type Detection Schemes for 40-50GHz Millimeter Wave Communication Systems

The document discusses bandwidth and packet type detection schemes for 40-50GHz millimeter wave communication systems in IEEE 802.11aj specifications. It proposes a preamble design for auto-detection of bandwidth and packet type to improve channel estimation and decoding efficiency. By utilizing dif

0 views • 27 slides

Congestion Control for High Bandwidth-Delay Product Networks

This presentation discusses the challenges faced by TCP in high bandwidth-delay product networks, highlighting issues such as oscillations and instability. It explores solutions like adjusting aggressiveness based on feedback delay, decoupling efficiency and fairness control, and introduces XCP as a

0 views • 23 slides

Understanding Latency Variation in Modern DRAM Chips

This research delves into the complexities of latency variation in modern DRAM chips, highlighting factors such as imperfect manufacturing processes and high standard latencies chosen to boost yield. The study aims to characterize latency variation, optimize DRAM performance, and develop mechanisms

0 views • 37 slides

Optimized Content Transfer in Mesh Networks Using Bandwidth-Aware Chunking

This presentation by Gurdev Singh from Samsung addresses a technique for optimized content transfer in mesh networks by splitting content into file chunks based on the bandwidth of the channel. By considering the bandwidth or link quality of destination nodes, the content is divided so that lower ba

0 views • 20 slides

Enhancing Off-chip Bandwidth Utilization for Improved System Performance

Efficiently coordinating off-chip read/write bandwidth through the Bandwidth-aware LLC proposal yields a 12% performance improvement in an 8-core system across multiple workloads. This approach optimizes DRAM read latency, surpassing existing policies and filling performance gaps while confirming lo

1 views • 36 slides

Understanding Power Consumption in Memory-Intensive Databases

This collection of research delves into the power challenges faced by memory-intensive databases (MMDBs) and explores strategies for reducing DRAM power draw. Topics covered include the impact of hardware features on power consumption, experimental setups for analyzing power breakdown, and the effec

0 views • 13 slides

Time Distribution System R&D Update for Hyper-Kamiokande Experiment

In the February 2020 update, Stefano Russo from LPNHE Paris presented the progress on the time distribution system R&D for the Hyper-Kamiokande experiment. The focus is on implementing a bidirectional data exchange link with a large bandwidth capacity for synchronous, phase-deterministic protocol. T

0 views • 17 slides

Enhancing DRAM Performance with ChargeCache: A Novel Approach

Reduce average DRAM access latency by leveraging row access locality with ChargeCache, a cost-effective solution requiring no modifications to existing DRAM chips. By tracking recently accessed rows and adjusting timing parameters, ChargeCache achieves higher performance and lower DRAM energy consum

0 views • 33 slides

Understanding Bandwidth, Channel Capacity, and Noise in Communication Networks

Bandwidth is a crucial aspect of network capacity, describing the data transfer speed and carrying capacity of a channel. Channel capacity involves factors like data rate, bandwidth, noise, and error rate. Noise sources include thermal noise, impulse noise, and delay distortion, impacting signal qua

0 views • 5 slides

DeltaINT: General In-band Network Telemetry with Low Bandwidth Overhead

This paper discusses DeltaINT, a novel framework for in-band network telemetry aimed at reducing bandwidth overhead while ensuring high generality and convergence. It addresses the limitations of existing methods by providing theoretical analysis on bandwidth mitigation guarantees and offering softw

0 views • 20 slides

Meeting Home Networking Bandwidth Needs with GEPOF Technology

Gigabit Ethernet over Polymer Optical Fiber (GEPOF) is a promising technology addressing the growing bandwidth requirements in home networking. Advances in FTTH technology enable high-speed connections for Smart Homes, supporting services like cloud computing, 4K video streaming, and Internet of Thi

0 views • 15 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

Understanding Bandwidth and Dispersion in Fiber Optic Communication

This presentation provides a comprehensive overview of bandwidth and dispersion in fiber optic communication. It covers essential terminologies like microns, nanometers, millimeters, and dB, explaining concepts such as bandwidth capacity, dispersion cancellation, and modal bandwidth in multimode fib

0 views • 24 slides

Evolution of Communication Systems: From Bandwidth Division to Spread Spectrum

Third-generation communication systems utilize Pseudo-Noise (PN) codes to share bandwidth without interference, while first and second-generation systems divide bandwidth into smaller channels. PN codes are vectors with 1s and -1s, orthogonal to each other. Users transmit data using PN coding, combi

0 views • 14 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

Overview of UE RF Requirements for 35/45MHz Channel Bandwidth in 3GPP Meeting #97-e

The document discusses the introduction of 35/45MHz channel bandwidth in UE RF requirements for various bands. It covers equation-based requirements and limitations in UL configurations based on bandwidth allocation. The scope includes capturing content from the first round discussions and clarifyin

0 views • 16 slides

Enhancing Bandwidth of Channel State Information (CSI) for Wireless Sensing Applications

This submission delves into the necessity of expanding the bandwidth of Channel State Information (CSI) in wireless environments to cater to the demands of time-sensitive wireless sensing applications. It explores the implications of high-bandwidth CSI on enhancing wireless channel understanding, ac

0 views • 12 slides

CLR-DRAM: Dynamic Capacity-Latency Trade-off Architecture

CLR-DRAM introduces a low-cost DRAM architecture that enables dynamic configuration for high capacity or low latency at the granularity of a row. By allowing a single DRAM row to switch between max-capacity and high-performance modes, it reduces key timing parameters, improves system performance, an

0 views • 42 slides

Enhancing Memory Bandwidth with Transparent Memory Compression

This research focuses on enabling transparent memory compression for commodity memory systems to address the growing demand for memory bandwidth. By implementing hardware compression without relying on operating system support, the goal is to optimize memory capacity and bandwidth efficiently. The a

0 views • 34 slides

Locality-Aware Caching Policies for Hybrid Memories

Different memory technologies present unique strengths, and a hybrid memory system combining DRAM and PCM aims to leverage the best of both worlds. This research explores the challenge of data placement between these diverse memory devices, highlighting the use of row buffer locality as a key criter

0 views • 34 slides

Understanding the Impact of On-Die ECC on DRAM Error Characteristics

The BEER project explores how on-die ECC complicates DRAM reliability studies by concealing error characteristics. It aims to uncover the unique ECC function of DRAM chips and infer error locations in error-prone cells. The study highlights the challenges in identifying and correcting bit flips obfu

0 views • 17 slides