Network Function Abstraction A delicate question of (CPU) affinity?

Exploring the delicate balance of CPU affinity in network function abstraction, including challenges, benefits, and solutions like CPU pinning for network workloads. Learn about the impact on performance and scalability, as well as the importance of proper configuration in virtual and physical envir

3 views • 40 slides

Comprehensive Guide to 8085 Microprocessor Interrupts and Pin Diagram

Explore the PIN diagram of the 8085 microprocessor, understand interrupts, including hardware interrupts like TRAP, RST, INTR, and the classification of interrupts such as maskable, non-maskable, vectored, and more. Learn about the sequence of steps during interrupts and their significance in microp

12 views • 31 slides

Understanding Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

Understanding Interrupts in Embedded Systems

In embedded systems, interrupts play a crucial role in letting peripherals notify the CPU of state changes. They are events external to the current process that disrupt the normal flow of instruction execution, typically generated by hardware devices. By using interrupts, CPUs can efficiently handle

1 views • 12 slides

Understanding Processor Interrupts and Exception Handling in Zynq Systems

Learn about interrupts, exceptions, and their handling in Zynq Systems. Explore concepts like interrupt sources, Cortex-A9 processor interrupts, interrupt terminology, and the difference between pooling and hardware interrupts. Gain insights into interrupt service routines, interrupt pins, interrupt

0 views • 60 slides

Understanding Timers and Interrupts in Operating Systems

This content discusses the importance of timers and interrupts in operating systems, focusing on how they facilitate preemptive multitasking. It covers how hardware timer interrupts help in preemption of processes by the kernel, ensuring efficient task scheduling and resource management in modern op

4 views • 18 slides

Understanding CPU Scheduling in Operating Systems

In a single-processor system, processes take turns running on the CPU. The goal of multiprogramming is to keep the CPU busy at all times. CPU scheduling relies on the alternating CPU and I/O burst cycles of processes. The CPU scheduler selects processes from the ready queue to execute when the CPU i

1 views • 26 slides

Understanding Interrupts in Computer Systems

Interrupts in computer systems play a crucial role in handling various events and managing the flow of instructions. This content discusses the types of interrupts, causes, handling procedures, and the role of supervisory modes in modern computers. It covers topics such as internal and external inte

0 views • 29 slides

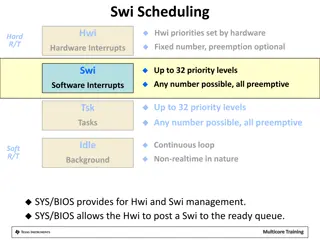

Real-Time Interrupt Handling and Scheduling in SYS/BIOS

This content covers the management of hardware and software interrupts, interrupt priorities, scheduling rules, and execution flow for real-time systems using SYS/BIOS. It discusses the handling of interrupts by the Hardware Interrupt (Hwi) and Software Interrupt (Swi) components, priority levels, p

0 views • 4 slides

Understanding Interrupt Processing in Operating Systems

An interrupt in an operating system disrupts the normal sequence of instructions executed by the processor. When an interrupt occurs, the OS takes control, saves the state of the interrupted process, analyzes the interrupt, and passes control to the appropriate routine. There are six classes of inte

0 views • 15 slides

Understanding MIPS I/O and Interrupt Handling

Delve into the world of MIPS architecture, exploring how I/O operations and interrupts are managed. Learn about memory organization, system functions, I/O registers, and kernel data. Discover how SPIM facilitates input and output handling, including reading from the keyboard and managing output. Div

0 views • 18 slides

Understanding Computer Organization: Instruction Set Architecture and Interrupts

Explore the critical concepts of Computer Organization focusing on Instruction Set Architecture (ISA) and Interrupts. ISA serves as the interface between hardware and software, enabling programmers to write machine language programs effectively. Learn about Application Binary Interface (ABI), interr

0 views • 26 slides

Understanding Interrupts in PIC16F Microcontrollers

Explore the key sources of interrupts in PIC16F627A/628A/648A, accessing registers, enabling interrupts, and managing local interrupts such as Timer 0 alarms and B0 pin changes. Learn how to set interrupts on desired events and understand the corresponding flag bits for interrupt occurrence.

0 views • 17 slides

Understanding Interrupts and Timers in Microcontrollers

Microprocessors function as finite state machines, with instructions loaded from memory and executed in sequence. However, interrupts allow for urgent out-of-turn servicing of signals, providing a way to handle asynchronous events. Learn how to utilize interrupts efficiently with examples on Arduino

0 views • 9 slides

Understanding Interrupt Processing Sequence in X86 Processors

X86 processors have 256 software interrupts, functioning similarly to a CALL instruction. When an INT n instruction is executed, the processor follows a sequence involving pushing the flag register, clearing flags, finding the correct ISR address, and transferring CPU control. Special interrupts lik

0 views • 10 slides

Understanding Operating System Interrupts and System Calls

Explore the fundamentals of operating system interrupts and system calls in COMP.530. Learn about synchronous and asynchronous interrupts, control flow handling, and the hardware tools available for irregular control flow. Delve into the key building blocks of operating systems such as context switc

0 views • 30 slides

Understanding Interrupts in 8051 Microcontroller

Interrupts in 8051 microcontrollers allow the system to respond to asynchronous events while multitasking on a single CPU, giving the illusion of handling many things simultaneously. They introduce the concept of priority, enabling preference over simultaneous interrupts. The interrupt vectors deter

0 views • 13 slides

Understanding Fundamental Concepts of Interrupts in Embedded Systems

Explore the fundamental concepts of interrupts in embedded systems, including interrupt handling, maskability, priority, service routines, and interrupt vectors. Learn how interrupts allow the CPU to handle special events efficiently, coordinate I/O activities, and prevent CPU tie-up, enhancing syst

0 views • 57 slides

Understanding Microcontroller Interrupts and Applications

Explore the fundamental concepts of interrupts, PWM, timer/counters, and ADC in microcontrollers. Learn how to use interrupts for tasks like LED blinking, control LED brightness with PWM, and read voltage using ADC. Get insights on interrupt routines, enabling interrupts through registers, and tips

0 views • 32 slides

Understanding Interrupt Handling with LPC2148 in Electronics & Telecommunication

Introduction to interrupt handling with LPC2148 focusing on ARM processors, IRQ, FIQ, associated registers, interrupt enabling, types of interrupts (FIQ, Vectored IRQ, Non-Vectored IRQ), and differences between Vectored and Non-Vectored interrupts in the context of LPC2148. Discusses interrupt sourc

0 views • 15 slides

Understanding Interrupt Handling in MSP430 Embedded Systems

This lab explores the intricacies of handling interrupts in MSP430, covering types of interrupts, enabling interrupts, and the execution flow when an interrupt is requested and serviced. Topics include interrupt service routines, clearing interrupt flags, and enabling/disabling maskable interrupts.

0 views • 23 slides

Understanding Interrupts and MicroBlaze in Advanced Embedded Systems

Dive into the world of interrupts in embedded systems with a focus on MicroBlaze architecture. Learn how interrupts enable multitasking, the process of handling interrupts, and generating interrupts in MicroBlaze. Explore custom IP integration and gain insights into interrupt-driven programming. Dis

0 views • 32 slides

Understanding Timers and Scheduled Interrupts in Physics 124

The lecture covers timer basics for Arduino Uno/Nano, discussing available timers, prescaler options, PWM frequencies, and implementation details. It explains prescaling and frequency concepts, wrap times for Timer0, Timer1, and Timer2, and the importance of timed interrupts for creating a schedule

0 views • 21 slides

Understanding Computer Architecture Interrupts and Exceptions

Computer architecture interrupts and exceptions are essential for handling external events and unexpected conditions during program execution. Interrupts are caused by external events such as I/O requests, timers, or hardware failures, while exceptions occur due to specific instruction executions. W

0 views • 19 slides

Understanding Arduino Timer and External Interrupts

Interrupts play a crucial role in Arduino programming, allowing for immediate responses to external events. This content covers the concepts of timer interrupts and external interrupts, their applications, and how to use them effectively in Arduino projects. It explains how interrupts work, provides

0 views • 11 slides

Understanding Interrupts in Embedded Systems using MicroBlaze

Dive into the world of interrupts in embedded systems with a focus on using the MicroBlaze soft core processor and custom IP to handle interrupts efficiently. Learn about the significance of interrupt service routines, interrupt handling process, and how to generate interrupts in MicroBlaze for seam

0 views • 30 slides

Understanding Exceptional Control Flow in Computer Systems

Control flow mechanisms in computer systems have evolved to handle exceptional events triggered by external system states. This includes exceptions, interrupts, and context switches that enable the CPU to respond to events like data arrival, user inputs, and system timeouts. Exception handling invol

0 views • 66 slides

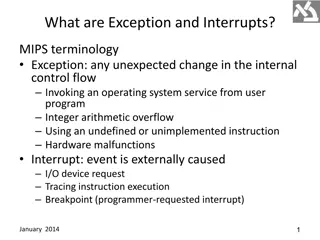

Exception Handling and Interrupts in MIPS Architectures

Exception and interrupts in MIPS play a crucial role in handling unexpected events and external requests efficiently. Exceptions include changes in control flow, arithmetic overflows, and hardware malfunctions, while interrupts are externally caused events like I/O requests. When an exception occurs

1 views • 29 slides

Understanding CPU Structure and Function in Computer Organization and Architecture

Exploring the intricate details of CPU architecture, this content delves into the essential tasks of fetching, interpreting, processing, and writing data. It discusses the significance of registers, user-visible registers, general-purpose registers, and condition code registers in CPU operations. Ad

0 views • 83 slides

Understanding CPU Architecture in Computing for GCSE Students

Explore the fundamental concepts of CPU architecture, including the Von Neumann Architecture, common CPU components like ALU and CU, and how characteristics such as Clock Speed and Cache Size impact performance. Learn about the Fetch-Execute Cycle and the essential hardware components of a computer

0 views • 18 slides

Intel CPU Architectures Overview: Evolution and Features

Explore the evolution and key features of various Intel CPU architectures including Pentium, Core, and Pentium 4 series. Learn about the pipeline stages, instruction issue capabilities, branch prediction mechanisms, cache designs, and memory speculation techniques employed in these processors. Gain

0 views • 11 slides

Understanding the Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

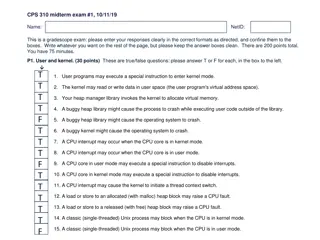

Understanding User and Kernel Modes in Operating Systems

The content provided discusses various aspects of user and kernel modes in operating systems through a set of true/false questions related to user programs, CPU interrupts, heap management, and process behavior in different modes. It touches on the role of the kernel in managing virtual memory, hand

0 views • 10 slides

Understanding Operating System Concepts: Multiprogramming, Multiprocessing, Multitasking, and Multithreading

In the realm of operating systems, terms like multiprogramming, multiprocessing, multitasking, and multithreading can often be confusing due to their similar appearance but distinct meanings. These concepts play a crucial role in efficiently managing resources in a computing system, particularly in

0 views • 6 slides

Understanding CPU Scheduling Concepts at Eshan College of Engineering, Mathura

Dive into the world of CPU scheduling at Eshan College of Engineering in Mathura with Associate Professor Vyom Kulshreshtha. Explore topics such as CPU utilization, I/O burst cycles, CPU burst distribution, and more. Learn about the CPU scheduler, dispatcher module, scheduling criteria, and the impl

0 views • 18 slides

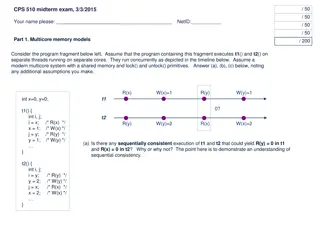

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Understanding Barrel Shifter in CPU Design

Barrel shifter is a vital component in CPU architecture, enabling shifting and rotating operations on data inputs based on control signals. The shifter consists of two main blocks - Shift-and-Rotate Array (SARA) and Control Logic. SARA, designed with multiple stages of cells, executes shift and rota

0 views • 12 slides

Understanding CPU Virtualization and Execution Control in Operating Systems

Explore the concepts of CPU virtualization, direct execution, and control mechanisms in operating systems illustrated through a series of descriptive images. Learn about efficient CPU virtualization techniques, managing restricted operations, system calls, and a limited direct execution protocol for

0 views • 18 slides

Enhancing gem5's GPUFS Support for Improved Simulation Speed

Addressing challenges in application scaling, this project focuses on enhancing gem5's GPUFS support to improve simulation speed by functionally simulating memory copies and adding KVM CPU-GPU support. The introduction covers prior CPU-GPU support in gem5, ML support, and the introduction of GPUFS s

0 views • 19 slides

Illustrated Design of a Simplified CPU with 16-bit RAM

Demonstrates the design of a basic CPU with 11 instructions and 4096 16-bit RAM, showcasing the assembly of a general-purpose computer using gates and registers. The CPU comprises 8 key registers for various functions, employing a sequential circuit for instruction execution. The machine language pr

0 views • 31 slides