Network Function Abstraction A delicate question of (CPU) affinity?

Exploring the delicate balance of CPU affinity in network function abstraction, including challenges, benefits, and solutions like CPU pinning for network workloads. Learn about the impact on performance and scalability, as well as the importance of proper configuration in virtual and physical envir

3 views • 40 slides

Understanding the Basics of Computer Hardware and CPU

Explore the fundamental concepts of information technology, focusing on hardware components like the CPU, control unit, ALU, registers, and cache memory. Learn about the functions of these parts and how they contribute to a computer's performance and speed.

3 views • 37 slides

Understanding Computer Architecture in CSE502

Exploring the intricate details of computer architecture in CSE502, covering concepts such as instruction commit, pipeline stages, program execution order, CPU state management during context switches, and implementation in the CPU. The focus is on the sequential part and the unified register file,

1 views • 26 slides

Understanding Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

MIPS CPU Design Using Verilog and Instruction Set Architecture Overview

Explore the world of MIPS CPU design using Verilog with a deep dive into Instruction Set Architecture (ISA), SPIM instruction formats, addressing modes, and more. Learn about the key components such as Program Counter (PC), Instruction Memory (IM), Register Files (RF), Arithmetic Logic Unit (ALU), D

1 views • 29 slides

Understanding Interrupts in Embedded Systems

In embedded systems, interrupts play a crucial role in letting peripherals notify the CPU of state changes. They are events external to the current process that disrupt the normal flow of instruction execution, typically generated by hardware devices. By using interrupts, CPUs can efficiently handle

1 views • 12 slides

Understanding von Neumann Architecture in Parallel & Distributed Systems

Exploring the von Neumann architecture, this lecture delves into the components like main memory, CPU, registers, and data transfer. It discusses the bottleneck problem and modifications made to enhance CPU performance, such as caching methods. The web presentation offers insights into key aspects o

0 views • 23 slides

Understanding Cache Memory in Computer Architecture

Cache memory is a crucial component in computer architecture that aims to accelerate memory accesses by storing frequently used data closer to the CPU. This faster access is achieved through SRAM-based cache, which offers much shorter cycle times compared to DRAM. Various cache mapping schemes are e

2 views • 20 slides

Anatomy of a Computer System: Hardware Components and Functions

A typical computer system consists of hardware and software working together to perform various computational tasks. The hardware components include the central processing unit (CPU), input/output devices, storage units, and the motherboard. The CPU acts as the main brain of the computer, performing

6 views • 6 slides

Understanding Computer Processing Systems

Computer processing systems consist of various components such as the control unit, ALU, input unit, CPU, output unit, memory, and more. Input devices feed raw data to the computer, while output devices provide processed information. The CPU plays a crucial role in executing instructions and data pr

0 views • 13 slides

Hardware-Assisted Virtualization: VT-x Overview and Implementation

Explore the key concepts of hardware-assisted virtualization using Intel VT-x technology for CPU virtualization, VMX transitions, and VM control structures. Understand the motivation behind VT-x, CPU virtualization techniques, and the benefits of VT-x in simplifying VMM software. Dive into VMX opera

2 views • 28 slides

Understanding Scheduling Algorithms in Operating Systems

Exploring the world of scheduling in operating systems, this content covers various aspects such as introduction to scheduling, process behavior, bursts of CPU usage, CPU-bound and I/O-bound processes, when to schedule processes, and the differences between non-preemptive and preemptive scheduling a

0 views • 34 slides

Understanding CPU Scheduling in Operating Systems

In a single-processor system, processes take turns running on the CPU. The goal of multiprogramming is to keep the CPU busy at all times. CPU scheduling relies on the alternating CPU and I/O burst cycles of processes. The CPU scheduler selects processes from the ready queue to execute when the CPU i

1 views • 26 slides

Accelerator for VMware Backup Solutions

Today's challenges in backing up data from VMware environments include high data volume, small backup windows, slow traditional backups, network bandwidth utilization, and CPU overhead. NetBackup's Accelerator for VMware in version 7.6 addresses these challenges by using Changed Block Tracking (CBT)

0 views • 18 slides

Overcoming Memory Constraints in Deep Neural Network Design

Limited availability of high bandwidth on-device memory presents a challenge in exploring new architectures for deep neural networks. Memory constraints have been identified as a bottleneck in state-of-the-art models. Various strategies such as Tensor Rematerialization, Bottleneck Activations, and G

0 views • 32 slides

Understanding Basics of Computer Systems

A computer is an electronic device that stores and processes data using hardware and software components. It consists of a CPU, memory, storage devices, input/output devices, and communication devices. The CPU includes a Control Unit and Arithmetic Logic Unit, and the memory stores data in bytes. St

0 views • 57 slides

Understanding Weird Machines in Transient Execution

Weird machines refer to models exhibiting unintentional behaviors triggered by adversarial inputs. They serve as computation primitives, enabling tasks like program obfuscation and secret computations. TSX weird machines, computing with time, manipulate cache states through gates like Assign, AND, O

0 views • 18 slides

Understanding System on Chip (SoC) Design and Components

Explore the world of System on Chip (SoC) design, components, and working flow. Learn about Intellectual Properties (IP), platform-based design, typical design flows, top-down design approach, and the emerging Electronic System Level (ESL) design flow. Discover the essential components of an SoC, su

0 views • 45 slides

Core-Assisted Bottleneck Acceleration in GPUs: Maximizing Resource Utilization

Imbalances in GPU execution lead to underutilization of resources, prompting the need for a solution like CABA (Core-Assisted Bottleneck Acceleration). This framework enables the efficient use of helper threads in GPUs, addressing memory bandwidth bottlenecks through flexible data compression. By le

0 views • 37 slides

Deep Learning with Theano: Installation, Neurons, and Exploration

Delve into the world of deep learning with Peter Podolski's comprehensive guide on utilizing Theano for neural network development. Explore topics such as installation on various systems, working with neurons, and unlocking the potential for CPU and GPU optimization. Discover insights on hidden node

0 views • 20 slides

Distributions of Computer Science in the 1990s

The study of distributions in Computer Science began in the 1990s with a focus on CPU load balancing and job migration. Concepts like preemptive migration and non-preemptive migration were explored to balance job allocations on machines. These studies laid the foundation for understanding the distri

0 views • 31 slides

Understanding Fundamental Concepts of Interrupts in Embedded Systems

Explore the fundamental concepts of interrupts in embedded systems, including interrupt handling, maskability, priority, service routines, and interrupt vectors. Learn how interrupts allow the CPU to handle special events efficiently, coordinate I/O activities, and prevent CPU tie-up, enhancing syst

0 views • 57 slides

Embedded Systems: Introduction to Input and Output Devices

This material explores the essential concepts related to input and output (I/O) devices in embedded systems. It covers examples of I/O devices, such as keyboards, mice, and disk drives, along with the digital interface between these devices and the CPU. Specific focus is given to the 8251 UART as an

0 views • 55 slides

Comprehensive Guide to Virtualization Infrastructure Administration

Explore the world of virtualization infrastructure administration, covering resources such as CPU, memory, storage, and network I/O. Learn about resource management, CPU scheduling, memory efficiency, and virtual memory management in virtualized environments. Dive into topics like vCPU mapping, prop

0 views • 10 slides

Energy-Efficient Query Processing on Embedded CPU-GPU Architectures

This study explores the energy efficiency of query processing on embedded CPU-GPU architectures, focusing on the utilization of embedded GPUs and the potential for co-processing with CPUs. The research evaluates the performance and power consumption of different processing approaches, considering th

0 views • 22 slides

Improvements and Performance Analysis of GATE Simulation on HPC Cluster

This report covers the status of GATE-related projects presented in May 2017 by Liliana Caldeira, Mirjam Lenz, and U. we Pietrzyk at the Helmholtz-Gemeinschaft. It focuses on running GATE on a high-performance computing (HPC) cluster, particularly on the JURECA supercomputer at the Juelich Supercomp

0 views • 8 slides

Understanding Process Management in Computer Systems

Exploring the concepts of process management in computer systems, including process creation, termination, running programs, synchronization between processes, and the components involved in managing processes such as memory, CPU, files, and devices. The importance of processes in sharing system res

0 views • 22 slides

Exploring Kubernetes Load Balancing with P4 Intel IPU Team

This presentation delves into Kubernetes load balancing and network functions using P4 Intel IPU technology. It covers service load balancing, control plane overview, P4 program logical view, demo initial setup, evaluation conclusions, and acknowledgements. The team aims to reduce CPU utilization, i

0 views • 8 slides

Understanding CPU Structure and Function in Computer Organization and Architecture

Exploring the intricate details of CPU architecture, this content delves into the essential tasks of fetching, interpreting, processing, and writing data. It discusses the significance of registers, user-visible registers, general-purpose registers, and condition code registers in CPU operations. Ad

0 views • 83 slides

Understanding CPU Architecture in Computing for GCSE Students

Explore the fundamental concepts of CPU architecture, including the Von Neumann Architecture, common CPU components like ALU and CU, and how characteristics such as Clock Speed and Cache Size impact performance. Learn about the Fetch-Execute Cycle and the essential hardware components of a computer

0 views • 18 slides

Intel CPU Architectures Overview: Evolution and Features

Explore the evolution and key features of various Intel CPU architectures including Pentium, Core, and Pentium 4 series. Learn about the pipeline stages, instruction issue capabilities, branch prediction mechanisms, cache designs, and memory speculation techniques employed in these processors. Gain

0 views • 11 slides

Understanding the Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

Understanding Processor Generations and VM Sizing for Azure Migration

Exploring the impact of processor generations on CPU performance, factors like clock speed, instruction set, and cache size are crucial. Choosing the right-sized VM plays a vital role in optimizing Azure migration. Passmark CPU Benchmark results provide insights on Intel processor generations for Az

0 views • 9 slides

Understanding Operating System Concepts: Multiprogramming, Multiprocessing, Multitasking, and Multithreading

In the realm of operating systems, terms like multiprogramming, multiprocessing, multitasking, and multithreading can often be confusing due to their similar appearance but distinct meanings. These concepts play a crucial role in efficiently managing resources in a computing system, particularly in

0 views • 6 slides

Understanding CPU Scheduling Concepts at Eshan College of Engineering, Mathura

Dive into the world of CPU scheduling at Eshan College of Engineering in Mathura with Associate Professor Vyom Kulshreshtha. Explore topics such as CPU utilization, I/O burst cycles, CPU burst distribution, and more. Learn about the CPU scheduler, dispatcher module, scheduling criteria, and the impl

0 views • 18 slides

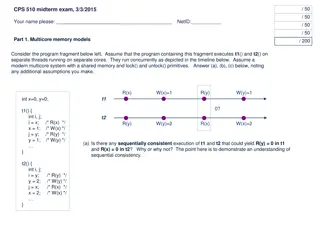

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Understanding Barrel Shifter in CPU Design

Barrel shifter is a vital component in CPU architecture, enabling shifting and rotating operations on data inputs based on control signals. The shifter consists of two main blocks - Shift-and-Rotate Array (SARA) and Control Logic. SARA, designed with multiple stages of cells, executes shift and rota

0 views • 12 slides

Understanding CPU Virtualization and Execution Control in Operating Systems

Explore the concepts of CPU virtualization, direct execution, and control mechanisms in operating systems illustrated through a series of descriptive images. Learn about efficient CPU virtualization techniques, managing restricted operations, system calls, and a limited direct execution protocol for

0 views • 18 slides

Enhancing gem5's GPUFS Support for Improved Simulation Speed

Addressing challenges in application scaling, this project focuses on enhancing gem5's GPUFS support to improve simulation speed by functionally simulating memory copies and adding KVM CPU-GPU support. The introduction covers prior CPU-GPU support in gem5, ML support, and the introduction of GPUFS s

0 views • 19 slides

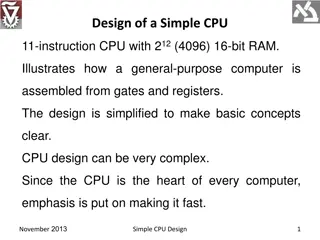

Illustrated Design of a Simplified CPU with 16-bit RAM

Demonstrates the design of a basic CPU with 11 instructions and 4096 16-bit RAM, showcasing the assembly of a general-purpose computer using gates and registers. The CPU comprises 8 key registers for various functions, employing a sequential circuit for instruction execution. The machine language pr

0 views • 31 slides