Solving PWM Trip Occurrence with CLB Constraint

In a scenario where PWM tripping occurs, a proposed solution utilizing CLB constraints ensures a consistent 50% duty cycle even during trips. The theoretical solutions provide detailed sequences for maintaining PWM signals and outputs, effectively managing trip occurrences. Explore theoretical scenarios with CLB constraints for handling PWM trip interruptions seamlessly.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

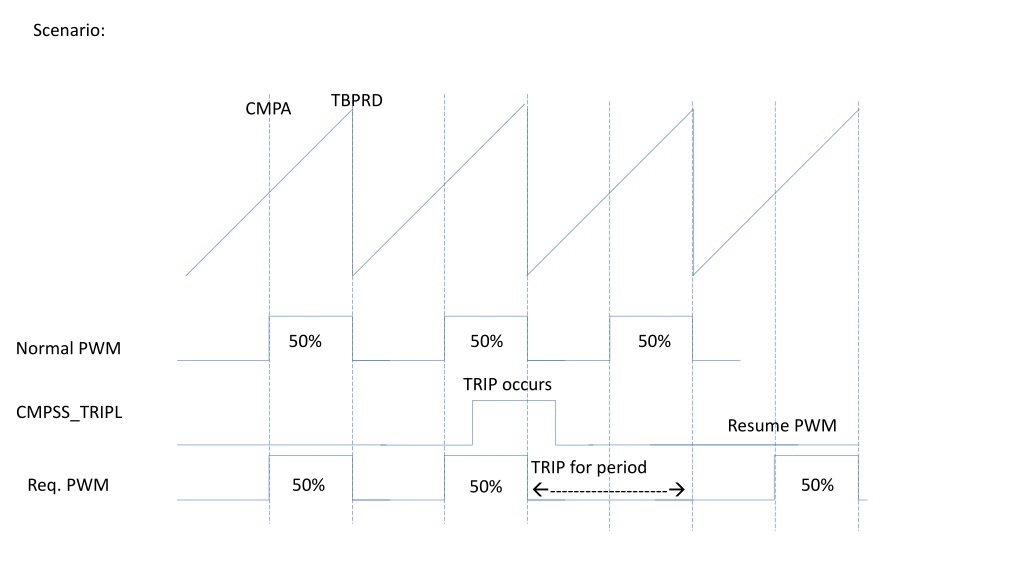

Scenario: TBPRD CMPA 50% 50% 50% Normal PWM TRIP occurs CMPSS_TRIPL Resume PWM TRIP for period -------------------- Req. PWM 50% 50% 50%

Proposed Solution using CLB Constraint: Having a 50% Duty cycle at all times even if trip occurs S0: Keep original PWM signals S1: Keep original PWM signals S2: Set outputs to certain state S3: Keep outputs to certain state S0 CMPSS trip Occurs TBCTR == Period and no trip S3 S1 TBCTR == Period On falling edge of PWM signal If trip occurs again during period and CTR has not reached period S2

Theoretical solution scenario 1: TBPRD CMPA S0 50% 50% 50% Normal PWM TRIP occurs S0 CMPSS_TRIPL S1 Resume PWM TRIP for period -------------------- Req. PWM 50% 50% 50% S2

Theoretical solution scenario 2: TBPRD CMPA S0 50% 50% 50% Normal PWM S0 TRIP occurs CMPSS_TRIPL S1 Set outputs PWM Resume PWM TRIP for period -------------------- S2 Req. PWM 50% 50% S 2 S3