SOI wafers: summary of relevant aspects

The summary covers fixed parameters for SOI wafers, comparison between SiSi and SOI for 3D processes, considerations for managing different process variants, and decision-making factors related to time and complexity.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

INFNLogo Mar. 2, 2015 G.-F. Dalla Betta SOI wafers: summary of relevant aspects Gian-Franco Dalla Betta University of Trento and TIFPA INFN, Trento, Italy gianfranco.dallabetta@unitn.it

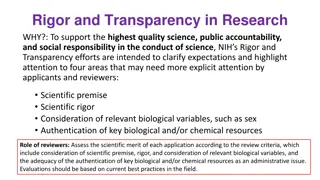

INFNLogo Mar. 2, 2015 G.-F. Dalla Betta Fixed parameters After interactions with ICEMOS, the following aspects can be considered as fixed: - same starting substrates as SiSi wafers, both in terms of thickness(es) and of doping concentrations - possibly use standard SOI ICEMOS process - provide it ensures 200 nm oxide layer - external service for back-side Boron implant - external service for B implant profile measurement

INFNLogo Mar. 2, 2015 G.-F. Dalla Betta SiSi vs SOI for 3D SOI SiSi P- high cm wafer P- high cm wafer SiO2 p++ low cm wafer p-spray p++ low cm wafer To be thinned down To be thinned down Similar process except for the etching of the ohmic columns - FBK demonstrated the feasibility - But is it possible to manage both variants as a process split ? - If YES, what would be the best process strategy/schedule ? On the back-side of the FZ wafer, 3D-SOI requires a p-spray layer to reduce the electric field at the interface

INFNLogo Mar. 2, 2015 G.-F. Dalla Betta SiSi vs SOI for PAE SOI SiSi P- high cm wafer P- high cm wafer SiO2 p++ low cm wafer p+ p++ low cm wafer To be thinned down To be thinned down Similar process except for the etching of the trenches - Is it possible to manage both variants as a process split ? - If YES, what would be the best process strategy/schedule ? On the back-side of the FZ wafer, PAE-SOI requires a p+ layer for ohmic contact (optimal bias voltage distribution)

INFNLogo Mar. 2, 2015 G.-F. Dalla Betta Relevant aspects for decision Time - SOI wafers will likely require at least 2 months for delivery - Can 3D batch wait so long ? - Can it start with SiSi and later add SOI ? Complexity - Is it wise to mix the two 3D process options ? - Is it better to try SOI first with PAE ?