Modeling CDAC SAR Input: A Case Study of ADS8320

This case study delves into modeling the SAR input of ADS8320, exploring the number of time constants vs. ADC resolution, voltage-controlled switches in SPICE, and the correct parameters for modeling SAR ADC. It also covers the specifications of ADS8320, including analog input characteristics, sampling dynamics, clock frequency, resolution, and more.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Modeling CDAC SAR Input A case study of ADS8320 Tim Green, MGTS Precision Linear Analog Applications April 16, 2015 1

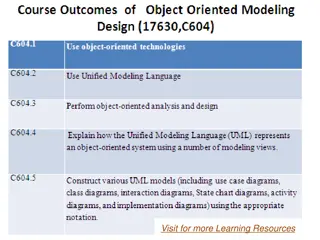

Number of Time Constants vs ADC Number of Bits to Settle <1/2 LSB (Based on Full Scale Input) Number of Bits 10 12 14 16 18 20 22 24 1/2 LSB 0.0488281% 0.0122070% 0.0030518% 0.0007629% 0.0001907% 0.0000477% 0.0000119% 0.0000030% Time Constants 8 9 11 12 13 15 17 18 3

Wrong (TINA Default) Switch Parameters for Modeling SAR ADC tsmpl SW_smpl 0 Von 1 + + - R1 1k R2 1k V1 5 VF1 6

Wrong (TINA Defualt) Switch Parameters for Modeling SAR ADC 7

Right Switch Parameters for Modeling SAR ADC tsmpl SW_smpl 0 Von 1 + + - R1 1k R2 1k V1 5 VF1 8

ADS8320 Specifications Analog Input: Csh=45pF Rsw = 100 ohms (not in data sheet and not critical as long as 1/(Rsw*Csh ) << tsmpl Assume Csh is reset to zero at end of each conversion cycle Full-scale Input Span = 0V to Vref Sampling Dynamics: Conversion Time (tconv) = 16 Clk cycles Acquisition Time (tacq) = 4.5 Clk cycles Clock Frequency (fclk) = 24kHz to 2.4MHz For fclk=2.4MHz (maximum sampling rate): tconv = 6.67us tacq = 1.88us Vref: 5V Resolution : 16 Bit ADC Vref = LSB 1 2 # Bits 5 V 1 = = = LSB 1 76 3 . V LSB 38 . 15 V 2 2 16 11

ADS8320 Input Model V+ Verror Voa_SS 2.501 -1.2505V ADS8320 Input Model Verror = Vcsh - Voa Voa Steady State Voltage Vacq Vconv + + - - SW_conv 0 Von 1 ADC_in - R1 100 Rsw 100 ++ SW_acq 0 Von 1 Voa 2.501V Op Amp VCVS1 1 Csh 45p + + + V1 5 Vin 2.5 V V_Csh 1.2505V Vcsh 1.2505V - - Vacq Vconv Vref = 2.5V tacq = 1.88us tconv=6.67us Vin = +/-2.5V LSB = 5V / 2^12 = 1.22mV 1/2_LSB = 610uV + + tacq tconv 1) Voa_SS will be used to easily measure Verror (difference between op amp output, Voa, and V_Csh at the end of tacq) in transient analysis. Do a DC Analysis and measure Voa. Adjust Voa_SS = Voa @ DC. Ignore Verror in DC Analysis since SW_Acq and SW_conv each have off resistance of 1T-ohm and form a DC divider which we will not care about. 2) 3) 12

ADS8320 Input Model Timing Voltage Sources, tacq & tconv ADS8320 Typical ADC Timing tsmpl 1.8us tconv 6.67us 1) Set trise and tfall times at 1ns for reasonable real world timing and ease of SPICE convergence in transient analysis. 2) tconv need only discharge Csh before the next tacq. So we will switch on SW_conv for a10ns pulse with the end of this pulse 10ns away from end of tconv to avoid SW_conv and SW_acq from ever being on at the same time. ADS8320 Typical ADC Switch Control 8.471us 1.801us 1.8us 1ns 0s 1V tacq 0V 8.449us 8.461us 8.45us 8.46us 0s 8.471us 1V tconv 0V 13

Creating tacq & tconv with PWL (PieceWise Linear) Voltage Sources Piecewise Linear Waveform Builder tacq control REPEAT FOREVER tconv control REPEAT FOREVER 0.000E+00 1.000E-09 1.800E-06 1.801E-06 8.471E-06 0.000E+00 1.000E+00 1.000E+00 0.000E+00 0.000E+00 0 0 8.449E-06 0.000E+00 8.450E-06 1.000E+00 8.460E-06 1.000E+00 8.461E-06 0.000E+00 8.47E-06 0.000E+00 ENDREPEAT ENDREPEAT 14

tacq PWL Voltage Source Paste from Excel PWL EZ Build SAR Timing worksheet. 15

tacq PWL Voltage Source Paste from Excel PWL EZ Build SAR Timing worksheet. 16

ADS8320 Input Model Complete 2.56 T V_Csh 0.00 2.56 Vcsh 0.00 54.25m Verror -2.50 2.55 Voa 1.83 1.00 tacq 0.00 1.00 tconv 0.00 0.00 20.00u 40.00u Time (s) 17

ADS8320 Input Model Complete Zoom In 1) 2) Note tconv pulse at the end of tconv before rise of tacq. At end of tacq = 1, Verror = 152nV and (1/2 LSB = 38.15uV). This ideal op amp and 100 ohms into ADC_in would work. 18

Improper ADC Input Drive At end of tacq Verror is -3.1mV or 4.23 LSBs At end of tacq Voa is not fully settled. Real parts will vary on Aol and settle. Not a robust design. 20

Proper ADC Input Drive: Response with optimized Op Amp, R-C At end of tacq Voa is fully settled. Verror < 1/2LSB at end of tacq 21

Op Amp Stability Reference For detailed, definition-by-example of 10 different ways to stabilize op amps driving capacitive loads, and additional technical information on solving op amp stability problems, visit the Texas Instruments E2E Forum at: http://e2e.ti.com/support/amplifiers/precision_amplifiers/w/design_notes/ 2645.solving-op-amp-stability-issues.aspx Download Part 1, Part 2, Part 3, and Part 4. All Embedded Schematics in this presentation can be run in the Free TINA_TI SPICE simulator available at: http://www.ti.com/tool/tina-ti 22