Advanced Simulation Integration in Virtuoso Design Environment

Explore the seamless integration of simulation flows in the Virtuoso ADE L/XL design environment, showcased at AMICSA 2018 in Leuven. From DARE set simulations to Wish List features and historical advancements like SET Striker Verilog-A models, the presentation highlights the compatibility with ADE Explorer/Assembler and the versatile applications in circuit analysis and exploration.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

DARE SET SIMULATION FLOW INTEGRATED IN VIRTUOSO ADE L/XL DESIGN ENVIRONMENT STAF VERHAEGEN AMICSA 2018, LEUVEN PUBLIC

DARE SET SIMULATION FLOW INTEGRATED IN VIRTUOSO ADE L/XL DESIGN ENVIRONMENT STAF VERHAEGEN AMICSA 2018, LEUVEN Also compatible with ADE Explorer/Assembler PUBLIC

OVERVIEW SET Wish List History Wrap-Up AMICSA 2018 3

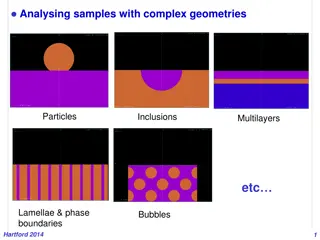

SET SINGLEEVENTTRANSIENT Courtesy: ECSS-Q-HB-60-02A1 Radiation Handbook AMICSA 2018 5

WISH LIST Easy SET injection on nodes in a circuit Integrated in analog design flow No changes needed on circuit to investigate Flexible timing of generated events Fit in design exploration, SET screening phase Fit in circuit SET hardening phase AMICSA 2018 7

HISTORY OCEAN SCRIPT SET injection in all nodes AMICSA 2018 9

HISTORY SETSTRIKER VERILOG-A MODEL Not integrated in Virtuoso ADE flow AMICSA 2018 10

HISTORY SETSTRIKER VERILOG-A MODEL AMICSA 2018 11

HISTORY SETSTRIKER VERILOG-A MODEL AMICSA 2018 12

HISTORY DEEPPROBE Adaption of circuit under test needed AMICSA 2018 13

HISTORY DEEPPROBE Part of current DARE180 ADK deepprobe in latest analogLib from Cadence AMICSA 2018 14

HISTORY PERIODIC SETSTRIKERAND DUAL DEEPPROBE Separate instance for each node and each SET event Manual event timing for each event AMICSA 2018 15

probes = '("Probes") probes->list = '( ( /DUT/N1 /GND ) ( /VDD /DUT/N1 ) ( /DUT/N2 /GND ) ( /VDD /DUT/N3 ) ( /DUT/N4 /GND ) ( /VDD /DUT/N4 ) ) HISTORY PERIODIC SETSTRIKERAND DUAL DEEPPROBE Output of internal state for tracing back injected node AMICSA 2018 16

HISTORY COMBINED SETSTRIKERAND DUALPROBE SETstriker and Dualprobe almost always used in combination SETstriker could accidently be connected in reverse AMICSA 2018 17

HISTORY COMBINED SETSTRIKERAND DUALPROBE AMICSA 2018 18

HISTORY TRIGGERED SETSTRIKERAND DUALPROBE Fixed timing; not easily adaptable in through corner simulation AMICSA 2018 19

HISTORY TRIGGERED SETSTRIKERAND DUALPROBE AMICSA 2018 20

HISTORY SET GUI Probelist needs to be edited manually Nodes may be overlooked AMICSA 2018 21

HISTORY COMBINED SETSTRIKERAND DUALPROBE AMICSA 2018 22

WRAP-UP Easy SET injection on nodes in a circuit Integrated in analog design flow No changes needed on circuit to investigate Flexible timing of generated events Fit in design exploration, SET screening phase Fit in circuit SET hardening phase AMICSA 2018 24

WRAP-UP Easy SET injection on nodes in a circuit Integrated in analog design flow In operation at imec for DARE65T development No changes needed on circuit to investigate Flexible timing of generated events Should soon be available for DARE customers Fit in design exploration, SET screening phase Fit in circuit SET hardening phase AMICSA 2018 25