Enhancing TLB Prefetching for Address Translation Performance

This study explores methods to improve TLB prefetching efficiency by leveraging page table locality, presenting two novel approaches - Sampling-based Free TLB Prefetching (SBFP) and Agile TLB Prefetcher (ATP). These techniques focus on optimizing TLB prefetching mechanisms without disrupting the vir

1 views • 10 slides

Insights into University of Bath Admissions Trends and Future Outlook

University of Bath's admissions insights reveal a diverse applicant pool in terms of domicile, demographics, and disciplines. The university receives a high number of applications, with updates for 2023 and 2024 applicants on firm and insurance choices. Teachers and advisors can engage with the univ

2 views • 8 slides

Medical Center Health System.

The Medical Center Health System (MCHS) emphasizes the importance of reporting patient safety events to improve the quality and safety of patient care. All team members are encouraged to report any deviation from routine care, events causing harm or potential harm, near misses, patient complaints, a

0 views • 4 slides

Learning From Error

Understanding the nature of errors in healthcare is crucial for improving patient safety. By learning from errors such as commission, omission, and violations, healthcare professionals can implement strategies to reduce mistakes and enhance overall care quality. Mistakes, near misses, and hindsight

4 views • 19 slides

Efficient Near Miss Reporting via QR Codes

Near miss reporting via QR codes offers a streamlined and efficient method for employees to report potential hazards or incidents. This system involves generating unique QR codes linked to a reporting system, strategically placing them in areas prone to near misses, enabling easy employee interactio

2 views • 8 slides

Reporting Incidents on Sphera

The Council utilizes Sphera to manage health and safety risks, requiring employees to report accidents, near misses, violence incidents, and more promptly. This guide explains how to report incidents on Sphera, including accessing the reporting portal, completing mandatory fields, and obtaining pape

9 views • 26 slides

Introduction to Operating Systems

Explore the concepts of address translation, Translation Lookaside Buffer (TLB), TLB usage in modern processors, TLB invalidate mechanisms, and hardware design principles related to memory hierarchy using examples from the Intel i7 processor. Understanding the trade-offs and costs associated with TL

0 views • 30 slides

National School Sport Week at Home: Engaging Families in Virtual Sporting Challenges

Coundon Primary School is supporting the National School Sport Week at Home campaign to ensure that no child misses out on sports day activities. Taking place from 20 to 26 June, this initiative encourages families, communities, schools, and sports clubs to participate in virtual sporting challenges

5 views • 9 slides

Understanding Incident Reporting in Healthcare

Incident reporting in healthcare is crucial for patient safety and organizational improvement. An incident can encompass a wide range of events that cause or have the potential to cause harm, loss, or damage. Reporting incidents, including near misses, allows for learning from both mistakes and succ

0 views • 10 slides

Nobody Gets Hurt: A New Approach to Safety Classification

Introducing a new Hurt-Based Approach to Safety Classification that focuses on true human impact, potential severity of injuries, and actionable learnings from near misses. Contrasting the Traditional Safety Model, this approach redefines Hurt Levels and emphasizes effective communication to prevent

0 views • 10 slides

Safety Awareness in Trackwork Operations

Explore the importance of safety in trackwork operations through a series of exercises and discussions prompted by film screenings and statistics on near misses. Reflect on key causes, risk tolerance, and the vital role of speaking up to prevent incidents. Enhance awareness and promote a culture of

0 views • 10 slides

Redesigning the GPU Memory Hierarchy for Multi-Application Concurrency

This presentation delves into the innovative reimagining of GPU memory hierarchy to accommodate multiple applications concurrently. It explores the challenges of GPU sharing with address translation, high-latency page walks, and inefficient caching, offering insights into a translation-aware memory

1 views • 15 slides

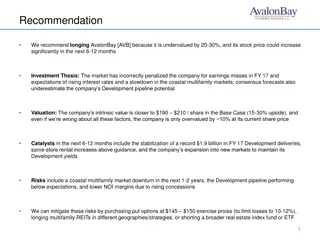

Undervalued Investment Opportunity: AvalonBay (AVB)

Recommended long position in AvalonBay (AVB) due to 20-30% undervaluation and potential stock price increase. Market incorrectly penalized company for past earnings misses and underestimated its development pipeline. Valuation suggests significant upside potential. Mitigate risks with strategic opti

0 views • 9 slides

Workplace Safety Analysis November 2004 Report

The document provides detailed insights into workplace safety and incidents analysis from 2002 to 2004, including accident statistics, injury types, HSSE performance, and causes of incidents. It covers data on fatalities, near misses, recordables, and more. The analysis also delves into personnel hu

0 views • 22 slides

Insights into Virtual Memory Management Challenges

Exploring various aspects of virtual memory management, such as TLB misses, page table optimizations, and the role of hashed page tables, shedding light on the evolution and complexities of memory addressing in computing systems.

0 views • 51 slides

Understanding Near Miss Incidents in Workplace Safety Training

Near misses are unplanned events with the potential for harm that did not result in injury or damage. This training covers the definition of near misses, reporting management, incident types, and reasons for reporting. It emphasizes the importance of addressing system weaknesses to prevent future ac

0 views • 28 slides

Baseball Umpire Training Presentation Highlights 2013

This presentation covers various aspects of baseball umpiring rules and scenarios, focusing on dead ball situations. Created by John Hickey, the slides detail instances where the ball becomes dead immediately, such as when a pitch touches a batter's clothes, or when the batter swings and misses as t

0 views • 60 slides

Understanding Cache Memory Designs: Set vs Fully Associative Cache

Exploring the concepts of cache memory designs through Aaron Tan's NUS Lecture #23. Covering topics such as types of cache misses, block size trade-off, set associative cache, fully associative cache, block replacement policy, and more. Dive into the nuances of cache memory optimization and understa

0 views • 42 slides

Mosaic: A GPU Memory Manager Enhancing Performance Through Adaptive Page Sizes

Mosaic introduces a GPU memory manager supporting multiple page sizes for improved performance. By coalescing small pages into large ones without data movement, it achieves a 55% average performance boost over existing mechanisms. This innovative framework transparently enables the benefits of both

0 views • 52 slides

Understanding Wrongful Convictions: Research, Criteria, and Policy Interventions

The Preventing Wrongful Convictions Project delves into the factors leading to erroneous convictions, exploring research questions, case criteria, organizational assistance, and case selection methodologies. Focusing on factual innocence, the project aims to identify near misses and provide insights

0 views • 18 slides

Improving Near Miss Reporting for Enhanced Workplace Safety

Implementing a comprehensive Near Miss Reporting Tool is crucial for creating a safe work environment. The tool facilitates the reporting of near misses without fear of repercussions, enabling companies to identify weaknesses in safety programs and proactively eliminate hazards. Challenges include t

0 views • 12 slides

Design and Verification of Autonomous System Controllers

Explore the challenges of designing autonomous system controllers under timing uncertainties, focusing on quantitative safety measures to ensure the robot maneuvers safely despite deadline misses. The study delves into implementing controllers, analyzing trajectory deviations under different scenari

0 views • 18 slides

Efficient Handling of Cache Miss Rate in FPGAs

This study focuses on improving cache miss rate efficiency in FPGAs through the implementation of non-blocking caches and efficient Miss Status Holding Registers (MSHRs). By tracking more outstanding misses and utilizing memory-level parallelism, this approach proves to be more cost-effective than s

0 views • 44 slides

Fast TLB Simulation for RISC-V Systems - Research Overview

TLB simulator for RISC-V systems introduced to evaluate TLB designs with realistic workloads, focusing on performance rather than cycle accuracy. The design sacrifices some accuracy for improved performance, making it suitable for meaningful software validation and profiling tasks.

0 views • 29 slides

Understanding Multiprocessors and Memory Hierarchy

Explore topics such as snooping-based coherence, synchronization, consistency, virtual memory overview, address translation, memory hierarchy properties, TLB functionality, TLB and cache access considerations, and cache indexing strategies in multiprocessor systems.

0 views • 22 slides

Efficient Paging Mechanisms in Operating Systems

Today's lecture covers various paging mechanisms in operating systems, including optimizations for managing page tables efficiently, utilizing Translation Lookaside Buffers (TLBs) for faster translations, implementing demand-paged virtual memory, and advanced functionality like memory sharing, copy-

0 views • 35 slides

Trace-Driven Cache Simulation in Advanced Computer Architecture

Trace-driven simulation is a key method for assessing memory hierarchy performance, particularly focusing on hits and misses. Dinero IV is a cache simulator used for memory reference traces without timing simulation capabilities. The tool aids in evaluating cache hit and miss results but does not ha

0 views • 13 slides

Efficient Memory Virtualization: Reducing Dimensionality of Nested Page Walks

TLB misses in virtual machines can lead to high overheads with hardware-virtualized MMU. This paper proposes segmentation techniques to bypass paging and optimize memory virtualization, achieving near-native performance or better. Overheads of virtualizing memory are analyzed, highlighting the impac

0 views • 48 slides

Making Dynamic Page Coalescing Effective on Virtualized Clouds

Creating huge pages through dynamic page coalescing is effective for reducing TLB misses and memory accesses per miss, although it can lead to memory fragmentation and paging overhead. While highly beneficial on native systems, the cost-effectiveness on virtualized platforms is challenged by the inc

0 views • 22 slides

Feedback Analysis on Medication Incident Reporting in Hospitals

Feedback received from IMSN members on NIMS and incident reporting revealed various issues affecting the rates at which staff report medication incidents/near misses within hospitals. Major themes included staffing numbers and turnover, pharmacist involvement in incident reporting, clinical pharmacy

0 views • 12 slides

Practical Transparent Operating System Support for Superpages

Presents a general mechanism for efficient OS management of VM pages of different sizes using superpages without requiring user intervention. Addresses limitations of existing Translation Lookaside Buffers (TLB) in managing page table entries. Discusses TLB organization and realizations in processor

0 views • 47 slides

Enhancing TLB Architecture with CoPTA for Improved Performance

CoPTA introduces a novel TLB architecture with contiguous pattern speculating capabilities to optimize address translation, especially for big-data workloads. By modifying TLB and LSQ to support TLB speculation, performance improvements in memory contiguity and prediction accuracy were achieved. The

0 views • 6 slides

Comprehensive Framework for Virtual Memory Research - Virtuoso

Virtuoso is an open-source, modular simulation framework designed for virtual memory research. The framework aims to address performance overheads caused by virtual memory by proposing solutions like improving the TLB subsystem, employing large pages, leveraging contiguity, rethinking page tables, r

1 views • 29 slides

Understanding Domain Name System (DNS) Resolver Operation and Debugging

The session explores the operation of Domain Name System (DNS) resolvers, focusing on how resolvers work, caching, and querying authoritative nameservers. It delves into the process of resolving queries, locating authoritative nameservers, handling cache misses, and the hierarchical structure of DNS

0 views • 37 slides