Apache MINA: High-performance Network Applications Framework

Apache MINA is a robust framework for building high-performance network applications. With features like non-blocking I/O, event-driven architecture, and enhanced scalability, MINA provides a reliable platform for developing multipurpose infrastructure and networked applications. Its strengths lie i

3 views • 13 slides

Managing File System Consistency in Operating Systems

File systems in operating systems face challenges with crash consistency, especially during write operations. Issues arise when modified data in cache is lost due to system crashes or when data structure invariants are violated. Solutions like write-through and write-back caches help mitigate these

6 views • 14 slides

Understanding Non-Aqueous Solvents: Types and Classification

Inorganic non-aqueous solvents play a crucial role in chemical research and industry. This article by Dr. Princy K.G. delves into the classification of solvents based on protonicity, polarity, and aqueous vs. non-aqueous nature. It explores the types of non-aqueous solvents, such as protonic and non

1 views • 29 slides

Design and Analysis of Engineering Experiments in Practice

Explore the fundamentals of engineering experiments, including blocking and confounding systems for two-level factorials. Learn about replicated and unreplicated designs, the importance of blocking in a replicated design, ANOVA for blocked designs, and considerations for confounding in blocks. Dive

0 views • 15 slides

Understanding Non-Firm Quantities in Electricity Markets

Non-Firm Quantities in electricity markets involve units with non-firm access not being compensated for their non-firm capacity not getting accommodated on the system. The concept of Firm Access Quantity plays a key role in determining compensation levels for units, with differences in implementatio

0 views • 6 slides

Understanding Non-Compete Agreements: Enforceability and Requirements

Non-compete agreements are commonly used in the United States to protect businesses from competition by former employees. To be enforceable, these agreements must meet certain requirements, including independent consideration, protection of legitimate business interests, and reasonableness in scope,

0 views • 26 slides

In-Depth Look at Pentium Processor Features

Explore the advanced features of the Pentium processor, including separate instruction and data caches, dual integer pipelines, superscalar execution, support for multitasking, and more. Learn about its 32-bit architecture, power management capabilities, internal error detection features, and the ef

0 views • 24 slides

Comparison of Trigger-based vs. Non-Trigger-based Sensing Measurement in IEEE 802.11

The document discusses the differences between Trigger-based (TB) and Non-Trigger-based (Non-TB) sensing measurement instances in IEEE 802.11 standards, focusing on who initiates the sensing measurement. TB sensing is initiated by the AP, while Non-TB sensing is initiated by a non-AP STA, enabling o

6 views • 13 slides

Constructive Computer Architecture Realistic Memories and Caches

Explore the realm of constructive computer architecture, realistic memories, and cache systems as presented by the Computer Science & Artificial Intelligence Lab at Massachusetts Institute of Technology. Delve into topics like 2-stage pipeline, magic memory models, and memory system views to gain in

0 views • 20 slides

Mastering Front Line Blocking Techniques in Football

Learn the strategies and techniques involved in front line blocking for field goal and PAT attempts in football. Understand the importance of FG/PAT blocking, inside and outside block schemes, and specific drills for developing these skills. Explore detailed instructions on single, look off, and rev

0 views • 18 slides

ANEFO Meeting on Player Conduct: Rules and Regulations Summary

Eugene Borgonzi presented key rules and regulations regarding player conduct at the ANEFO Meeting on September 30, 2019. The sections covered include rules on assisting runners, illegal use of hands and holding, illegal blocking, and illegal personal contact. The detailed guidelines prohibit actions

1 views • 16 slides

Understanding Parallelism and Vector Instructions in CMPT 295

Delve into the world of parallelism and vector instructions in CMPT 295 as you explore fixed-length vector intrinsics, RISC-V concepts, computer programming fundamentals, processor execution processes, scalar and vector loops, and more. Discover the intricacies of memory, data arrays, structs, integ

1 views • 45 slides

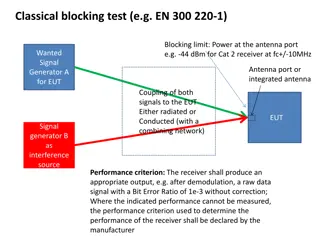

Classical Blocking Test and Receiver Performance Criteria

Classical blocking test procedures such as EN 300.220-1 outline limits on power at the antenna port for receivers, with criteria for achieving desired performance levels without errors. Manufacturers must declare appropriate performance criteria for devices, even if certain performance metrics are n

0 views • 6 slides

Understanding the Non-Blocking Michael Scott Queue

The Non-Blocking Michael Scott Queue, presented by Gurudatta Patil, is a thread-based data structure where threads help each other in managing a queue efficiently. Threads collaborate to add nodes at the tail and remove them from the head, ensuring smooth operation even in a non-empty queue scenario

0 views • 17 slides

Exploring Caching Techniques in Web Systems

Dive into the world of web caching with concepts like consistent hashing, Bloom filters, and shared caches for enhanced performance and efficiency. Discover the challenges faced in managing large-scale caches and learn about innovative solutions and ideas in the field of web systems.

0 views • 21 slides

Enhancing Multi-Node Systems with Coherent DRAM Caches

Exploring the integration of Coherent DRAM Caches in multi-node systems to improve memory performance. Discusses the benefits, challenges, and potential performance improvements compared to existing memory-side cache solutions.

0 views • 28 slides

Enhancing Memory Cache Efficiency with DRAM Compression Techniques

Explore the challenges faced by Moore's Law in relation to bandwidth limitations and the innovative solutions such as 3D-DRAM caches and compressed memory systems. Discover how compressing DRAM caches can improve bandwidth and capacity, leading to enhanced performance in memory-intensive application

0 views • 48 slides

Bi-Decomposition of Large Boolean Functions Using Blocking Edge Graphs

Bi-decomposition is a vital technique in logic synthesis for restructuring Boolean networks. This paper discusses the methodology of breaking down large Boolean functions using Blocking Edge Graphs (BEG) to simplify physical design and reduce complexity. The process involves constructing BEG, perfor

1 views • 29 slides

Summer Fellows 2024: Dive into OSDF Caches and IP Geolocation Challenges

Explore the Summer Fellows 2024 program focusing on topics like Glideins, IP geolocation challenges, OSDF Caches, and the use of AI in OSPool Failure Classification. Participants delve into learning the GlideinWMS system and grappling with issues related to network latency, hops, and machine learnin

0 views • 64 slides

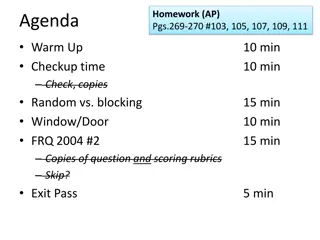

AP Statistics Homework Agenda and Experimental Design Example

In this AP Statistics homework agenda, students work on warm-up questions, checkups, and a controlled experiment design example involving paper airplanes and natural light impact on test scores. The agenda covers various topics such as confounding variables, random vs. blocking, and controlled exper

0 views • 15 slides

Exploring Real-World Concurrency Bugs in Go Programming Language

Golang, a programming language designed for efficient concurrency, utilizes lightweight threads called goroutines. This study delves into 171 Go concurrency bugs from various sources, analyzing root causes and fixing strategies. Highlighted results reveal insights for developers, pointing out that m

0 views • 36 slides

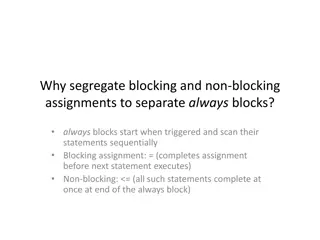

Understanding Blocking and Non-blocking Assignments in Verilog

Explore the intricacies of segregating blocking and non-blocking assignments to separate always blocks in Verilog. Learn about the differences between blocking and non-blocking assignments, their implications on sequential execution, and how to use them effectively in hardware description language p

0 views • 9 slides

Verilog FF Circuit Examples & Assignments Overview

Delve into Verilog FF circuit examples such as Gated D Latch and D Flip-Flop. Understand blocking and non-blocking assignments, their differences, and practical implications. Learn when to use each assignment method in Verilog design for combinational always blocks.

0 views • 17 slides

Architecting DRAM Caches for Low Latency and High Bandwidth

Addressing fundamental latency trade-offs in designing DRAM caches involves considerations such as memory stacking for improved latency and bandwidth, organizing large caches at cache-line granularity to minimize wasted space, and optimizing cache designs to reduce access latency. Challenges include

0 views • 32 slides

Chi: A Scalable and Programmable Control Plane for Distributed Stream Processing

Distributed stream processing systems are increasingly crucial for various production use cases, such as real-time dashboards, machine learning, and interactive debugging. The challenges of handling large variability in production ingestion workloads and high-degree data skew in queries are addresse

1 views • 20 slides

Youth Football: Finding the Right Backfield Qualities

Discover the essential qualities to look for in young football players for the backfield position: footwork, body language, toughness, blocking skills, mental resilience, and speed. Learn about common bad behaviors to correct and drills to enhance body language and footwork, as well as the importanc

0 views • 10 slides

CSE351 Spring 2019 - Caches and Memory Concepts

Exploring the intricacies of caching in CSE351 Spring 2019, delving into memory management, data structures, assembly language, Java comparisons, and mnemonic aids. The course covers practical applications and theoretical underpinnings, including memory allocation, virtual memory, and processor cach

0 views • 31 slides

CSE351 Autumn 2017: Caches Instructor and TA Information

The content provides information about the CSE351 course on caches for Autumn 2017, including details about the instructor, teaching assistants, administrative updates, midterm policies, course roadmap, units and prefixes, mnemonic techniques, and execution time analysis. It also includes important

0 views • 31 slides

Understanding Caches and the Memory Hierarchy in Computer Systems

Delve into the intricacies of memory hierarchy and caches in computer systems, exploring concepts like cache organization, implementation choices, hardware optimizations, and software-managed caches. Discover the significance of memory distance from the CPU, the impact on hardware/software interface

0 views • 84 slides

Efficient Handling of Cache Miss Rate in FPGAs

This study focuses on improving cache miss rate efficiency in FPGAs through the implementation of non-blocking caches and efficient Miss Status Holding Registers (MSHRs). By tracking more outstanding misses and utilizing memory-level parallelism, this approach proves to be more cost-effective than s

0 views • 44 slides

Pre-Operative Considerations for Equine Castration

Selection of a technique, common agents used to anaesthetize horses, scrubbing procedure, and blocking method are essential pre-operative considerations for equine castration. Closed and half-closed techniques decrease post-operative complications, while various agents can be used for sedation. Prop

0 views • 6 slides

Proxies, Caches, and Scalable Software Architectures

Statelessness, proxies, and caches play key roles in creating scalable software architectures. The lecture explains the concepts of proxies and caches, highlighting their functions in enhancing performance and scalability. Proxies act as intermediaries for requests, while caches store frequently acc

0 views • 13 slides

Understanding Web Caching: An Overview

Web caching, implemented through various types of caches like browser cache, proxy cache, and gateway cache, plays a crucial role in improving content availability, reducing network congestion, and enhancing user experience by saving bandwidth and decreasing latency. It addresses the challenges pose

0 views • 27 slides

Analyzing Blocking Probability in Wideband Links with Narrowband Frequency Hopping

This document delves into the analysis of the likelihood of wideband link obstructions resulting from multiple active narrowband frequency hopping (NBFH) links. A dynamic Energy Detection Threshold (EDT) approach is suggested for mitigation. The study also explores scenarios involving single and mul

0 views • 18 slides

Memory and Caches in CSE 351 Spring 2020: Insights and Roadmap

Exploring the world of memory and caches in CSE 351 Spring 2020 led by Instructor Ruth Anderson and her dedicated team of Teaching Assistants. Discover the essential topics covered such as data integers, x86 assembly, processes, and more. Dive into the nuances of memory allocation, Java implementati

0 views • 30 slides

Intelligent DRAM Cache Strategies for Bandwidth Optimization

Efficiently managing DRAM caches is crucial due to increasing memory demands and bandwidth limitations. Strategies like using DRAM as a cache, architectural considerations for large DRAM caches, and understanding replacement policies are explored in this study to enhance memory bandwidth and capacit

0 views • 23 slides

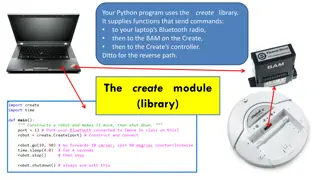

Python Create Library Overview

This Python program uses the Create library to send commands, enabling communication between your laptop's Bluetooth radio, the BAM on the Create robot, and the Create's controller. The library facilitates non-blocking commands for controlling the robot's movements and sensors, with specific instruc

0 views • 9 slides

Understanding CILK: An Efficient Multithreaded Runtime System

CILK is a multithreaded runtime system designed to develop dynamic, asynchronous, and concurrent programs efficiently. It utilizes a work-stealing thread scheduler and relies on a directed acyclic graph (DAG) model for computations. With a focus on optimizing critical paths and total work, CILK enab

0 views • 44 slides

Understanding Lock-Free and Wait-Free Algorithms in Concurrent Data Structures

Illustration of lock-free and wait-free algorithms compared to blocking algorithms, with insights on concurrent object execution, blocking vs. non-blocking algorithms, definitions, comparisons between locks, lock-free, and wait-free approaches, and explanations on making algorithms wait-free. Exampl

0 views • 23 slides

Selpercatinib 40 & 80 mg Tablets in India: For RET Fusion-Positive Cancers

Selpercatinib 40 & 80 mg tablets provide targeted treatment for RET fusion-positive cancers, effectively blocking RET mutations in cancers like non-small cell lung and thyroid cancer. Selpercatinib 40 & 80 mg in India, offers a specialized approach f

0 views • 1 slides