Understanding MIPS Part II: Memory Organization and Instructions

Explore the intricacies of Memory Organization in the context of MIPS architecture, covering topics such as Memory Transfer Unit, Word Alignment, Load and Store Instructions, Making Decisions with Conditional Branching and Unconditional Jumps, Loops, Arrays and practical exercises. Learn about the m

16 views • 43 slides

Network Function Abstraction A delicate question of (CPU) affinity?

Exploring the delicate balance of CPU affinity in network function abstraction, including challenges, benefits, and solutions like CPU pinning for network workloads. Learn about the impact on performance and scalability, as well as the importance of proper configuration in virtual and physical envir

3 views • 40 slides

Understanding the Basics of Computer Hardware and CPU

Explore the fundamental concepts of information technology, focusing on hardware components like the CPU, control unit, ALU, registers, and cache memory. Learn about the functions of these parts and how they contribute to a computer's performance and speed.

3 views • 37 slides

Understanding Computer Architecture in CSE502

Exploring the intricate details of computer architecture in CSE502, covering concepts such as instruction commit, pipeline stages, program execution order, CPU state management during context switches, and implementation in the CPU. The focus is on the sequential part and the unified register file,

1 views • 26 slides

Understanding Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

MIPS CPU Design Using Verilog and Instruction Set Architecture Overview

Explore the world of MIPS CPU design using Verilog with a deep dive into Instruction Set Architecture (ISA), SPIM instruction formats, addressing modes, and more. Learn about the key components such as Program Counter (PC), Instruction Memory (IM), Register Files (RF), Arithmetic Logic Unit (ALU), D

1 views • 29 slides

Understanding Interrupts in Embedded Systems

In embedded systems, interrupts play a crucial role in letting peripherals notify the CPU of state changes. They are events external to the current process that disrupt the normal flow of instruction execution, typically generated by hardware devices. By using interrupts, CPUs can efficiently handle

1 views • 12 slides

Understanding von Neumann Architecture in Parallel & Distributed Systems

Exploring the von Neumann architecture, this lecture delves into the components like main memory, CPU, registers, and data transfer. It discusses the bottleneck problem and modifications made to enhance CPU performance, such as caching methods. The web presentation offers insights into key aspects o

0 views • 23 slides

Overview of MIPS Arithmetic and Logic Instructions in COE 301

MIPS Architecture consists of R-Type and I-Type instruction formats for arithmetic, logical, shift, and immediate constant operations. It includes a variety of general-purpose registers and specific units for execution, floating-point operations, and memory handling. The presentation outlines the st

2 views • 29 slides

Understanding Cache Memory in Computer Architecture

Cache memory is a crucial component in computer architecture that aims to accelerate memory accesses by storing frequently used data closer to the CPU. This faster access is achieved through SRAM-based cache, which offers much shorter cycle times compared to DRAM. Various cache mapping schemes are e

2 views • 20 slides

Anatomy of a Computer System: Hardware Components and Functions

A typical computer system consists of hardware and software working together to perform various computational tasks. The hardware components include the central processing unit (CPU), input/output devices, storage units, and the motherboard. The CPU acts as the main brain of the computer, performing

6 views • 6 slides

Understanding Computer Processing Systems

Computer processing systems consist of various components such as the control unit, ALU, input unit, CPU, output unit, memory, and more. Input devices feed raw data to the computer, while output devices provide processed information. The CPU plays a crucial role in executing instructions and data pr

0 views • 13 slides

Performance Analysis of Different MIPS Processors

This analysis compares two different implementations (P1 and P2) of the same instruction set based on clock rates, CPI values, peak performances, and execution times on a 3GHz MIPS processor. The performance trade-offs for changes made to an MIPS process are explored using a breakdown of different p

0 views • 42 slides

MIPS Single-cycle Datapath Analysis for Instruction SW

Examine the operation of the single-cycle datapath for a specific MIPS instruction "SW.R4,-100(R16)". This analysis covers the instruction word value, register numbers, control signals, and the logic diagram implementation. Dive into details like instruction word encoding, register file operations,

0 views • 55 slides

Software Engineering Design Principles and Concepts

The chapter discusses the essential principles and concepts in software design, highlighting the four key design models - data design, architectural design, interface design, and component-level design. It emphasizes the importance of traceability to the analysis model, minimizing the gap between so

0 views • 36 slides

Understanding CPU Scheduling in Operating Systems

In a single-processor system, processes take turns running on the CPU. The goal of multiprogramming is to keep the CPU busy at all times. CPU scheduling relies on the alternating CPU and I/O burst cycles of processes. The CPU scheduler selects processes from the ready queue to execute when the CPU i

1 views • 26 slides

Understanding System on Chip (SoC) Design and Components

Explore the world of System on Chip (SoC) design, components, and working flow. Learn about Intellectual Properties (IP), platform-based design, typical design flows, top-down design approach, and the emerging Electronic System Level (ESL) design flow. Discover the essential components of an SoC, su

0 views • 45 slides

Understanding MIPS I/O and Interrupt Handling

Delve into the world of MIPS architecture, exploring how I/O operations and interrupts are managed. Learn about memory organization, system functions, I/O registers, and kernel data. Discover how SPIM facilitates input and output handling, including reading from the keyboard and managing output. Div

0 views • 18 slides

Understanding MIPS Instruction Sets and Binary Execution

This lecture covers the mapping of MIPS instructions to binary for execution, the use of pseudo-instructions to improve code readability, and the handling of large constants. It discusses levels of representation and interpretation, the concept of stored-program computers, addressing in memory, bina

0 views • 50 slides

Understanding MIPS Functions and Calling Conventions

MIPS functions in assembly language are called using the 'jal' instruction, passing arguments in specific registers. Functions must end with 'jr $ra' and have explicit declarations. MIPS functions are stored separately from the main function in memory. The 'jal' instruction jumps to a specified addr

0 views • 18 slides

Introduction to MIPS Assembly Programming with MARS

Introduction to MIPS Assembly Programming with MARS including instructions, I-Type format, register initialization, addi instructions, and translation to machine code using an assembler. Learn how to perform basic arithmetic operations in MIPS assembly language.

0 views • 61 slides

Understanding MACRA and MIPS for Post-Acute Care Providers

Explore the key provisions of MACRA impacting post-acute care (PAC) providers, including the Merit-based Incentive Payment System (MIPS) and Advanced Alternative Payment Models (APMs). Learn about quality reporting requirements, payment structures, and participation options under MACRA to optimize r

0 views • 20 slides

Understanding MIPS Arithmetic Logic Unit (ALU)

The MIPS ALU is the heart of computer calculations, performing functions like add, and, or, and sub. This article delves into designing a full ALU, starting from a 1-bit full adder to a 32-bit ALU. It explores how operations like and, or, and addition are carried out within the ALU, and how to imple

0 views • 28 slides

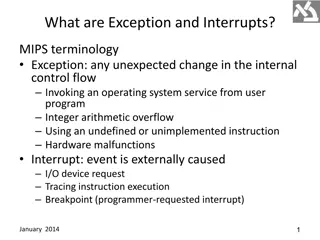

Exception Handling and Interrupts in MIPS Architectures

Exception and interrupts in MIPS play a crucial role in handling unexpected events and external requests efficiently. Exceptions include changes in control flow, arithmetic overflows, and hardware malfunctions, while interrupts are externally caused events like I/O requests. When an exception occurs

1 views • 29 slides

Understanding Computer Architecture: Exploring MIPs, Assembly Code, and BIOS Functions

Dive into the world of computer architecture with a focus on MIPs assembly language, basic program formats, BIOS functions, and system calls. Learn about the role of the OS kernel, memory addresses, and control flow in executing programs efficiently.

0 views • 16 slides

Understanding CPU Structure and Function in Computer Organization and Architecture

Exploring the intricate details of CPU architecture, this content delves into the essential tasks of fetching, interpreting, processing, and writing data. It discusses the significance of registers, user-visible registers, general-purpose registers, and condition code registers in CPU operations. Ad

0 views • 83 slides

Understanding CPU Architecture in Computing for GCSE Students

Explore the fundamental concepts of CPU architecture, including the Von Neumann Architecture, common CPU components like ALU and CU, and how characteristics such as Clock Speed and Cache Size impact performance. Learn about the Fetch-Execute Cycle and the essential hardware components of a computer

0 views • 18 slides

Intel CPU Architectures Overview: Evolution and Features

Explore the evolution and key features of various Intel CPU architectures including Pentium, Core, and Pentium 4 series. Learn about the pipeline stages, instruction issue capabilities, branch prediction mechanisms, cache designs, and memory speculation techniques employed in these processors. Gain

0 views • 11 slides

Understanding the Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

MIPS 2022 Updates and Program Recap for Large Practices

Explore the latest updates for the Merit-Based Incentive Payment Program (MIPs) in 2022, including performance year changes, quality category considerations, penalty mitigation strategies, and historical thresholds. Learn how MIPS rewards clinicians for high-quality, cost-effective care under MACRA.

0 views • 27 slides

Understanding Operating System Concepts: Multiprogramming, Multiprocessing, Multitasking, and Multithreading

In the realm of operating systems, terms like multiprogramming, multiprocessing, multitasking, and multithreading can often be confusing due to their similar appearance but distinct meanings. These concepts play a crucial role in efficiently managing resources in a computing system, particularly in

0 views • 6 slides

Understanding CPU Scheduling Concepts at Eshan College of Engineering, Mathura

Dive into the world of CPU scheduling at Eshan College of Engineering in Mathura with Associate Professor Vyom Kulshreshtha. Explore topics such as CPU utilization, I/O burst cycles, CPU burst distribution, and more. Learn about the CPU scheduler, dispatcher module, scheduling criteria, and the impl

0 views • 18 slides

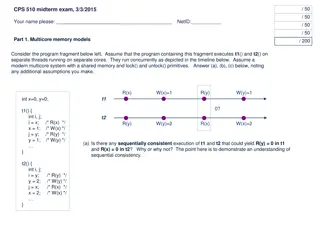

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Efficient Video Encoder on CPU+FPGA Platform

Explore the integration of CPU and FPGA for a highly efficient and flexible video encoder. Learn about the motivation, industry trends, discussions, Xilinx Zynq architecture, design process, H.264 baseline profile, and more to achieve high throughput, low power consumption, and easy upgrading.

0 views • 27 slides

Understanding Barrel Shifter in CPU Design

Barrel shifter is a vital component in CPU architecture, enabling shifting and rotating operations on data inputs based on control signals. The shifter consists of two main blocks - Shift-and-Rotate Array (SARA) and Control Logic. SARA, designed with multiple stages of cells, executes shift and rota

0 views • 12 slides

Understanding Context Switching and User-Kernel Interaction in Operating Systems

Context switching in operating systems involves a seamless transition between user-level threads without the kernel's awareness. User-level code manages register state and stack pointers, while user-kernel mode switching requires changing processor privilege levels and agreement on information excha

0 views • 25 slides

Understanding CPU Virtualization and Execution Control in Operating Systems

Explore the concepts of CPU virtualization, direct execution, and control mechanisms in operating systems illustrated through a series of descriptive images. Learn about efficient CPU virtualization techniques, managing restricted operations, system calls, and a limited direct execution protocol for

0 views • 18 slides

Enhancing gem5's GPUFS Support for Improved Simulation Speed

Addressing challenges in application scaling, this project focuses on enhancing gem5's GPUFS support to improve simulation speed by functionally simulating memory copies and adding KVM CPU-GPU support. The introduction covers prior CPU-GPU support in gem5, ML support, and the introduction of GPUFS s

0 views • 19 slides

Understanding Instruction Set Architectures (ISAs) in Computer Science

Explore the concepts of RISC, CISC, and ISA variations in computer architecture. Dive into the differences between MIPS, ARM, X86, and other ISAs, focusing on load/store, arithmetic, control flow, and more. Gain insights into the evolution and variations of ISAs, and discover the alternatives beyond

0 views • 37 slides

Illustrated Design of a Simplified CPU with 16-bit RAM

Demonstrates the design of a basic CPU with 11 instructions and 4096 16-bit RAM, showcasing the assembly of a general-purpose computer using gates and registers. The CPU comprises 8 key registers for various functions, employing a sequential circuit for instruction execution. The machine language pr

0 views • 31 slides