Gain Analysis for Coordinated AP Transmissions in IEEE Enterprise R3 Network

This document discusses gain analysis results for coordinated AP transmissions in the IEEE Enterprise R3 network, focusing on tail latency gain for aperiodic traffic. Simulation setups, topology details, and results for different coordination schemes (C-TDMA, C-RTWT, and combined) are provided, show

5 views • 6 slides

Understanding Computer Networks: Basics, Components, and Topologies

Computer networks are essential for sharing resources, exchanging files, and enabling electronic communications. This includes components like senders, receivers, messages, transmission media, and various modes of communication. The need for networking arises from file sharing, resource sharing, com

13 views • 28 slides

Electric Grid Congestion Management Updates

Working Group updates on congestion management strategies including proposed fixes for reliability deployment pricing, mitigations for ESRs, and congestion mitigation using topology reconfigurations. Discussions covered locational price signals, resource payments, offer cap designs, and operational

0 views • 4 slides

Understanding Electromigration Effects in IC Interconnect Lines

Background: As IC circuits advance, preventing failures like electromigration is crucial. Vacancies lead to potential failures in metal interconnects by causing macroscopic voids and hillocks. Explore the governing equations and physics interfaces behind the migration of vacancies in IC circuits. Im

0 views • 14 slides

Understanding Mesh and Star Network Topologies

Network topology plays a crucial role in network performance and maintenance costs. Mesh topology connects every device with a dedicated link, providing reliability and security. On the other hand, star topology connects devices to a central hub, ensuring communication through the hub. Explore the a

0 views • 22 slides

Considerations on Coordinated OFDMA Operation in IEEE 802.11

The document discusses the Coordinated OFDMA (C-OFDMA) operation as a part of Multi-AP coordination schemes within the IEEE 802.11 standard. It covers resource allocation options, topology considerations, resource allocation methods, capability announcement procedures, and negotiation processes betw

0 views • 15 slides

Introduction to Topological Spaces and Examples

Topology is the study of surfaces derived from Greek words meaning surface and discourse. In mathematics, a topological space is a set with a family of subsets satisfying specific properties. Examples include the open ball, open set, indiscrete topology, discrete topology, co-finite topology, and co

0 views • 14 slides

Understanding Physical Network Topologies

Physical network topology refers to the layout of cables, computers, and peripherals in a network, distinct from logical topology. Common physical topologies include Star, Ring, Linear Bus, Tree, and Mesh. Each topology has its advantages and disadvantages, impacting network performance and reliabil

0 views • 16 slides

Understanding IEEE 802.11-20/0410r4 Coordinated Spatial Reuse Procedure

This document presents the Coordinated Spatial Reuse (CSR) procedure in IEEE 802.11-20/0410r4, focusing on the transmission schemes and necessary information for effective spatial reuse. It outlines the topology of CSR environments, acquisition of information for CSR, CSR capability announcement by

8 views • 23 slides

Oncor Far West TX Transmission Projects Overview

This presentation outlines the Oncor Far West Texas transmission projects approved by ERCOT, including planned developments for 2019. The projects aim to enhance the reliability and efficiency of the electrical grid in the region, catering to factors like load, generation, engineering, system protec

0 views • 8 slides

Understanding CMOS Layers and Interconnect Design in Semiconductor Manufacturing

This content provides detailed insights into the CMOS layers, n-well process, p-well process, twin-tub process, metal interconnect layers, gate design, and layout strategies involved in semiconductor manufacturing. Explore the images and descriptions to grasp the complexities of MOS arrays, gate con

0 views • 27 slides

Understanding EIGRP: A Comprehensive Overview

Enhanced Interior Gateway Routing Protocol (EIGRP) is a dynamic routing protocol providing various advantages to network administrators. It is a classless routing protocol supporting VLSM and is considered an Interior Gateway Protocol (IGP). EIGRP uses advanced distance vector routing and is known f

1 views • 5 slides

Understanding Quotient Spaces in Mathematics

In group theory, a subgroup H of a group G helps decompose G into equal-size disjoint subsets called cosets. Quotient spaces in mathematics involve equivalence classes under a given relation and a specific topology. Furthermore, in linear algebra, the quotient of a vector space by a subspace results

0 views • 8 slides

Advancements in Signal Processing for ProtoDUNE Experiment

The team, including Xin Qian, Chao Zhang, and Brett Viren from BNL, leverages past experience in MicroBooNE to outline a comprehensive work plan for signal processing in ProtoDUNE. Their focus includes managing excess noise, addressing non-functional channels, and evolving signal processing techniqu

1 views • 23 slides

SAT-Based Exact Synthesis Using DAG Topology Families

Explore the world of exact synthesis in digital circuit design utilizing SAT solvers to achieve precise results. Understand the challenges, decision problems, algorithms, motivation behind exact synthesis, and the contribution of SAT solvers in mitigating runtime. Discover the concept of DAG topolog

0 views • 17 slides

Understanding Interconnect Topology Design and Performance Metrics

Interconnect topology design plays a crucial role in determining the cost and performance of a network. Factors such as the number of switches and links, switch port count, network layout, throughput, packet latency, average hop counts, nodal degree, hop count, and diameter are essential considerati

0 views • 38 slides

Understanding Interconnection Networks Topology

Exploring the topology of interconnection networks helps determine the arrangement of channels and nodes, impacting network cost, performance, latency, energy consumption, and complexity of implementation. Abstract metrics such as degree, hop count, and network diameter play crucial roles in evaluat

1 views • 56 slides

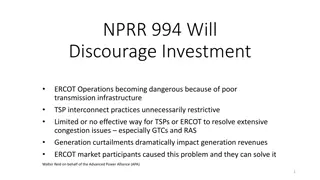

Challenges in ERCOT Transmission Infrastructure & Operations

Poor transmission infrastructure and restrictive interconnect practices in ERCOT are leading to dangerous operations, congestion issues, and generation revenue impacts. Concerns include increased RAS proposals, challenges with GTC management, and minimalist interconnect processes. The need for impro

0 views • 9 slides

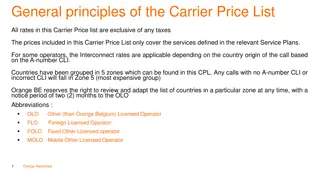

Overview of Carrier Price List and Country Groupings

The Carrier Price List outlines rates exclusive of taxes, covering defined services. Countries are grouped into zones, affecting interconnect rates. The list includes Zone 1 (Belgium, EU, EFTA, China, India) and subsequent groups. Orange BE may adjust country zoning.

0 views • 8 slides

IBIS Interconnect: Models and Task Group Overview

The IBIS Interconnect draft explores models representing package and on-die interconnect, with separate or combined approaches for on-die, package, supply, and signal interconnect. The IBIS Interconnect Task Group, comprising major contributors such as Altera, Cadence Design Systems, Intel Corp, and

0 views • 10 slides

Overview of IBIS Interconnect Task Group Models

The IBIS Interconnect Task Group focuses on modeling package and on-die interconnects, with support for separate or combined interconnect models. They meet weekly to discuss contributions from major companies like Altera, Cadence, Intel, and more. The models include terminals for differential signal

0 views • 17 slides

Understanding Net Metering with FPUA Fort Pierce Utilities Authority

Net metering enables customers to own or lease renewable generation, interconnect with the electric system, and offset consumption. Customers can use solar energy in their homes and the excess energy generated can be sold back to the grid. The rate utilities pay for excess generation varies and is s

0 views • 11 slides

Unified Approach for Performance Evaluation and Debug of System on Chip in Early Design Phase

This presentation discusses the challenges related to system-on-chip design, focusing on bandwidth issues, interconnect design, and DDR efficiency tuning. It explores the evolution of performance evaluation methods and the limitations of existing solutions. The need for a unified approach for early-

0 views • 28 slides

Machine Learning of Interconnect Coupling Delay and Transition Effects

This research paper explores the use of machine learning to study interconnect coupling delay and transition effects in VLSI design. It discusses the challenges of calibrating non-SI to SI timing reports, the impact of clock period adjustments on path slack, and the complexities involved in the cali

0 views • 32 slides

Understanding Cache Coherency and Multi-Core Programming

Explore the intricate world of cache coherency and multi-core programming through images and descriptions covering topics such as how cache shares data between cores, maintaining data consistency, CPU architecture, memory caching, MESI protocol, and interconnect bus communication.

0 views • 97 slides

Cutting-Edge Interconnect Technology for High-Performance Computing

Explore the world of high-performance embedded computing through images and descriptions detailing key components like terrestrial autonomous vehicles, wireless infrastructure, FPGA-based data exchange, and more. The content dives into fault tolerance, data processing, redundant computing, and hardw

0 views • 12 slides

Fault-Tolerant Engineered Networks Overview

Explore the design and challenges of fault-tolerant engineered networks such as FatTrees, with a focus on recovery strategies, topology innovations, and failure detection mechanisms. Learn about the co-design of topology, routing protocols, and failure detectors for optimal performance in data cente

0 views • 27 slides

Exploring Topological Band Theory and Quantum Phases in Electronic Matter

Delve into the fascinating realm of topological band theory, examining the insulating state, band topology in different dimensions, symmetry-protected topological band insulators, and the interplay between symmetry and topology. Uncover the principles underlying matter symmetry, quantum phases, and

0 views • 29 slides

Optimizing Multi-Party Video Conferencing through Server Selection and Topology Control

This paper proposes innovative methods for multi-server placement and topology control in multi-party video conferences. It introduces a three-step procedure to minimize end-to-end delays between client pairs using D-Grouping and convex optimization. The study demonstrates how combining D-Grouping,

0 views • 13 slides

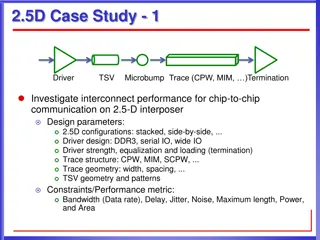

Investigating Chip-to-Chip Communication Performance on 2.5D Interposer

Investigate the performance of chip-to-chip communication on a 2.5D interposer by analyzing interconnect parameters such as configurations, driver design, trace structure, TSV geometry, and channel modeling. Explore methods like SPICE simulation and MATLAB GUI for performance estimation and optimiza

0 views • 18 slides

Understanding Software-Defined Networking (SDN) Threats and Countermeasures

Software-Defined Networking (SDN) revolutionizes network management by separating control and data planes, providing flexibility, and enabling innovative flow handling. This presentation explores SDN concepts, OpenFlow protocol, operational distinctions from legacy networks, and the importance of to

0 views • 27 slides

Extending OVN Forwarding Pipeline for Topology-based Service Injection

Explore how to extend the OVN forwarding pipeline to enable topology-based service injection, allowing external applications to influence flow routes dynamically, such as for service chaining and DPI. The extensible pipeline facilitates the interaction with base OpenFlow pipelines, distributed netwo

0 views • 17 slides

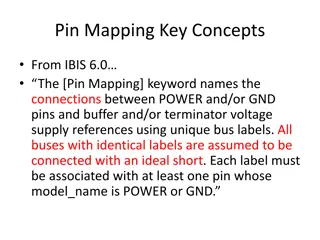

Understanding Pin Mapping and Interconnect in IBIS 6.0

Pin Mapping in IBIS 6.0 defines the connections between POWER/GND pins and buffer/terminator voltage supplies using unique bus labels. Interconnects between VDD pins and buffer supply terminals are crucial, with all pins associated with a named supply being shorted together. Draft 9 Interconnects an

0 views • 6 slides

InterConnect A/S - Driving Innovation in Legal Technology

InterConnect A/S, established in 1996 in Svendborg, Denmark, specializes in software development and ERP/database systems. As a key player in the LIT Pilot Project, they are actively involved in developing a search machine for legal interpreters and translators. With a strong track record in project

0 views • 16 slides

High-Performance Gate Sizing with Signoff Timer: VLSI Design Challenges

This study delves into the intricate realm of gate sizing in VLSI design, focusing on optimizing power and delay through effective approaches and addressing challenges such as interconnect delay, inaccurate internal timers, and critical paths. Previous gate sizing techniques are evaluated, and a met

0 views • 34 slides

Understanding Homotopy and Fundamental Groups in Topology

Explore the concepts of homotopy and fundamental groups in topology, where objects with the same structure can be classified into classes, and the fundamental group characterizes loops. Discover the fundamental group of a torus, its identity elements, closure, associativity, and inverses. Homotopy a

0 views • 10 slides

Understanding the Impact of Crooked Traceroute on Network Topologies

Traceroute-based algorithms play a crucial role in collecting network topology data, but the introduction of per-flow load balancing has raised concerns about the accuracy of these algorithms. This study examines the implications of crooked traceroute on false link inference rates and the identifica

0 views • 23 slides

Energy-Aware Optimization of BEOL Interconnect Stack Geometry

This study focuses on optimizing Back-End-of-Line (BEOL) interconnect stack geometry in advanced nodes for improved performance and energy efficiency. It explores the motivations, background, and potential benefits of Design-Aware Manufacturing (DAM) and Manufacturing-Aware Design (MAD) methodologie

0 views • 28 slides

Randomness in Topology: Persistence Diagrams, Euler Characteristics, and Möbius Inversion

Exploring the concept of randomness in topology, this work delves into the fascinating realms of persistence diagrams, Euler characteristics, and Möbius inversion. Jointly presented with Amit Patel, the study uncovers the vast generalization of Möbius inversion as a principle of inclusion-exclusio

0 views • 57 slides

Understanding Interconnection Networks: Topology and Routing

Interconnection networks play a crucial role in determining the arrangement of channels and nodes within a network, similar to a road map guiding traffic flow. Topology overview defines the network structure, while abstract metrics help evaluate performance and cost. Latency and throughput are key f

0 views • 49 slides