File I/O and Inter-Process Communication Through Pipes

Delve into the intricacies of file operations, I/O redirection, and inter-process communication through pipes as discussed in the readings of "Advanced Programming in the Unix Environment" (APUE). Explore data structures for open files, file descriptor tables, implications of data structures, system

4 views • 18 slides

Guidelines for Upholding Rights of LGBTQ

In light of evolving societal norms and the imperative to safeguard the rights and dignity of LGBTQ individuals and inter-faith\/inter-caste couples, the Supreme Court has given guidelines for the handling of habeas corpus petitions and petitions for police protection.\nBackground:\nRecent instance

9 views • 4 slides

727003-B21 HP BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT

Refurbished | HP 727003-B21 | BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/727003-b21-hp-bl460c-g9-e5-2695-v3-14-core-processor-kit\/

0 views • 1 slides

Cache and Virtual Memory in Computer Systems

A computer's memory system is crucial for ensuring fast and uninterrupted access to data by the processor. This system comprises internal processor memories, primary memory, and secondary memory such as hard drives. The utilization of cache memory helps bridge the speed gap between the CPU and main

3 views • 47 slides

Effective Communication Skills for Healthcare Professionals

Enhance your communication skills with the Accelerated Preceptorship Communication Session by Desiree Cox. Learn the importance of effective communication, different communication preferences, communication dynamics, non-verbal communication, listening skills, and more. Understand the communication

3 views • 28 slides

Buy 872012-B21 HPE BL460C GEN10 XEON-S 4110 PROCESSOR KIT

Refurbished | HPE 872012-B21 | BL460C GEN10 XEON-S 4110 PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/872012-b21-hpe-bl460c-gen10-xeon-s-4110-processor-kit\/

0 views • 1 slides

Processor Control Unit and ALU Implementation Overview

In Chapter 4, the processor's control unit and ALU are detailed in a simple implementation scheme. The ALU performs operations based on opcode values, while the control unit provides signals for various functions such as load/store, compare, and branch. Decoding techniques and control signal generat

2 views • 21 slides

Inter-Process Communication Signals in Operating Systems

Signals in inter-process communication are asynchronous notifications delivered to specific processes, allowing event-based programming. Processes can handle signal delivery by ignoring it, terminating, or invoking a signal handler. Signal handlers can be written in two ways - one handler for many s

0 views • 21 slides

Inter-Cluster Coordination and Information Management in Humanitarian Emergencies

Inter-Cluster Coordination and Information Management play vital roles in humanitarian emergencies. The coordination mechanism involves regular meetings convened by the RC/HC and coordinated by OCHA, providing opportunities for clusters to collaborate on shared planning, needs assessments, and poole

3 views • 13 slides

Computer System Architectures

Computer systems can be categorized into single-processor and multiprocessor systems. Single-processor systems have one main CPU but may also contain special-purpose processors. Multiprocessor systems have multiple processors that share resources, offering advantages like increased throughput, econo

2 views • 25 slides

Inter-Agency SEA Community Based Complaints Mechanism in Nigeria

The Inter-Agency SEA Community Based Complaints Mechanism in Nigeria facilitates safe and confidential reporting of complaints, particularly related to sexual exploitation and abuse (SEA), by beneficiaries. Through inter-agency coordination, this mechanism ensures effective collaboration, messaging,

2 views • 18 slides

Techniques for Reducing Connected-Standby Energy Consumption in Mobile Devices

Mobile devices spend a significant amount of time in connected-standby mode, leading to energy inefficiency in the Deepest-Runtime-Idle-Power State (DRIPS). This study introduces Optimized DRIPS (ODRIPS) to address this issue by offloading wake-up timer events, powering off IO signals, and transferr

2 views • 31 slides

Managing Inter-Departmental Transfers in Financial Accounting

Inter-departmental transfers involve recording and charging costs from one department to another, with different pricing bases like cost-based and market-based transfers. Unrealized profits in transfers are adjusted using stock reserves. Entries are made at the selling price to include costs and pro

1 views • 7 slides

In-Depth Look at Pentium Processor Features

Explore the advanced features of the Pentium processor, including separate instruction and data caches, dual integer pipelines, superscalar execution, support for multitasking, and more. Learn about its 32-bit architecture, power management capabilities, internal error detection features, and the ef

0 views • 24 slides

Trends in Computer Organization and Architecture

This content delves into various aspects of computer organization and architecture, covering topics such as multicore computers, alternative chip organization, Intel hardware trends, processor trends, power consumption projections, and performance effects of multiple cores. It also discusses the sca

5 views • 28 slides

Parallel Processing and SIMD Architecture Overview

Parallel processors in advanced computer systems utilize multiple processing units connected through an interconnection network. This enables communication via shared memory or message passing methods. Multiprocessors offer increased speed and cost-effectiveness compared to single-processor systems

4 views • 24 slides

Pipelined Control in Processor Architecture

Explore the intricacies of pipelined control in processor design, detailing the control signals required at each stage of the pipeline. Learn about data hazards, forwarding, and stalling techniques to ensure efficient instruction execution. Dive into the concept of optimized control values for strea

0 views • 16 slides

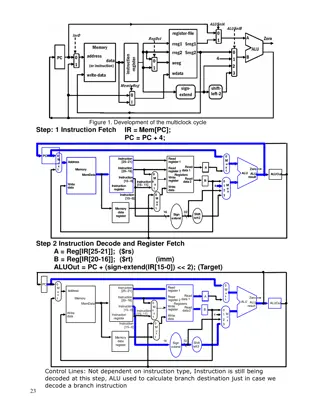

Development of Multiclock Cycle in Processor

The development process of the multiclock cycle in a processor is explained in detail through different steps, including instruction fetch, decode, register fetch, execution, and write-back for R-type instructions. Control lines and branching execution are also covered in the description. The conten

0 views • 5 slides

Overview of Inter-Processor Communication (IPC) in Processor Communication Link

Overview of Inter-Processor Communication (IPC) entails communication between processors, synchronization methods, and supported device types. The IPC architecture supports diverse use cases with various thread combinations and messaging types, catering to multi- or uni-processor environments. The A

0 views • 110 slides

Agreements on FR2 Inter-Band Carrier Aggregation Requirements

Agreements have been reached on the RRM requirements and scaling factors for FR2 inter-band Carrier Aggregation, focusing on common beam and independent beam management. Discussions include alignment with Release 16 specifications, scenarios, and RF architectures. Interruption requirements for diffe

0 views • 8 slides

Portable Inter-workgroup Barrier Synchronisation for GPUs

This presentation discusses the implementation of portable inter-workgroup barrier synchronisation for GPUs, focusing on barriers provided as primitives, GPU programming threads and memory management, and challenges such as scheduling and memory consistency. Experimental results and occupancy-bound

1 views • 61 slides

CITEL Working Instruments and Strategic Initiatives for Radiocommunications

Inter-American Telecommunication Commission (CITEL) plays a crucial role in coordinating strategic initiatives related to radiocommunications within the OAS. The Permanent Consultative Committee II (PCC.II) focuses on radiocommunications and works towards preparing for World Radiocommunication Confe

1 views • 10 slides

Inter-Process Communication in Computer Architecture

Explore the key concepts of Inter-Process Communication (IPC) in computer architecture, covering topics such as signals, message queues, shared memory, and handling signals. Learn how to send and handle signals, manage never-ending programs, and control processes using utilities like kill. Dive into

0 views • 20 slides

Challenges in Establishing a Secure Inter-Domain Routing System

The daunting task of creating a secure and trusted inter-domain routing system poses significant challenges due to the decentralized nature of the internet. Addressing issues such as propagation of false routing information, ensuring correct reachability, and dealing with the lack of a clear truth m

0 views • 15 slides

The Contact Hypothesis in Inter-group Relations

The contact hypothesis explores inter-group relations from a cognitive perspective, highlighting how initial stereotypes and prejudices can be challenged and changed through positive interactions. It emphasizes the importance of contact in altering perceptions and reducing prejudice, as demonstrated

0 views • 42 slides

Out-of-Order Processor Design Exploration

Explore the design of an Out-of-Order (OOO) processor with an architectural register file, aggressive speculation, and efficient replay mechanisms. Understand the changes to renaming, dispatch, wakeup, bypassing, register writes, and commit stages. Compare Processor Register File (PRF) based design

1 views • 29 slides

Classical Inter-Process Communication Problems

Classical Inter-Process Communication (IPC) problems such as the Dining Philosophers Problem and the Readers and Writers Problem are explored in-depth by Ali Akbar Mohammadi. The challenges, solutions, and non-solutions to these problems are discussed, shedding light on issues like starvation in con

0 views • 15 slides

Processor Cycles and Machine Cycles in 8085 Microprocessor

Processor cycles in microprocessors like 8085 involve executing instructions through machine cycles that are essential operations performed by the processor. In the 8085 microprocessor, there are seven basic machine cycles, each serving a specific purpose such as fetching opcodes, reading from memor

0 views • 17 slides

Inter-Process Communication in Operating Systems

Exploring the concept of Inter-Process Communication (IPC) in operating systems, this content delves into how processes cooperate, different IPC paradigms like message passing and shared memory, examples of cooperating processes, and the challenges and advantages of process cooperation. It also addr

0 views • 29 slides

Carnegie Mellon Inter-Process Communication Mechanisms

Carnegie Mellon Inter-Process Communication (IPC) mechanisms enable communication between processes living in different memory address spaces. This involves cooperating processes needing data transfer, resource sharing, event notification, and process control. IPC methods include Pipes, Shared Memor

0 views • 78 slides

New IDT/ICT Form: Streamlining Inter-Departmental and Inter-Company Transactions

Streamline inter-departmental and inter-company transactions with the new IDT/ICT form. Easily transfer funds between different departments within the same company and across different companies. Two identical forms cater to Foundation and Philanthropic accounts, enhancing efficiency in financial pr

0 views • 13 slides

Processor Organization in Computer Architecture

Processor organization involves key tasks such as fetching instructions, interpreting instructions, processing data, and storing temporary data. The CPU consists of components like the ALU, control unit, and registers. Register organization plays a crucial role in optimizing memory usage and control

0 views • 21 slides

Processor Structure and Function in Computing

Explore the key components and functions of processors in computing, including user-visible and control status registers, instruction cycle, instruction pipelining, processor tasks like data processing and instruction interpretation, and the roles of arithmetic and logic units and control units. Lea

0 views • 61 slides

Pipes in Process Communication

Pipes in process communication allow for high-throughput data transfer between parent and child processes. The kernel creates a communication stream through file descriptors, enabling one process to send data to another. Processes can use pipes for efficient inter-process communication, with the ker

1 views • 15 slides

Processor Generations and VM Sizing for Azure Migration

Exploring the impact of processor generations on CPU performance, factors like clock speed, instruction set, and cache size are crucial. Choosing the right-sized VM plays a vital role in optimizing Azure migration. Passmark CPU Benchmark results provide insights on Intel processor generations for Az

0 views • 9 slides

Efficient Inter-Company Netting Solutions for Multinational Corporations

Gain insights into the need for multi-currency inter-company netting systems, their benefits, limitations, and tips for successful implementation. Address global challenges in netting to streamline processes, reduce costs, enhance visibility, and improve efficiency in managing inter-company transact

0 views • 14 slides

Enhancing Data Movement Efficiency in DRAM with Low-Cost Inter-Linked Subarrays (LISA)

This research focuses on improving bulk data movement efficiency within DRAM by introducing Low-Cost Inter-Linked Subarrays (LISA). By providing wide connectivity between subarrays, LISA enables fast inter-subarray data transfers, reducing latency and energy consumption. Key applications include fas

0 views • 49 slides

Specialization in International Business Communication (SIBC)

Specialization in International Business Communication (SIBC) offered by the Department of Business Communication focuses on the critical role of communication in various business settings, emphasizing skills in language usage, communicative competence, and strategic language application. The progra

2 views • 11 slides

Enhancing Safety in Inter-Hospital Transfers for Intracranial Hemorrhage Patients

Background: Inter-hospital transfers pose safety risks due to care transitions and handoffs. This study discusses interventions to improve care quality and communication in such transfers, highlighting significant process improvements but non-significant clinical outcomes. Conclusion: Implementing

0 views • 8 slides

Constructive Computer Architecture Lab 6 Discussion

Lab 6 involves creating a 6-stage pipelined processor from a 2-stage pipeline, emphasizing architectural details and interactions between stages. Learn about common bugs, diagnosing processor hangs, testing outcomes, and processor state manipulation in this informative tutorial.

0 views • 23 slides