Equipment Management - LABS FOR LIFE PROJECT - INDIA

Histopathology and cytology equipment, focusing on the tissue processor, important parts, maintenance, and steps in tissue processing. Understand the significance of these tools in the microscopic examination of tissues for disease manifestations.

5 views • 30 slides

Evolution of Parallel Programming in Computing

Moores Law predicted the doubling of transistor capacity every two years, benefitting software developers initially. However, hardware advancements can no longer ensure consistent performance gains. Parallel computing, leveraging multicore architecture, has emerged as a solution to optimize performa

7 views • 10 slides

Introduction to Operating Systems

Explore the concepts of address translation, Translation Lookaside Buffer (TLB), TLB usage in modern processors, TLB invalidate mechanisms, and hardware design principles related to memory hierarchy using examples from the Intel i7 processor. Understanding the trade-offs and costs associated with TL

0 views • 30 slides

Bobcat Asphalt Processor Service Repair Manual Instant Download (SN AYYS00101 AND Above)

Please open the website below to get the complete manual\n\n\/\/ \n

0 views • 17 slides

727003-B21 HP BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT

Refurbished | HP 727003-B21 | BL460C G9 E5-2695 V3 14-CORE PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/727003-b21-hp-bl460c-g9-e5-2695-v3-14-core-processor-kit\/

0 views • 1 slides

John Deere 840 Bale Processor Operator’s Manual Instant Download (Publication No.OME76359)

Please open the website below to get the complete manual\n\n\/\/

0 views • 22 slides

John Deere 840 Bale Processor Operator’s Manual Instant Download (Publication No.OME77322)

Please open the website below to get the complete manual\n\n\/\/

0 views • 22 slides

Understanding Memory Organization in Computers

The memory unit is crucial in any digital computer for storing programs and data. It comprises main memory, auxiliary memory, and cache memory, each serving different roles in data storage and retrieval. Main memory directly communicates with the CPU, while cache memory enhances processing speed by

1 views • 37 slides

Understanding Computer Memory Systems and Organization

Memory systems in computer architecture play a crucial role in data storage and processing. They vary in purpose, performance, and capacity, from temporary storage like RAM to permanent storage. The main goal of a memory system is to ensure fast and uninterrupted access for the processor to enhance

0 views • 33 slides

Understanding Memory Ordering in Programming

Memory ordering in programming is crucial for developers to understand, as it dictates the sequence of memory operations at different levels - source code, program order, and execution order. Compiler optimizations and reordering of memory accesses can impact how code is executed by the processor, e

1 views • 30 slides

Understanding Cache and Virtual Memory in Computer Systems

A computer's memory system is crucial for ensuring fast and uninterrupted access to data by the processor. This system comprises internal processor memories, primary memory, and secondary memory such as hard drives. The utilization of cache memory helps bridge the speed gap between the CPU and main

2 views • 47 slides

Understanding Microcontrollers: Definition, Working, and Elements

A microcontroller (MCU) is a compact integrated circuit essential for embedded systems, controlling specific operations. This article delves into the definition, functioning, and key elements of microcontrollers, such as the processor, memory, and I/O peripherals. Explore how microcontrollers work,

0 views • 16 slides

Understanding Superscalar Processors in Processor Design

Explore the concept of superscalar processors in processor design, including the ability to execute instructions independently and concurrently. Learn about the difference between superscalar and superpipelined approaches, instruction-level parallelism, and the limitations and design issues involved

0 views • 55 slides

Understanding Basic Input/Output Operations in Computer Organization

Basic Input/Output Operations are essential functions in computer systems that involve transferring data between processors and external devices like keyboards and displays. This task requires synchronization mechanisms due to differences in processing speeds. The process involves reading characters

0 views • 11 slides

Buy 872012-B21 HPE BL460C GEN10 XEON-S 4110 PROCESSOR KIT

Refurbished | HPE 872012-B21 | BL460C GEN10 XEON-S 4110 PROCESSOR KIT | \u2713 FREE and FAST Ground Shipping across the U.S. | Best Price Guaranteed\n\n\/\/ \/872012-b21-hpe-bl460c-gen10-xeon-s-4110-processor-kit\/

0 views • 1 slides

Processor Control Unit and ALU Implementation Overview

In Chapter 4, the processor's control unit and ALU are detailed in a simple implementation scheme. The ALU performs operations based on opcode values, while the control unit provides signals for various functions such as load/store, compare, and branch. Decoding techniques and control signal generat

1 views • 21 slides

Understanding Instruction Set Architecture and Data Types in Computer Systems

In computer architecture, the Instruction Set Architecture (ISA) level is crucial in defining how a processor executes instructions. This includes the formal defining documents, memory models, registers, and various data types that can be supported. The ISA level specifies the capabilities of a proc

2 views • 13 slides

Understanding Computer System Architectures

Computer systems can be categorized into single-processor and multiprocessor systems. Single-processor systems have one main CPU but may also contain special-purpose processors. Multiprocessor systems have multiple processors that share resources, offering advantages like increased throughput, econo

2 views • 25 slides

Techniques for Reducing Connected-Standby Energy Consumption in Mobile Devices

Mobile devices spend a significant amount of time in connected-standby mode, leading to energy inefficiency in the Deepest-Runtime-Idle-Power State (DRIPS). This study introduces Optimized DRIPS (ODRIPS) to address this issue by offloading wake-up timer events, powering off IO signals, and transferr

1 views • 31 slides

Understanding Processor Interrupts and Exception Handling in Zynq Systems

Learn about interrupts, exceptions, and their handling in Zynq Systems. Explore concepts like interrupt sources, Cortex-A9 processor interrupts, interrupt terminology, and the difference between pooling and hardware interrupts. Gain insights into interrupt service routines, interrupt pins, interrupt

1 views • 60 slides

In-Depth Look at Pentium Processor Features

Explore the advanced features of the Pentium processor, including separate instruction and data caches, dual integer pipelines, superscalar execution, support for multitasking, and more. Learn about its 32-bit architecture, power management capabilities, internal error detection features, and the ef

0 views • 24 slides

Trends in Computer Organization and Architecture

This content delves into various aspects of computer organization and architecture, covering topics such as multicore computers, alternative chip organization, Intel hardware trends, processor trends, power consumption projections, and performance effects of multiple cores. It also discusses the sca

5 views • 28 slides

Parallel Processing and SIMD Architecture Overview

Parallel processors in advanced computer systems utilize multiple processing units connected through an interconnection network. This enables communication via shared memory or message passing methods. Multiprocessors offer increased speed and cost-effectiveness compared to single-processor systems

3 views • 24 slides

Understanding Processor Speculation and Optimization

Dive into the world of processor speculation techniques and optimizations, including compiler and hardware support for speculative execution. Explore how speculation can enhance performance by guessing instruction outcomes and rolling back if needed. Learn about static and dynamic speculation, handl

0 views • 33 slides

Understanding Pipelined Control in Processor Architecture

Explore the intricacies of pipelined control in processor design, detailing the control signals required at each stage of the pipeline. Learn about data hazards, forwarding, and stalling techniques to ensure efficient instruction execution. Dive into the concept of optimized control values for strea

0 views • 16 slides

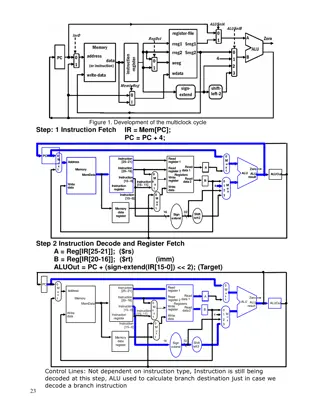

Development of Multiclock Cycle in Processor

The development process of the multiclock cycle in a processor is explained in detail through different steps, including instruction fetch, decode, register fetch, execution, and write-back for R-type instructions. Control lines and branching execution are also covered in the description. The conten

0 views • 5 slides

Overview of Inter-Processor Communication (IPC) in Processor Communication Link

Overview of Inter-Processor Communication (IPC) entails communication between processors, synchronization methods, and supported device types. The IPC architecture supports diverse use cases with various thread combinations and messaging types, catering to multi- or uni-processor environments. The A

0 views • 110 slides

Development of GR740 Single Board Computer Reference Design by RUAG Space and Partners

RUAG Space collaborates with Gaisler and other partners in the development of a GR740-based single board computer reference design funded by ESA. The project aims to create an advanced technology platform for future space projects, leveraging RUAG's expertise in electronics and digital computers for

0 views • 12 slides

Understanding Processor Hazards and Pipeline Stalls

Explore processor hazards like load-use and data hazards, along with strategies to avoid stalls in the pipeline. Discover how to detect and handle hazards efficiently for optimal performance in computer architecture. Learn about forwarding conditions, datapath design, and the impact of hazards on in

0 views • 30 slides

Out-of-Order Processor Design Exploration

Explore the design of an Out-of-Order (OOO) processor with an architectural register file, aggressive speculation, and efficient replay mechanisms. Understand the changes to renaming, dispatch, wakeup, bypassing, register writes, and commit stages. Compare Processor Register File (PRF) based design

0 views • 29 slides

Enhancing Processor Performance Through Rollback-Free Value Prediction

Mitigating memory and bandwidth walls, this research extends rollback-free value prediction to GPUs, achieving up to 2x improvement in energy and performance while maintaining 10% quality degradation. Utilizing microarchitecturally-triggered approximation to predict missed loads, this work focuses o

0 views • 7 slides

Understanding Processor Cycles and Machine Cycles in 8085 Microprocessor

Processor cycles in microprocessors like 8085 involve executing instructions through machine cycles that are essential operations performed by the processor. In the 8085 microprocessor, there are seven basic machine cycles, each serving a specific purpose such as fetching opcodes, reading from memor

0 views • 17 slides

IPC Lab 2 MessageQ Client/Server Example

This MessageQ example demonstrates the client/server pattern using SYS/BIOS heap for message pool, anonymous message queue, and return address implementation. The example involves two processors - HOST and DSP, where the DSP processor acts as the server creating a named message queue, and the HOST p

0 views • 12 slides

MIPAR Medical Image Processor & Repository Implementation Overview

Explore the MIPAR Medical Image Processor and Repository project by Olabanjo Olusola from Lagos State University. Learn about software skills requirements, the benefits of using PHP, uploading and downloading from the Open Access Repository (OAR), and more. Discover why PHP is a preferred choice for

0 views • 21 slides

Comparison Study Between ExoMars and Sample Fetch Rover Visual Localization Algorithms

Two space projects, ExoMars and Sample Fetch Rover, are compared based on their Visual Localization algorithms. The study focuses on the timing performance, ease of use, and consistency with previous results of the GR740 processor. Visual Odometry and challenges like motion blur and lighting differe

0 views • 16 slides

Understanding Processor Organization in Computer Architecture

Processor organization involves key tasks such as fetching instructions, interpreting instructions, processing data, and storing temporary data. The CPU consists of components like the ALU, control unit, and registers. Register organization plays a crucial role in optimizing memory usage and control

0 views • 21 slides

Understanding Processor Structure and Function in Computing

Explore the key components and functions of processors in computing, including user-visible and control status registers, instruction cycle, instruction pipelining, processor tasks like data processing and instruction interpretation, and the roles of arithmetic and logic units and control units. Lea

0 views • 61 slides

Understanding Processor Generations and VM Sizing for Azure Migration

Exploring the impact of processor generations on CPU performance, factors like clock speed, instruction set, and cache size are crucial. Choosing the right-sized VM plays a vital role in optimizing Azure migration. Passmark CPU Benchmark results provide insights on Intel processor generations for Az

0 views • 9 slides

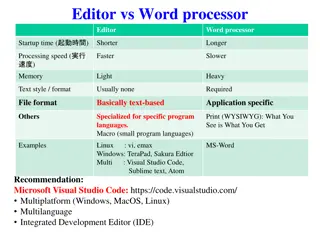

Comparison Between Text Editor and Word Processor

In this comparison, the differences between a text editor and a word processor are highlighted in terms of startup time, processing speed, memory usage, text style/format, file format, and application specificity. Both general and specialized examples are given with guidance on installing Visual Stu

0 views • 18 slides

Understanding Context Switching and User-Kernel Interaction in Operating Systems

Context switching in operating systems involves a seamless transition between user-level threads without the kernel's awareness. User-level code manages register state and stack pointers, while user-kernel mode switching requires changing processor privilege levels and agreement on information excha

0 views • 25 slides