National Food Processing Policy and Its Importance

National Food Processing Policy aims to address the significant wastage in food production through value addition and efficient processing. The policy highlights the reasons for food processing, including reducing losses in the supply chain and enhancing quality. It emphasizes creating an enabling e

1 views • 19 slides

Network Function Abstraction A delicate question of (CPU) affinity?

Exploring the delicate balance of CPU affinity in network function abstraction, including challenges, benefits, and solutions like CPU pinning for network workloads. Learn about the impact on performance and scalability, as well as the importance of proper configuration in virtual and physical envir

3 views • 40 slides

Introduction to Spark Streaming for Large-Scale Stream Processing

Spark Streaming, developed at UC Berkeley, extends the capabilities of Apache Spark for large-scale, near-real-time stream processing. With the ability to scale to hundreds of nodes and achieve low latencies, Spark Streaming offers efficient and fault-tolerant stateful stream processing through a si

0 views • 30 slides

Computer Architecture: CPU Structure and Function

Delve into the intricate world of computer architecture with Prof. Dr. Nizamettin AYDIN as your guide. Explore topics such as CPU structure, registers, instruction cycles, data flow, pipelining, and handling conditional branches. Gain insights into the responsibilities of a CPU, internal structures,

0 views • 39 slides

MIPS CPU Design Using Verilog and Instruction Set Architecture Overview

Explore the world of MIPS CPU design using Verilog with a deep dive into Instruction Set Architecture (ISA), SPIM instruction formats, addressing modes, and more. Learn about the key components such as Program Counter (PC), Instruction Memory (IM), Register Files (RF), Arithmetic Logic Unit (ALU), D

1 views • 29 slides

Opportunities in Ethiopia's Agro-Processing Industry

Ethiopia stands out as a leader in raw material production for agro-processing industries, offering opportunities in dairy, juice processing, edible oil processing, poultry, beef production, and tomato processing. With abundant resources, suitable climate conditions, and a growing domestic market, E

2 views • 8 slides

Significance of Raw Materials in Food Processing

Effective selection of raw materials is crucial for ensuring the quality of processed food products. The quality of raw materials directly impacts the final products, making it important to procure materials that align closely with processing requirements. Quality evaluation, including microbiologic

2 views • 30 slides

Anatomy of a Computer System: Hardware Components and Functions

A typical computer system consists of hardware and software working together to perform various computational tasks. The hardware components include the central processing unit (CPU), input/output devices, storage units, and the motherboard. The CPU acts as the main brain of the computer, performing

7 views • 6 slides

Computer Processing Systems

Computer processing systems consist of various components such as the control unit, ALU, input unit, CPU, output unit, memory, and more. Input devices feed raw data to the computer, while output devices provide processed information. The CPU plays a crucial role in executing instructions and data pr

0 views • 13 slides

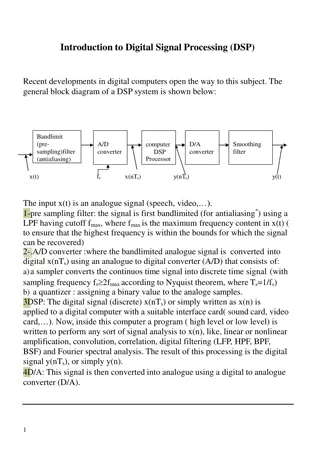

Overview of Digital Signal Processing (DSP) Systems and Implementations

Recent advancements in digital computers have paved the way for Digital Signal Processing (DSP). The DSP system involves bandlimiting, A/D conversion, DSP processing, D/A conversion, and smoothing filtering. This system enables the conversion of analog signals to digital, processing using digital co

1 views • 24 slides

Hardware-Assisted Virtualization: VT-x Overview and Implementation

Explore the key concepts of hardware-assisted virtualization using Intel VT-x technology for CPU virtualization, VMX transitions, and VM control structures. Understand the motivation behind VT-x, CPU virtualization techniques, and the benefits of VT-x in simplifying VMM software. Dive into VMX opera

2 views • 28 slides

CPU Scheduling in Operating Systems

In a single-processor system, processes take turns running on the CPU. The goal of multiprogramming is to keep the CPU busy at all times. CPU scheduling relies on the alternating CPU and I/O burst cycles of processes. The CPU scheduler selects processes from the ready queue to execute when the CPU i

1 views • 26 slides

Advancements in Signal Processing for ProtoDUNE Experiment

The team, including Xin Qian, Chao Zhang, and Brett Viren from BNL, leverages past experience in MicroBooNE to outline a comprehensive work plan for signal processing in ProtoDUNE. Their focus includes managing excess noise, addressing non-functional channels, and evolving signal processing techniqu

1 views • 23 slides

Sampling and Signal Processing Fundamentals

Sampling plays a crucial role in converting continuous-time signals into discrete-time signals for processing. This lecture covers periodic sampling, ideal sampling, Fourier transforms, Nyquist-Shannon sampling, and the processing of band-limited signals. It delves into the relationship between peri

1 views • 60 slides

Enhancing Near-Data Processing with Active Routing

Explore the implementation and benefits of Active-Routing for efficient data processing in memory networks. Motivated by the increasing demands for memory in graph processing and deep learning, this approach aims to reduce data movement, energy consumption, and costs associated with processing large

0 views • 46 slides

Overview of RNMRTK Software for NMR Data Processing

Rowland NMR Toolkit (RNMRTK) is a comprehensive software platform primarily used for NMR data processing tasks such as running MaxEnt, apodization, DFT processing, linear prediction, and more. It offers a robust set of tools for various processing needs and supports efficient parallel processing. RN

0 views • 17 slides

Transaction Processing Systems (TPS)

Transaction Processing Systems (TPS) are vital components in capturing, storing, and processing data generated from various business transactions. They ensure efficient handling of high volumes of data while maintaining accuracy, security, and privacy. TPS operate through automated data entry, batch

0 views • 24 slides

Centre of Excellence in Signal Processing Activities and Progress Report

Broad areas of signal processing activities at the Centre of Excellence in Signal Processing include audio, speech, language, medical image processing, computer vision, wireless communications, and machine learning. The center focuses on addressing various challenges in audio/speech recognition, emo

0 views • 17 slides

Energy-Efficient Query Processing on Embedded CPU-GPU Architectures

This study explores the energy efficiency of query processing on embedded CPU-GPU architectures, focusing on the utilization of embedded GPUs and the potential for co-processing with CPUs. The research evaluates the performance and power consumption of different processing approaches, considering th

0 views • 22 slides

Edge Computing for Optimizing Internet Devices

Edge computing brings computing closer to the data source, minimizing communication distances between client and server for reduced latency and bandwidth usage. Distributed in device nodes, edge computing optimizes processing in smart devices instead of centralized cloud environments, enhancing data

0 views • 32 slides

Multi-Processing in Computer Architecture

Beginning in the mid-2000s, a shift towards multi-processing emerged due to limitations in uniprocessor performance gains. This led to the development of multiprocessors like multicore systems, enabling enhanced performance through parallel processing. The taxonomy of Flynn categories, including SIS

0 views • 46 slides

Insight into PEPS Data Processing Architecture by Erwann Poupard

Erwann Poupard, a Software Ground System Engineer at CNES, Toulouse, France, plays a crucial role in the PEPS data processing architecture. The outline covers PEPS HPSS data storage statistics, current data processing trends, and future plans including PEPS V2 development. Explore PEPS processing ch

0 views • 8 slides

CPU Structure and Function in Computer Organization and Architecture

Exploring the intricate details of CPU architecture, this content delves into the essential tasks of fetching, interpreting, processing, and writing data. It discusses the significance of registers, user-visible registers, general-purpose registers, and condition code registers in CPU operations. Ad

0 views • 83 slides

CPU Architecture in Computing for GCSE Students

Explore the fundamental concepts of CPU architecture, including the Von Neumann Architecture, common CPU components like ALU and CU, and how characteristics such as Clock Speed and Cache Size impact performance. Learn about the Fetch-Execute Cycle and the essential hardware components of a computer

0 views • 18 slides

Intel CPU Architectures Overview: Evolution and Features

Explore the evolution and key features of various Intel CPU architectures including Pentium, Core, and Pentium 4 series. Learn about the pipeline stages, instruction issue capabilities, branch prediction mechanisms, cache designs, and memory speculation techniques employed in these processors. Gain

0 views • 11 slides

The Basics of Multi-Stage Architecture in CPU Design

The article explains the fundamentals of a multi-stage digital processing system in computer organization, focusing on the central processing unit (CPU). It covers topics such as instruction execution, processor building blocks, and the benefits of pipelined operation. Concepts like fetching, decodi

0 views • 42 slides

Data Processing and Preprocessing Summary

In this document, Aymeric Sauvageon from CEA/DRF/Irfu/DAp presents a detailed overview of the preprocessing steps involved in data processing from L0 to L1. It covers the definition of L0/L1 and coding, utilization of the database for processing, input file specifications from China, packet content

0 views • 11 slides

Operating System Concepts: Multiprogramming, Multiprocessing, Multitasking, and Multithreading

In the realm of operating systems, terms like multiprogramming, multiprocessing, multitasking, and multithreading can often be confusing due to their similar appearance but distinct meanings. These concepts play a crucial role in efficiently managing resources in a computing system, particularly in

0 views • 6 slides

CPU Scheduling Concepts at Eshan College of Engineering, Mathura

Dive into the world of CPU scheduling at Eshan College of Engineering in Mathura with Associate Professor Vyom Kulshreshtha. Explore topics such as CPU utilization, I/O burst cycles, CPU burst distribution, and more. Learn about the CPU scheduler, dispatcher module, scheduling criteria, and the impl

0 views • 18 slides

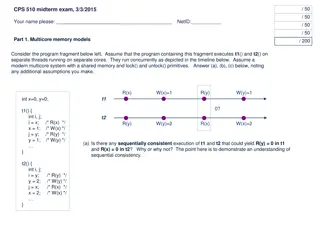

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Barrel Shifter in CPU Design

Barrel shifter is a vital component in CPU architecture, enabling shifting and rotating operations on data inputs based on control signals. The shifter consists of two main blocks - Shift-and-Rotate Array (SARA) and Control Logic. SARA, designed with multiple stages of cells, executes shift and rota

0 views • 12 slides

CPU Virtualization and Execution Control in Operating Systems

Explore the concepts of CPU virtualization, direct execution, and control mechanisms in operating systems illustrated through a series of descriptive images. Learn about efficient CPU virtualization techniques, managing restricted operations, system calls, and a limited direct execution protocol for

0 views • 18 slides

Enhancing gem5's GPUFS Support for Improved Simulation Speed

Addressing challenges in application scaling, this project focuses on enhancing gem5's GPUFS support to improve simulation speed by functionally simulating memory copies and adding KVM CPU-GPU support. The introduction covers prior CPU-GPU support in gem5, ML support, and the introduction of GPUFS s

0 views • 19 slides

Illustrated Design of a Simplified CPU with 16-bit RAM

Demonstrates the design of a basic CPU with 11 instructions and 4096 16-bit RAM, showcasing the assembly of a general-purpose computer using gates and registers. The CPU comprises 8 key registers for various functions, employing a sequential circuit for instruction execution. The machine language pr

0 views • 31 slides

Orleans Streaming Orleans Streaming

In this content, Orleans Streaming and real-life scenarios are discussed, highlighting the flexibility of stream processing logic, support for dynamic topologies, and fine-grained stream granularity. The content explores scenarios such as actor calls, IoT device event processing, chat room events, a

0 views • 17 slides

Introduction to Processing - The Basics

Processing, initiated by Ben Fry and Casey Reas at MIT Media Lab in 2001, is a Java-based platform designed for visual artists. It simplifies complex Java syntax for creating art. Processing incorporates numerous libraries for various purposes such as computer vision, data visualization, music compo

0 views • 32 slides

Understanding a Modern Processing in-Memory Architecture

Data movement between memory/storage units and compute units significantly impacts execution time and energy consumption. Processing-in-Memory (PIM) offers a promising solution to address this bottleneck. This paper discusses the challenges and advancements in PIM architecture, focusing on UPMEM's i

0 views • 10 slides

Understanding Von Neuman CPU Circuitry

A central processing unit (CPU) is a vital part of a computer, executing instructions for arithmetic, logic, control, and I/O operations. This article delves into the components of a CPU, such as the Arithmetic Logic Unit (ALU) and Control Unit (CU), outlining their functions and importance in compu

0 views • 8 slides

Computing Fundamentals

The personal computer system consists of hardware and software components. Hardware includes the physical equipment such as the CPU, monitor, and printer. Software comprises coded instructions for the computer to execute tasks. The key hardware components are the CPU, I/O devices, RAM, and storage d

0 views • 16 slides

CPU and Von Neumann Architecture

This unit delves into the fundamental concepts of CPU functionality and the Von Neumann architecture, exploring the purpose of the CPU, common components like registers, and factors influencing CPU speed. Understand how the CPU decodes instructions, performs calculations, and utilizes memory efficie

0 views • 4 slides