Implementation of a 42-PS TDC Based on FPGA Target

Context: Time-to-Digital Converter (TDC) architecture, methodology, and realization for high-throughput time-correlated single-photon counting in microfluidic droplets. Fluorescence Lifetime (FL) measurements offer high system sensitivity and accuracy. TDC specification for FPGA target with temporal resolution lower than 100 ps. Definition of TDC, working principle with fine and coarse counters, architecture involving tapped delay line and ringed oscillator, and methodology including control logic and data communication via USB.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

IMPLEMENTATION OF A 42 PS TDC BASED ON FPGA TARGET Speaker Contributors : : Timoth Turko * Mcf. Foudil Dadouche * Pr. Wilfried Uhring * Dr. Imane Malass * J r my Bartringer * Mcf. Jean-Pierre Le Normand 2016 ICube

SUMMARY Context Time to Digital Converter Architecture Methodology and realization Encountered problems and solutions Fast Time to Digital Converter characterization 2

CONTEXT High-throughput time-correlated single photon counting in microfluidic droplets for enzymatic activity assays Why Fluorescence Lifetime (FL) measurements instead of Fluorescence Intensity measurements? Due to the intrinsic character of FL studies, there are no interferences arising from volume differences, concentration, sample geometry or laser power, leading to high system sensitivity, accuracy and low noise level (Poisson noise). 3

CONTEXT Time to Digital Converter (TDC) specification : FPGA target (Cyclone IV) Temporal resolution lower than 100 ps 4

DEFINITION Electronic instrumentation Signal processing Time to Digital Converter Absolute time Digital (Binary) Output Events recognition providing a digital representation of the time 5

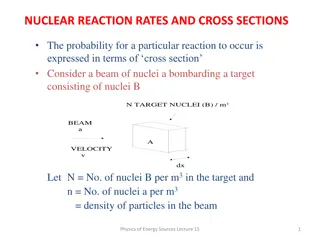

HOW DOES IT WORKS ? Two Fine counters One Coarse counter Tm = TFine1+ TCoarse TFine2 6

ARCHITECTURE Tapped Delay Line Ringed Oscillator Maximum resolution : 10 ps Maximum resolution : 10 ps The resolution is imposed by the FPGA s technological limits and not by the TDC s architecture 7

METHODOLOGY AND REALIZATION One associated control logic fine counter and One coarse counter and associated control logic One Encoder to convert the TDC results on 8 bits A data communication tool : USB 8

FIRST APPROACH Logical simplification ! It is necessary to constrain the logical elements placement 9

IMPLEMENTED SOLUTION New objectives: Avoid the software data path simplification Increase TDC resolution by reducing the propagation time through delay elements Automate the elementary cells set-up process to optimize the design time and make possible the development of generic and adaptable structures This method is focused on two main areas: Using adders as delay elements and utilization of the Carry Chain Logic of the FPGA Using the Chip Planner tool 10

CARRY CHAIN Positionning failure of logical elements Achieve a minimum propagation delay Spacial constrain of logical elements positions mandatory is 11

TDC CHARACTERIZATION Using a delay generator: Start The measurement last a long time Delay Generator FPGA Allows to measure the jitter Stop Start signal Delay generator trigger Stop signal Start signal delayed 12

TDC CHARACTERIZATION 200 INL (ps) 0 -200 0 2 4 6 8 10 12 14 16 4 Time (ps) Resolution : 42 ps x 10 200 Jitter : 90 ps RMS DNL (ps) 0 -200 INL : 132 ps RMS 0 2 4 6 8 10 12 14 16 4 Time (ps) x 10 DNL : 50 ps RMS 13

TDC CHARACTERIZATION Replacement of the FPGA s native DC/DC converter by a less noisy one. Resolution : 42 ps Jitter : 26 ps RMS INL : 22 ps RMS DNL : 13 ps RMS 14

RESULTS : FINE TDC Resolution : 42 ps Jitter : 26 ps RMS INL : 22 ps RMS DNL : 13 ps RMS Dead Time : 20 ns 15

TDC CHARACTERIZATION Using Poisson process events: Statistically each TDC bins should go through the same number of event Light source + SPAD = Random events generator STOP Photon START SPAD Can not measure the Jitter FPGA Start and Stop signals are not dependent. The delay between both of them is totally random Very fast and accurate measurement 16

TDC CHARACTERIZATION Where : T is the total time range M is the number of bins in the time range T 18

CASE STUDY Before correction Visible static pattern Lifetime : 4.21 ns 0.08 ns After correction Static pattern clearly attenuated Lifetime : 4.19 ns 0.02 ns 20

Conclusion Reached resolution : 42 ps Jitter lower than 1 LSB Fast and accurate characterization Possibility to correct the transfer function 21