Overview of Front-End DAQ for TREND

Cutting-edge Front-End DAQ system featuring components like the Texas Instruments ADS6424 ADC, ALTERA 5CEFA4F23C6N FPGA, Ring Buffer for data management, u-blox Precision Timing GPS module for accurate time stamping, and General Slow Control Architecture for monitoring. The system utilizes Ethernet UDP Protocol for high-speed data transmission and follows a structured block format for message handling. Expect exceptional performance in data acquisition based on the outlined specifications.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. Download presentation by click this link. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

E N D

Presentation Transcript

Introduction 2 25/09/2024

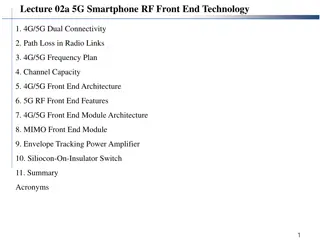

The ADC 3-100MHz x 12-bit ADC Serial LVDS output interface Texas Instruments ADS6424 (Quad Channel) 3 25/09/2024

The FPGA ALTERA 5CEFA4F23C6N BGA technology 484-pin 48K Logic Elements 3 Mega bits Low cost 4 25/09/2024

The Ring Buffer 100MHz Write 100MHz Read Simultaneous R/W operations Allows to read a ROI around the trigger time (4 s 400 cells) Dead time during reading operation, but no data lost (will be in the buffer anyway). ADC Deserializer Ring Buffer FPGA 5 25/09/2024

Time Stamping Based on u-blox Precision Timing GPS module Up to 15 ns accuracy Provide 1PPS synchronously in all the boards A TDC (embedded in the FPGA) measures the time between the 1PPS and the Trigger pulse Cheap 6 25/09/2024

General Slow Control Architecture EPROM DS2502 MAC Address generator DAC AD5328 Comparators thresholds FPGA Temp. TC77 Temperature Sensor ADC 128S102 Voltages monitoring 7 25/09/2024

Ethernet UDP Protocol 1Gb/s transfert rate. Data transmission as the bottleneck, unit trig rate up to several MHz should be OK. Optical fibers transmission down to central DAQ. 8 25/09/2024

General Block Structure The incoming and outgoing data are encapsulated into a block structure Message TRENDDAQ TRENDTRIG TRENDSLCREQ TRENDGPS TRENDINTREG TRENDDATA TRENDSLC TRENDRDINTREG Direction incoming incoming incoming incoming incoming outgoing outgoing outgoing HEADER HEADER MSGTYPE MSGTYPE DATA IP ADDRESS IP ADDRESS DATA . . TRAILER TRAILER Incoming Messages Outgoing Messages TRENDACK outgoing 9 25/09/2024

Expected DAQ performances 10 25/09/2024

DAQ response simulation Simulated signal @ LNA output +noise (TREND50): expected signal @ LNA output Simulated analog stage response (National Instruments MultiSim)

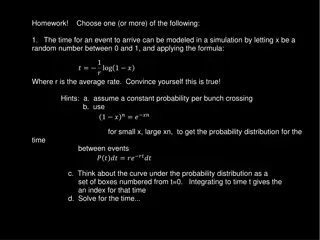

Digitization 60MHz 100MHz 1GHz

Signal amplitude (@ 100MHz) PD log response. Fit y=P1+P2*log(x) PD log response inversion: y=exp[ (PDOut-P1) /P2 ] Spread around linear response: standard deviation <6%.

Timing precision Analytical computation of and assuming 6 antennas triggering & 15ns timing resolution. The different colors correspond to -20< <20 <2.5 <1

Conclusion Radio DAQ system features meet requests. Prototype being setup, to be tested on site before September 2015 If all goes well, production of 32 units completed before January 2015. GRAND radio array fully operational in a year from now (fingers crossed). 15 25/09/2024