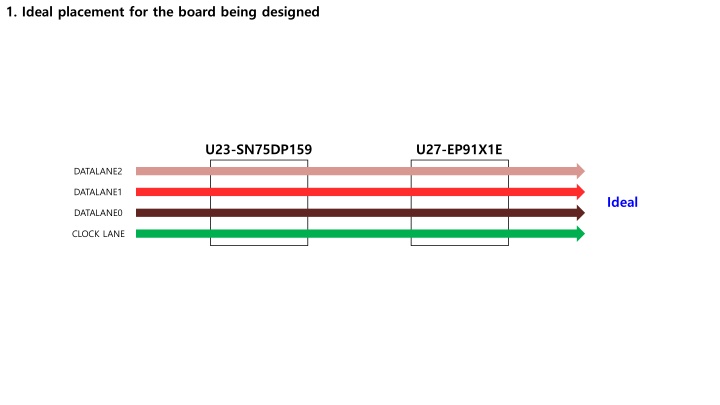

Ideal Placement for Board Design with U23-SN75DP159 and U27-EP91X1E

The current status of the board under design includes various components such as resistors, capacitors, and integrated circuits (ICs) like PLL_XFC-2. Connections for TMDS_D2P, TMDS_D2N, TMDS_D1P, TMDS_D1N, TMDS_D0P, TMDS_D0N, and TMDS_CLKP are detailed. Additionally, there are references to HDMI interfaces with HDMI_3V3, COMR-2, and more. The board layout is complex and involves detailed routing of lanes and clock signals.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

1. Ideal placement for the board being designed U23-SN75DP159 U27-EP91X1E DATALANE2 DATALANE1 Ideal DATALANE0 CLOCK LANE

2. Current status of the board under design CLOSE TO CHIP Schematic C280 C_102_50V_1005_X7R R196 R_2.2K_F_1608 PLL_XFC-2 C270 C_105_16V_1005_X5R COMR-2 SW_3V3 HDMI_3V3 SW_1V1 C278 C_105_16V_1005_X5R COMR-2 C_106_6.3V_1005_X5R C_106_6.3V_1005_X5R C_104_10V_1005_X5R C_103_10V_1005_X7R C_104_10V_1005_X5R C_104_10V_1005_X5R C_104_10V_1005_X5R C_104_10V_1005_X5R C_103_10V_1005_X7R C_103_10V_1005_X7R C_106_6.3V_1005_X5R C_106_6.3V_1005_X5R U7_T2_TX2+ U7_T2_TX2- TX2P-2 L35 L36 T2_TX2+ T2_TX2- TX2P-2 TX2M-2 R212 R221 R_20R_F_1005 R_20R_F_1005 C274 C_104_16V_1005_X7R R222 R198 R_499R_F_1005 R_499R_F_1005 TX2M-2 L_PBY201209T-121Y-N L_PBY201209T-121Y-N C283 C_104_16V_1005_X7R C237 C232 C238 C239 C240 C241 C233 C242 C243 C234 C235 C244 U7_T2_TX1+ TX1P-2 TX1M-2 T2_TX1+ T2_TX1- TX1P-2 R209 R206 R_20R_F_1005 R_20R_F_1005 C284 C272 C_104_16V_1005_X7R C_104_16V_1005_X7R R192 R199 R_499R_F_1005 R_499R_F_1005 U7_T2_TX1- TX1M-2 10nF U7_T2_TX0+ TX0P-2 TX0M-2 T2_TX0+ TX0P-2 TX0M-2 R202 R204 R_20R_F_1005 R_20R_F_1005 C275 C_104_16V_1005_X7R R203 R_499R_F_1005 U7_T2_TX0- T2_TX0- C279 C_104_16V_1005_X7R R210 R_499R_F_1005 U7_T2_TXC+ U7_T2_TXC- TXCP-2 T2_TXC+ TXCP-2 TXCM-2 R214 R218 R_20R_F_1005 R_20R_F_1005 C277 C_104_16V_1005_X7R R223 R_499R_F_1005 TXCM-2 T2_TXC- C276 C_104_16V_1005_X7R R211 R_499R_F_1005 C236 C_104_16V_1005_X7R PLL_XFC-2 [6] TMDS_D2P TX_RSEN-2 R197 R_10K_F_1005 R195 R_1M_F_1005 13 43 14 23 24 37 48 TX_HPD-2 R213 R_10K_F_1005 C282 C_105_16V_1005_X5R C245 C_104_16V_1005_X7R U23 [6] TMDS_D2N R194 R_0R_J_1005 2021.12.01 (Artwork ) MET off page VCC_13 VCC_43 VDD_14 VDD_23 VDD_24 VDD_37 VDD_48 TX_RSEN-2 2 3 35 TMDS_D2P-1 VDD-2 SDI_TMDS_OUT_D2P IN_D2p IN_D2n OUT_D2p [9] R219 DNS_R_0R_J_1005 34 TMDS_D2N-1 C246 C_104_16V_1005_X7R TX_PVDD-2 EPMCU_RSTb-2 C_105_16V_1005_X5R [6] TMDS_D1P SDI_TMDS_OUT_D2N [9] R201 R_10K_F_1005 OUT_D2n TX_AVDD-2 VDDE-2 5 6 32 TMDS_D1P-1 C247 C_104_16V_1005_X7R [6] TMDS_D1N SDI_TMDS_OUT_D1P IN_D1p IN_D1n OUT_D1p [9] C273 31 SDI_TMDS_5V TMDS_D1N-1 SDI_TMDS_OUT_D1N [9] OUT_D1n 42 41 40 39 38 37 36 35 34 33 32 31 30 29 U27 8 9 29 TMDS_D0P-1 C248 C_104_16V_1005_X7R [6] TMDS_D0P SDI_TMDS_OUT_D0P IN_D0p IN_D0n OUT_D0p [9] 28 TMDS_D0N-1 TX0- TXC- PLL_XFC TIM[0] MCU_RSTb VDD12 MCU_P02 MCU_P01 TX0+ TX_AVDD TXC+ TX_PVDD TX_AVSSE TX_AVSSE SDI_TMDS_OUT_D0N [9] OUT_D0n C249 C_104_16V_1005_X7R [6] TMDS_D0N 11 12 26 25 TMDS_CLKP-1 TMDS_CLKN-1 R147 R148 R_2K_J_1005 SDI_TMDS_OUT_CLKP [9] SDI_TMDS_OUT_CLKN [9] IN_CLKp IN_CLKn OUT_CLKp OUT_CLKn R_2K_J_1005 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 28 27 26 25 24 23 22 21 20 19 EPMCU_OP0-2 EPMCU_TXD-2 EPMCU_RXD-2 LED_CEC-2 R220 R_1K_J_1005 C250 C_104_16V_1005_X7R TX1- TX1+ TX_AVDD TX2- TX2+ TX_AVSSE COMR RX_HPD VDDE VSS TX_SDA RX_SDA RX_VDD RX_VSS E_PAD MCU_OP0 MCU_P71 MCU_P70 MCU_P31_P41 MCU_P36 MCU_P35 MCU_P34 MCU_VDDE MCU_XOUT MCU_XIN [6] TMDS_CLKP R208 R191 R_10K_F_1005 R_10K_F_1005 4 33 SRC_HPD R149 R_1K_J_1005 R_0R_J_1005 R_0R_J_1005 [9] SDI_HPD HPD_SRC HPD_SNK VDDE-2 TX_AVDD-2 C251 C_104_16V_1005_X7R U_SN75DP159 R215 DNS_R_0R_J_1005 [6] TMDS_CLKN 47 39 R150 R151 H5V_IN-2 R_2K_J_1005 R_2K_J_1005 SRC_DDC_SDA SDA_SRC SDA_SNK [9] 46 38 MCU_SDA-2 R205 R207 U_EP91X1E SRC_DDC_SCL SCL_SRC SCL_SNK [9] HDMI_3V3 MCU_SCL-2 COMR-2 VDDE-2 45 1 10 20 21 HDMI_3V3 RX_HPD-2 VDDE-2 AUX_SRCp SWAP/POL I2C_EN/PIN PRE_SEL EQ_SEL/A0 44 Xout-2 C271 C_200_50V_1005_NPO VDDE-2 AUX_SRCn R216 R_1M_J_1005 3 18 TX_SDA-2 R193 R_0R_J_1005 16 R_0R_J_1005 DNS_R_0R_J_1005 R155 R157 VDD-2 VDD12 17 16 2 4 [6, 7] SDA_CTL rxSDA-IC-2 Xout-2 SDA_CTL Y3 Y_JYD3A1G3D8-18-24.000 15 27 36 40 XIN rxSCL-IC-2 TX_SCL-2 [6, 7] SCL_CTL SCL_CTL HDMI_SELb/A1 TX_TERM_CTL SLEW_CTL VDD-2 RX_SCL 15 R200 R_0R_J_1005 42 C_224_6.3V_1005_X5R 1 RX_AVDD33 TX_SCL C281 C_200_50V_1005_NPO RX_PAVDD OE 22 HDMI_3V3 RX_AVDD RX_AVDD RX_AVDD R163 R_6.98K_F_1005 EXT_RES VSADJ C252 RXC+ RX0+ RX1+ RX2+ RXC- RX0- RX1- RX2- 18 R164 R167 DNS_R_10K_J_1005 DNS_R_10K_J_1005 GND_19 GND_30 GND_41 GND_7 CEC_EN 17 NC_17 TAB 1 2 3 4 5 6 7 8 9 10 11 12 13 14 Default I2C Address: [A1:A0] = 0x1 0x5D (7 address bits) 7 19 30 41 49 R217 R_510R_F_1005 RX_AVDD33-2 RX_AVDD-2 [8] [8] SDI_TMDS_OUT_CLKN SDI_TMDS_OUT_CLKP RX_AVDD33-2 [8] [8] [8] SDI_TMDS_OUT_D0N SDI_TMDS_OUT_D0P SDI_TMDS_OUT_D1N [8] SDI_TMDS_OUT_D1P [8] [8] SDI_TMDS_OUT_D2N SDI_TMDS_OUT_D2P rxSDA-IC-2 R_0R_J_1005 R226 [8] SRC_DDC_SDA rxSCL-IC-2 U23-SN75DP159 U27-EP91X1E 35 SDI_TMDS_OUT_D2P 34 SDI_TMDS_OUT_D2N 35 SDI_TMDS_OUT_CLKN 34 SDI_TMDS_OUT_CLKP 32 SDI_TMDS_OUT_D1P 31 SDI_TMDS_OUT_D1N Artwork 32 SDI_TMDS_OUT_D0N 31 SDI_TMDS_OUT_D0P 29 SDI_TMDS_OUT_D0P 28 SDI_TMDS_OUT_D0N 29 SDI_TMDS_OUT_D1N 28 SDI_TMDS_OUT_D1P 26 SDI_TMDS_OUT_CLKP 25 SDI_TMDS_OUT_CLKN 26 SDI_TMDS_OUT_D2N 25 SDI_TMDS_OUT_D2P

3. SN75DP159 lane & polarity swap function 3-1) Ideal Situation 3-2) Current situation U13 U23 U27 U13 U23 U27 OUT => IN OUT => IN OUT => IN OUT => IN D2P D2N -> -> D2P D2N D2P D2N -> -> D2P D2N D2P D2N -> -> D2P D2N D2P D2N -> X -> X CLKN CLKP D1P D1N -> -> D1P D1N D1P D1N -> -> D1P D1N D1P D1N -> -> D1P D1N D1P D1N -> X -> X D0N D0P D0P D0N -> -> D0P D0N D0P D0N -> -> D0P D0N D0P D0N -> -> D0P D0N D0P D0N -> X -> X D1N D1P CLKP CLKN -> -> CLKP CLKN CLKP CLKN -> -> CLKP CLKN CLKP CLKN -> -> CLKP CLKN CLKP CLKN -> X -> X D2N D2P

3. SN75DP159 lane & polarity swap function 3-3) Using SN75DP159, lane swap 3-4) at 3-3) Condition, polarity swap U13 U23 U27 U13 U23 U27 OUT => IN OUT => IN OUT => IN OUT => IN D2P D2N -> -> D2P D2N CLKP CLKN -> -> CLKN CLKP D2P D2N -> -> D2P D2N CLKN CLKP -> -> CLKN CLKP D1P D1N -> -> D1P D1N D0P D0N -> -> D0N D0P D1P D1N -> -> D1P D1N D0N D0P -> -> D0N D0P D0P D0N -> -> D0P D0N D1P D1N -> -> D1N D1P D0P D0N -> -> D0P D0N D1N D1P -> -> D1N D1P CLKP CLKN -> -> CLKP CLKN D2P D2N -> -> D2N D2P CLKP CLKN -> -> CLKP CLKN D2N D2P -> -> D2N D2P Please check if the 3-4) condition can be applicable

3. SN75DP159 lane & polarity swap function SN75DP159 Datasheet

3. SN75DP159 lane & polarity swap function 3-5) Based on the datasheet, forecast the lane & polarity swap function U13 U23 U27 OUT => IN OUT => IN CLKN CLKP -> -> CLKN CLKP D2P(fixed)-> X D2N(fixed)-> X CLKN CLKP D0N D0P -> -> D0N D0P D1P(fixed)-> X D1N(fixed)-> X D0N D0P D1N D1P -> -> D1N D1P D0P(fixed)-> X D0N(fixed)-> X D1N D1P CLKP CLKN -> -> D2N D2P CLKP(fixed)-> X CLKN(fixed)-> X D2N D2P

4. Additional question Regarding the RDK(third-party offered) board being reviewed by KORTEK, They commented on the TI s SN75DP159 function like below, and we also confirmed that function.(red box) We would like to ask TI to confirm whether there are any other customers asking the same opinion as ours and whether this IC function is correct.