Computer Components and Microprocessor: Understanding Computer Architecture

Explore the main computer components and learn about the operation of these components, including inputting, storing, processing, outputting, and controlling. Understand the role of the microprocessor in computer processing and its characteristics such as instruction set, bandwidth, and clock speed.

11 views • 20 slides

Towards Single-Event Upset Detection in Hardware Secure RISC-V Processors

This research focuses on detecting single-event upsets (SEUs) in hardware-secure RISC-V processors in radiation environments, such as high-energy physics and space applications. Motivated by the potential data errors, unpredictable behavior, or crashes caused by SEUs, the study explores fault inject

4 views • 17 slides

Understanding Microprocessor Architecture and Software Design

Microprocessor architecture and software design play crucial roles in the development of microprocessors. This article explores the internal features, software design types, and characteristics of Complex Instruction Set Computer (CISC) and Reduce Instruction Set Computer (RISC) architectures. It de

7 views • 73 slides

Evolution of IBM System/360 Architecture and Instruction Set Architectures

The IBM System/360 (S/360) mainframe computer system family, introduced in 1964, revolutionized computing by offering forward and backward compatibility, a unified instruction set architecture (ISA), and a balance between scientific and business efficiency. The critical elements of this architecture

1 views • 18 slides

Understanding Computer Architecture: A Comprehensive Overview by Prof. Dr. Nizamettin AYDIN

Explore the realm of computer architecture through the expertise of Prof. Dr. Nizamettin AYDIN, covering topics like RISC characteristics, major advances in computers, comparison of processors, and the driving force for CISC. Delve into the evolution of processors, register optimization, and the tra

0 views • 42 slides

MIPS CPU Design Using Verilog and Instruction Set Architecture Overview

Explore the world of MIPS CPU design using Verilog with a deep dive into Instruction Set Architecture (ISA), SPIM instruction formats, addressing modes, and more. Learn about the key components such as Program Counter (PC), Instruction Memory (IM), Register Files (RF), Arithmetic Logic Unit (ALU), D

1 views • 29 slides

PowerPC Architecture Overview and Evolution

PowerPC is a RISC instruction set architecture developed by IBM in collaboration with Apple and Motorola in the early 1990s. It is based on IBM's POWER architecture, offering both 32-bit and 64-bit processors popular in embedded systems. The architecture emphasizes a reduced set of pipelined instruc

2 views • 13 slides

Evolution of Computing Architectures: RISC Approach

Study on the RISC approach in computing architecture, focusing on key characteristics and advancements since the inception of stored-program computers. Topics covered include the family concept, microprogrammed control units, cache memory, pipelining, and the development of RISC architecture as an a

0 views • 58 slides

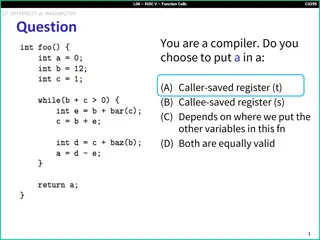

Understanding RISC-V Function Calls

In RISC-V function calls, the decision to place variables in caller-saved or callee-saved registers depends on various factors such as recursion and variable usage within the function. Additionally, understanding how function arguments are passed and stored is crucial for efficient program execution

0 views • 5 slides

Contrasting RISC and CISC Architectures

Contrasting RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing) architectures, the images and descriptions elaborate on their advantages and disadvantages, with a focus on multiplying two numbers in memory using a CISC approach. CISC processors aim to complete tasks

0 views • 35 slides

Understanding ARM RISC Design Philosophy and Its Impact

Delve into the world of ARM processors, exploring the RISC design philosophy that underpins their efficiency and widespread application. Learn about key principles, compare RISC with CISC, and discover how ARM's simplicity, orthogonality, and efficient architecture contribute to its dominance in mob

0 views • 12 slides

Understanding Parallelism and Vector Instructions in CMPT 295

Delve into the world of parallelism and vector instructions in CMPT 295 as you explore fixed-length vector intrinsics, RISC-V concepts, computer programming fundamentals, processor execution processes, scalar and vector loops, and more. Discover the intricacies of memory, data arrays, structs, integ

1 views • 45 slides

Understanding RISC, CISC, and ISA Variations in Computer Science

Explore the differences between RISC and CISC architectures, along with variations in Instruction Set Architecture (ISA). Dive into the intricacies of processor design, performance factors, and assembly languages. Get insights into the concepts of control units, memory units, pipelines, and datapath

0 views • 37 slides

Variations in Computer Architectures: RISC, CISC, and ISA Explained

Delve into the realm of computer architectures with a detailed exploration of Reduced Instruction Set Computing (RISC), Complex Instruction Set Computing (CISC), and Instruction Set Architecture (ISA) variations explained by Prof. Kavita Bala and Prof. Hakim Weatherspoon at Cornell University. Explo

0 views • 55 slides

Framework for Developing Verified Assemblers for ELF Format

This research paper discusses the importance of verified assemblers in the context of verified compilation, focusing on the development of verified assemblers for the ELF format for multiple architectures like X86, RISC-V, and ARM. The framework aims to be configurable, extensible, and general to su

0 views • 32 slides

Embedded Computer Architecture - Instruction Level Parallel Architectures Overview

This material provides an in-depth look into Instruction Level Parallel (ILP) architectures, covering topics such as hazards, out-of-order execution, branch prediction, and multiple issue architectures. It compares Single-Issue RISC with Superscalar and VLIW architectures, discussing their differenc

0 views • 49 slides

Fast TLB Simulation for RISC-V Systems - Research Overview

TLB simulator for RISC-V systems introduced to evaluate TLB designs with realistic workloads, focusing on performance rather than cycle accuracy. The design sacrifices some accuracy for improved performance, making it suitable for meaningful software validation and profiling tasks.

0 views • 29 slides

SunGuide Software Users Group Meeting Highlights January 26, 2023

Highlights from the SunGuide Software Users Group meeting on January 26, 2023, include discussions on RISC management, equipment behavior, enhancements, safe tow rotations, and predefined plans for FDLE alert types. Topics covered range from managing equipment in RISC events to allowing users to sel

0 views • 22 slides

Implementation of RISC-V in Protium: Overview and Analysis

RISC-V, a royalty-free open-source Instruction Set Architecture (ISA), has gained popularity since its inception in 2010. This article delves into the historical background, extensions, integer registers, and the Pulp platform's RISC-V cores. The implementation of RISC-V in Protium is discussed, pro

0 views • 13 slides

Understanding Memory Hierarchy and Different Computer Architecture Styles

Delve into the concepts of memory hierarchy, cache optimizations, RISC architecture, and other architecture styles in embedded computer architecture. Learn about Accumulator and Stack architectures, their characteristics, advantages, and example code implementations. Explore the differences between

0 views • 52 slides

Understanding Instruction Set Architectures (ISAs) in Computer Science

Explore the concepts of RISC, CISC, and ISA variations in computer architecture. Dive into the differences between MIPS, ARM, X86, and other ISAs, focusing on load/store, arithmetic, control flow, and more. Gain insights into the evolution and variations of ISAs, and discover the alternatives beyond

0 views • 37 slides