Implementation of RISC-V in Protium: Overview and Analysis

RISC-V, a royalty-free open-source Instruction Set Architecture (ISA), has gained popularity since its inception in 2010. This article delves into the historical background, extensions, integer registers, and the Pulp platform's RISC-V cores. The implementation of RISC-V in Protium is discussed, providing a comprehensive understanding of this innovative technology and its application in modern computing systems.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Outline Introduction RISC-V global overview Two different architectures Implementation in Protium Conclusion 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 2

Introduction What is RISC-V? It is a Instruction Set Architecture (ISA) It is based on established Reduced Instruction Set Computer (RISC) principle It is s provided under royalty-free open-source licenses When it has started? 18thMay 2010 First Silicon in 2011 (FDSOI 28nm from STM) RISC-V Foundation was formed in 2015 Based on computer architecture ideas that date back at least 40 years 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 3

Historical overview 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 4

Extensions Base ISA variant: 32, 64 or 128 bits address space The I extension is the only mandatory The E extension is a reduce set of I for embedded (16 registers instead of 32) Several RISC-V extension exist: Allows fitting the architecture to your needs Support of non-standard extension: Free portions of the encoding space are guarantee 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 5

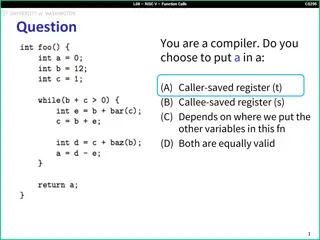

Integer registers Except in rv32e there is 32 integer registers The x0 is hard codded to 0 The other usage are by convention 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 6

Pulp platform Several RISC-V cores: 32 or 64 bits address space Different pipeline stages Complete systems Wide sort of peripherals SolderPad license Non-exclusive No-charge Royalty-free Irrevocable Support of Hardware Processing Engine Rich toolset 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 7

Pulpissimo Single-core platform Either the RI5CY core or the Ibex one Autonomous Input/Output subsystem (uDMA) Software Development Kit RISCY is a RV32IMC[F] with some specific extensions Ibex highly configurable core See lowRISC company for more details 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 8

PicoRV32 Goal: Auxiliary processor for FPGA/ASIC High Fmax ease timing closure Small area RV32I[M][C] A RV32E implementation is also possible Three variations: Simple native memory interface Wishbone master interface AXI-4 Lite master interface 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 9

Protium platform 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 10

Why RISC-V in protium Co-development: Full chain verification Software and hardware validation External hardware optional SoC usage: Versatile device to configure ASIC Fast reconfiguration (C compilation) No need to PNR the system Increase Protium interactivity First steps for future implementation of RISC-V in our designs: Smart sensor with fast auto-test and calibration capabilities Not for computing in first intention 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 11

Results Pulpissimo CPU is working Difficulties with modules due to complex SystemVerilog bus interfaces PicoRV32 First communication through UART Blackbox mode is ongoing 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 12

Conclusion RISC-V will come soon in particle physics designs Mainly not for computing power Most probable for supervision RISC-V landscape is large Easy to find something suitable for your needs Difficult to choose the best fitted We succeed to implement it in Protium Can enhanced the Protium platform First step before ASIC version 15/06/2023 frederic.morel@iphc.cnrs.fr - Journ es des M tiers de l'Electronique de l'IN2P3 et de l'IRFU 13