Evolution of Parallel Programming in Computing

Moores Law predicted the doubling of transistor capacity every two years, benefitting software developers initially. However, hardware advancements can no longer ensure consistent performance gains. Parallel computing, leveraging multicore architecture, has emerged as a solution to optimize performa

7 views • 10 slides

Secure System Architecture Progression Framework Overview

Explore the evolution of secure system architectures, including multicore analysis and components like Cell Broadband Engine, Intel Core i, Freescale P4080. Dive into centralized processing systems, memory management, and hardware evaluations for improved processing power and security measures.

0 views • 30 slides

Understanding Multicore Processors: Hardware and Software Perspectives

This chapter delves into the realm of multicore processors, shedding light on both hardware and software performance issues associated with these advanced computing systems. Readers will gain insights into the evolving landscape of multicore organization, spanning embedded systems to mainframes. The

1 views • 36 slides

SmartNIC Offloading for Distributed Applications

This presentation discusses offloading distributed applications onto SmartNICs using the iPipe framework. It explores the potential of programmable NICs to accelerate general distributed applications, characterizes multicore SmartNICs, and outlines the development and evaluation process. The study c

0 views • 31 slides

Trends in Computer Organization and Architecture

This content delves into various aspects of computer organization and architecture, covering topics such as multicore computers, alternative chip organization, Intel hardware trends, processor trends, power consumption projections, and performance effects of multiple cores. It also discusses the sca

5 views • 28 slides

Optimizing Word2Vec Performance on Multicore Systems

This research focuses on improving the efficiency of Word2Vec training on multi-core systems by enhancing floating point throughput, reducing overheads, and avoiding any accuracy loss. The study combines optimization techniques to achieve parallel performance and evaluates the accuracy of the result

0 views • 30 slides

Efficient Dynamic Memory Management for Embedded Multicore Systems

This content delves into the challenges of dynamic memory management in embedded multicore systems, emphasizing the importance of transaction-friendly approaches. It covers parallel data structures, the role of operating systems/libraries, and principles of memory allocation. Through illustrations a

0 views • 24 slides

Fast Multicore Key-Value Storage Study

Explore Cache Craftiness for Fast Multicore Key-Value Storage in a comprehensive study on building a high-performance KV store system. Learn about the feature wishlist, challenges with hard workloads, initial attempts with binary trees, and advancements with Masstree. Discover the contributions and

0 views • 38 slides

Understanding Cache Memory in Computer Systems

Explore the intricate world of cache memory in computer systems through detailed explanations of how it functions, its types, and its role in enhancing system performance. Delve into the nuances of associative memory, valid and dirty bits, as well as fully associative examples to grasp the complexit

0 views • 15 slides

A Model for Application Slowdown Estimation in On-Chip Networks

Problem of inter-application interference in on-chip networks in multicore processors due to NoC contention causes unfair slowdowns. The goal is to estimate NoC-level slowdowns in runtime and improve system fairness and performance. The approach includes NoC Application Slowdown Model (NAS) and Fair

0 views • 25 slides

A Software Memory Partition Approach for Eliminating Bank-level Interference in Multicore Systems

Memory requests from different threads can cause interferences in DRAM banks, impacting performance. The solution proposed involves partitioning DRAM banks between threads to eliminate interferences, leading to improved performance and energy savings.

0 views • 32 slides

Distributed Consensus and Coordination in Hardware Birds of a Feather Session

Specialists in distributed consensus and hardware coordination gathered at Middleware 18 for a session hosted by Zsolt István and Marko Vukoli. The session covered topics such as specialized hardware, programmable switches and NICs, P4 language for expressing forwarding rules, and deployment exampl

0 views • 33 slides

Understanding Multi-Processing in Computer Architecture

Beginning in the mid-2000s, a shift towards multi-processing emerged due to limitations in uniprocessor performance gains. This led to the development of multiprocessors like multicore systems, enabling enhanced performance through parallel processing. The taxonomy of Flynn categories, including SIS

0 views • 46 slides

Understanding Advanced Computer Architecture in Parallel Computing

Covering topics like Instruction-Set Architecture (ISA), 5-stage pipeline, and Pipelined instructions, this course delves into the intricacies of advanced computer architecture, with a focus on achieving high performance by optimizing data flow to execution units. The course provides insights into t

0 views • 12 slides

Supercomputing in Plain English: Multicore Madness Workshop Details

Prepare for the "Supercomputing in Plain English: Multicore Madness" workshop with important instructions such as muting yourself, downloading slides in advance, and accessing the session via Zoom or YouTube. The session, led by Henry Neeman from the University of Oklahoma, covers supercomputing top

0 views • 97 slides

Overview of Nested Data Parallelism in Haskell

The paper by Simon Peyton Jones, Manuel Chakravarty, Gabriele Keller, and Roman Leshchinskiy explores nested data parallelism in Haskell, focusing on harnessing multicore processors. It discusses the challenges of parallel programming, comparing sequential and parallel computational fabrics. The evo

0 views • 55 slides

Study of Garbage Collector Scalability on Multicores

This study delves into the scalability challenges faced by garbage collectors on multicore hardware. It highlights how the performance of garbage collection does not scale effectively with the increasing number of cores, leading to bottlenecks in applications. The shift from centralized to distribut

0 views • 23 slides

Memory Model Safety of Programs Research

Explore the challenges and vulnerabilities in memory models of programs, emphasizing the importance of maintaining strict locking discipline for performance-critical code. The research discusses issues with relaxed memory models on multicore machines and provides examples of memory model vulnerabili

0 views • 14 slides

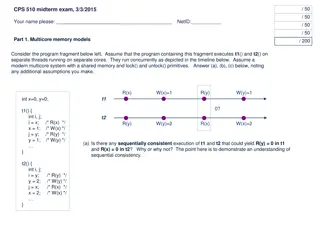

Multicore Memory Models and CPU Protection in Operating Systems

This content covers topics related to multicore memory models, synchronization, CPU protection levels in Dune-enabled Linux systems, and concurrency control in multithreaded programs. The material includes scenarios, questions, and diagrams to test understanding of these concepts in the context of t

0 views • 10 slides

Software Design Considerations for Multicore CPUs

Discussion on performance issues with modern multi-core CPUs, focusing on higher-end chips and boards. Exploring the concept of cores, chips, and boards in the context of multicore CPUs and their memory architectures.

0 views • 31 slides

Understanding KeyStone Multicore Navigator for Efficient Data Transport

This lesson provides insights into the KeyStone Multicore Navigator, explaining its advantages, architecture, functional components like descriptors and queues, and how to configure it for optimal performance. It covers the motivation behind its design, basic elements such as descriptors and queues,

0 views • 55 slides

Cooperative Cache Scrubbing for Efficient Memory Management in Multicore Systems

Cooperative Cache Scrubbing optimizes memory management in multicore systems by efficiently handling short-lived application objects and reducing unnecessary data writes to memory. By communicating semantic information to hardware caches, dead lines are scrubbed, dirty bits unset, and unnecessary fe

0 views • 40 slides